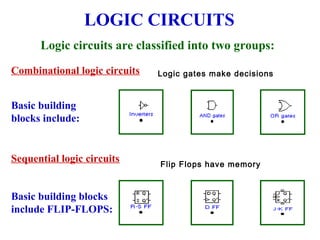

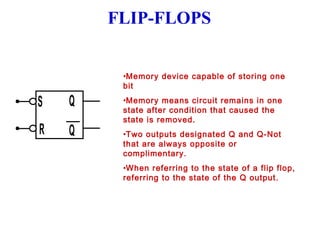

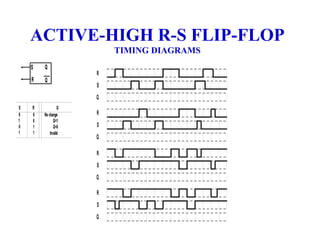

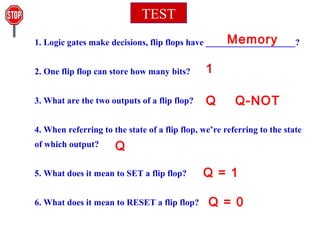

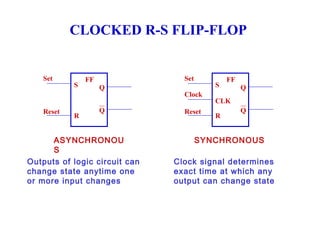

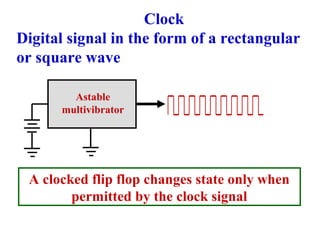

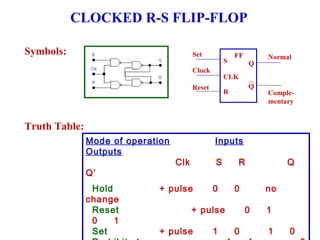

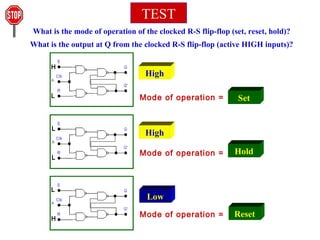

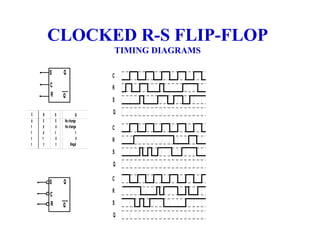

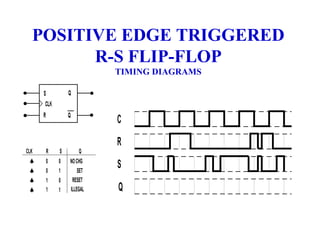

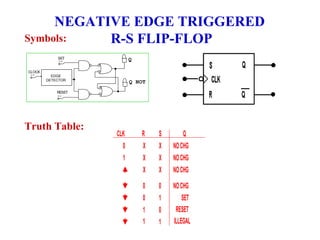

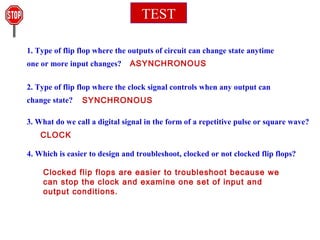

The document discusses different types of flip-flops including RS NAND and NOR flip-flops, and covers the basics of sequential logic circuits. It defines level-triggered and edge-triggered clock inputs for flip-flops and compares asynchronous and synchronous clocked flip-flops. The timing diagrams show how positive and negative edge triggering determines when the output of a flip-flop changes state in response to clock pulses and input signals.