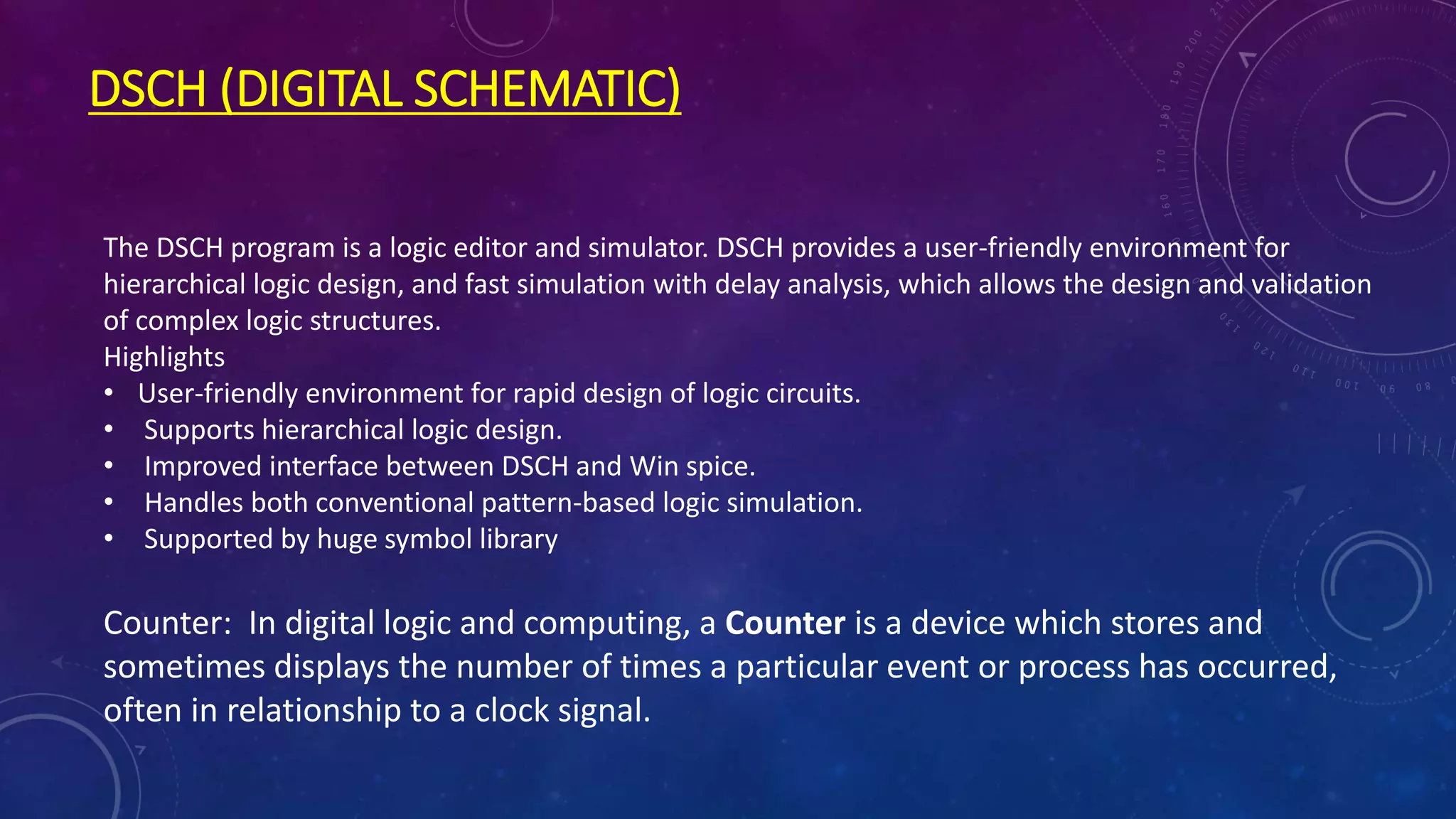

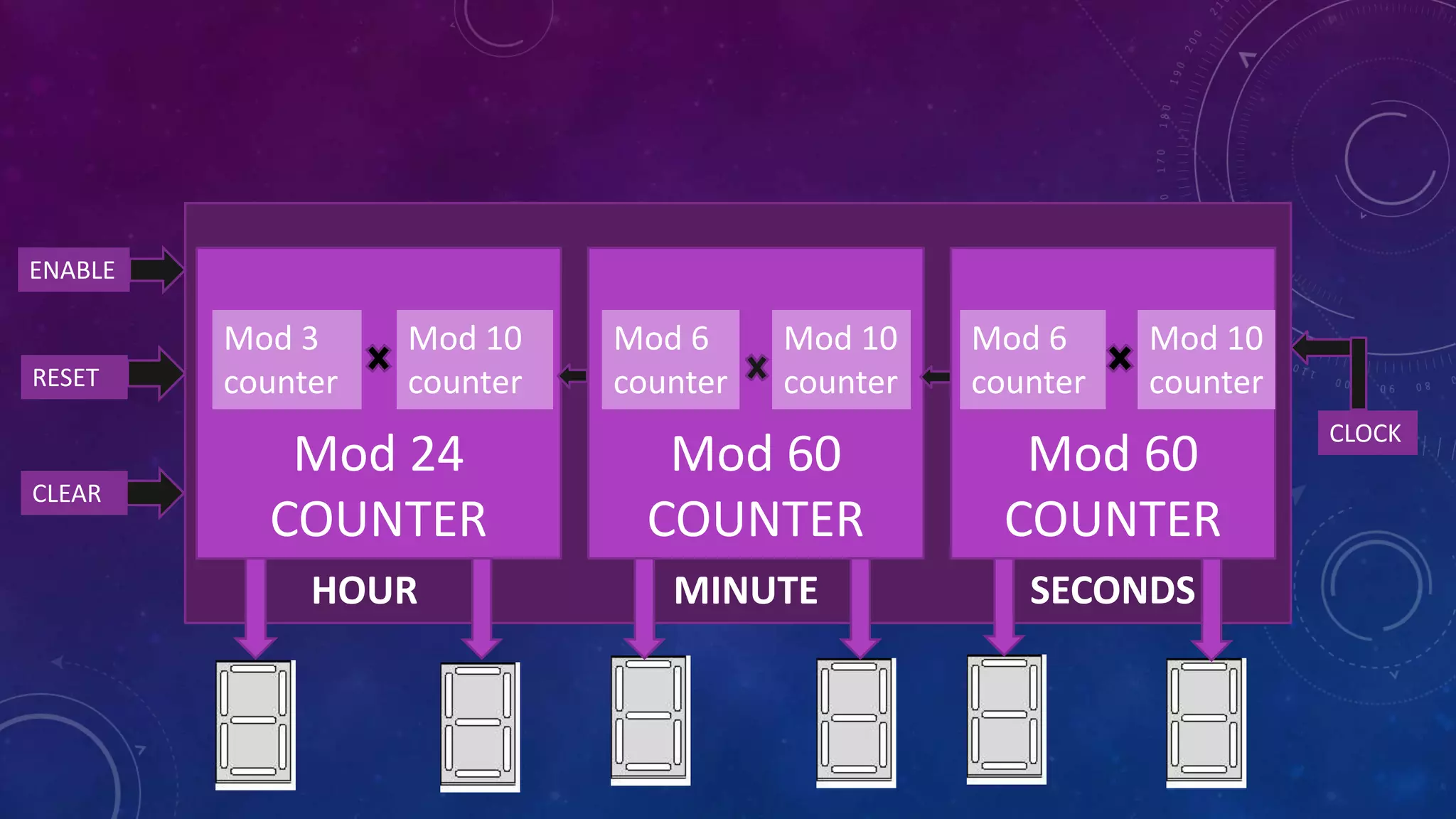

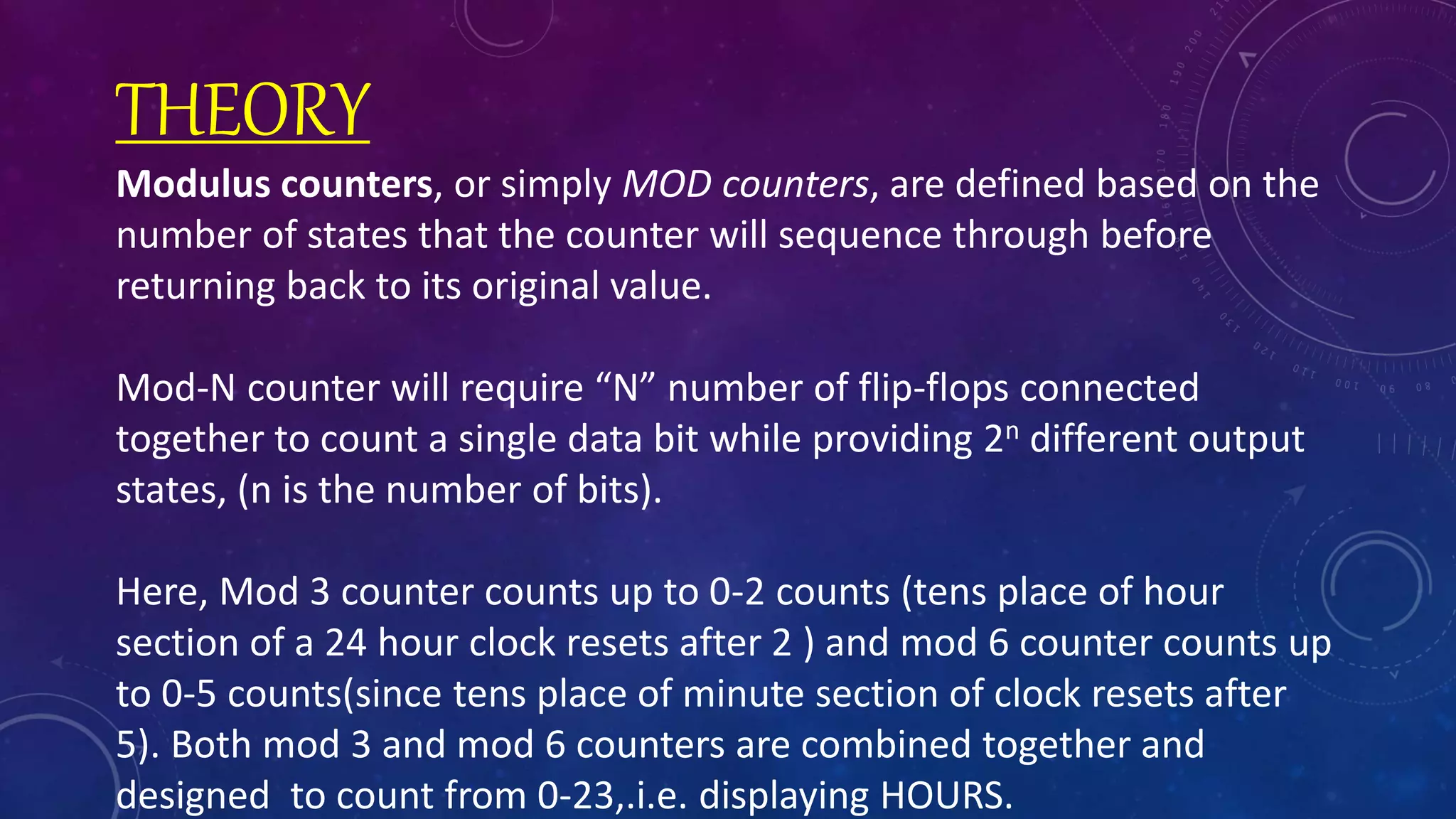

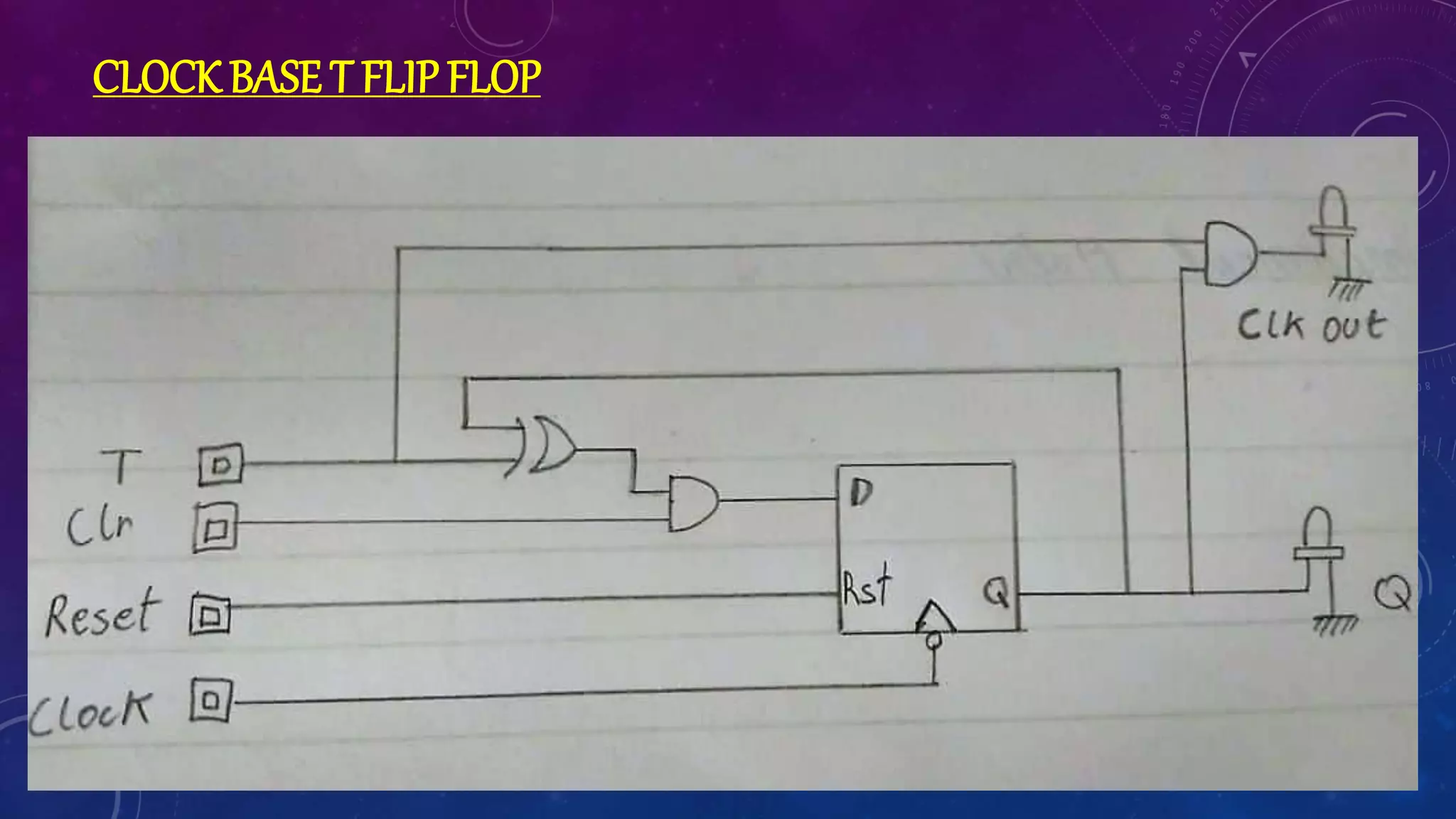

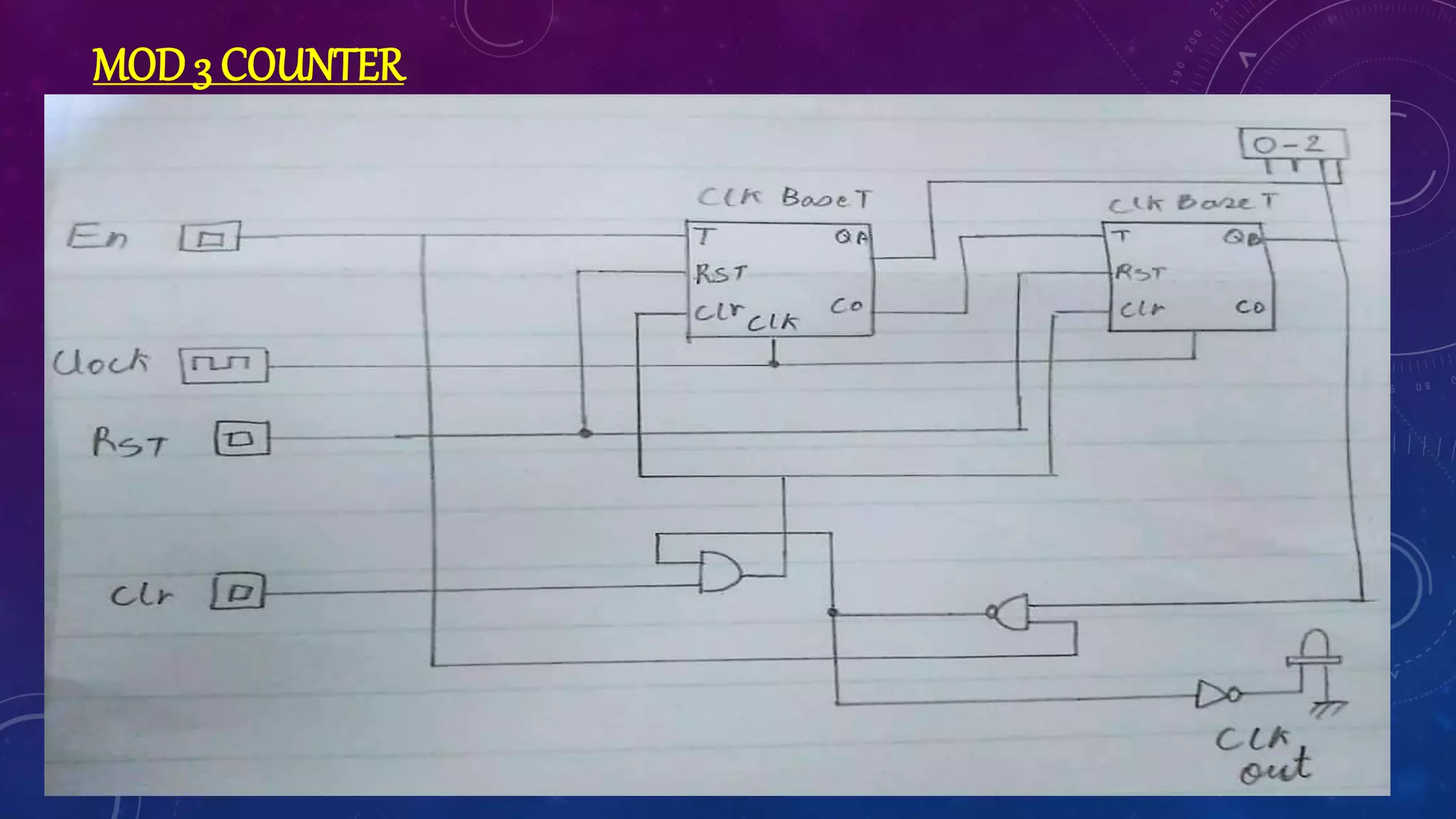

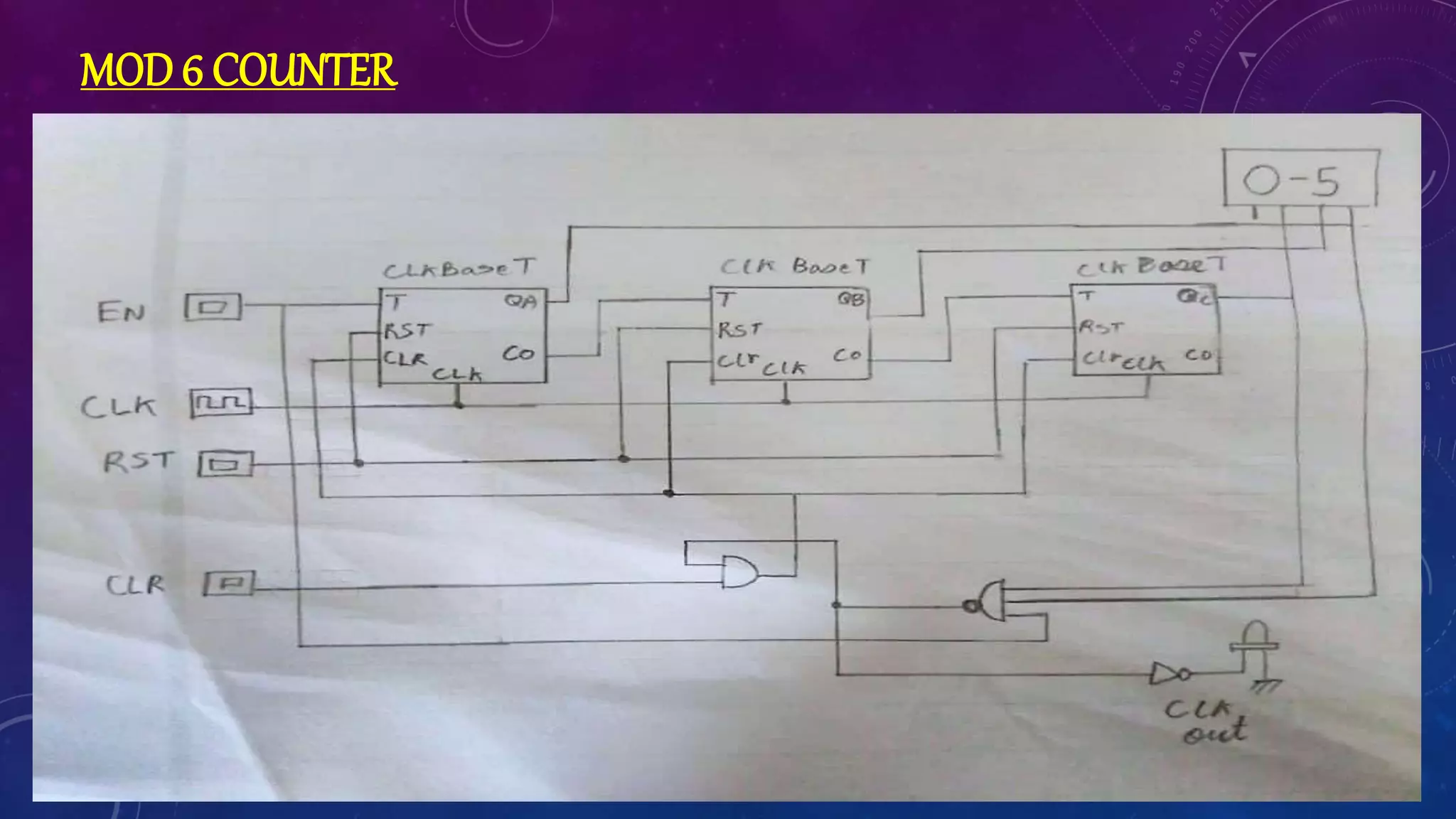

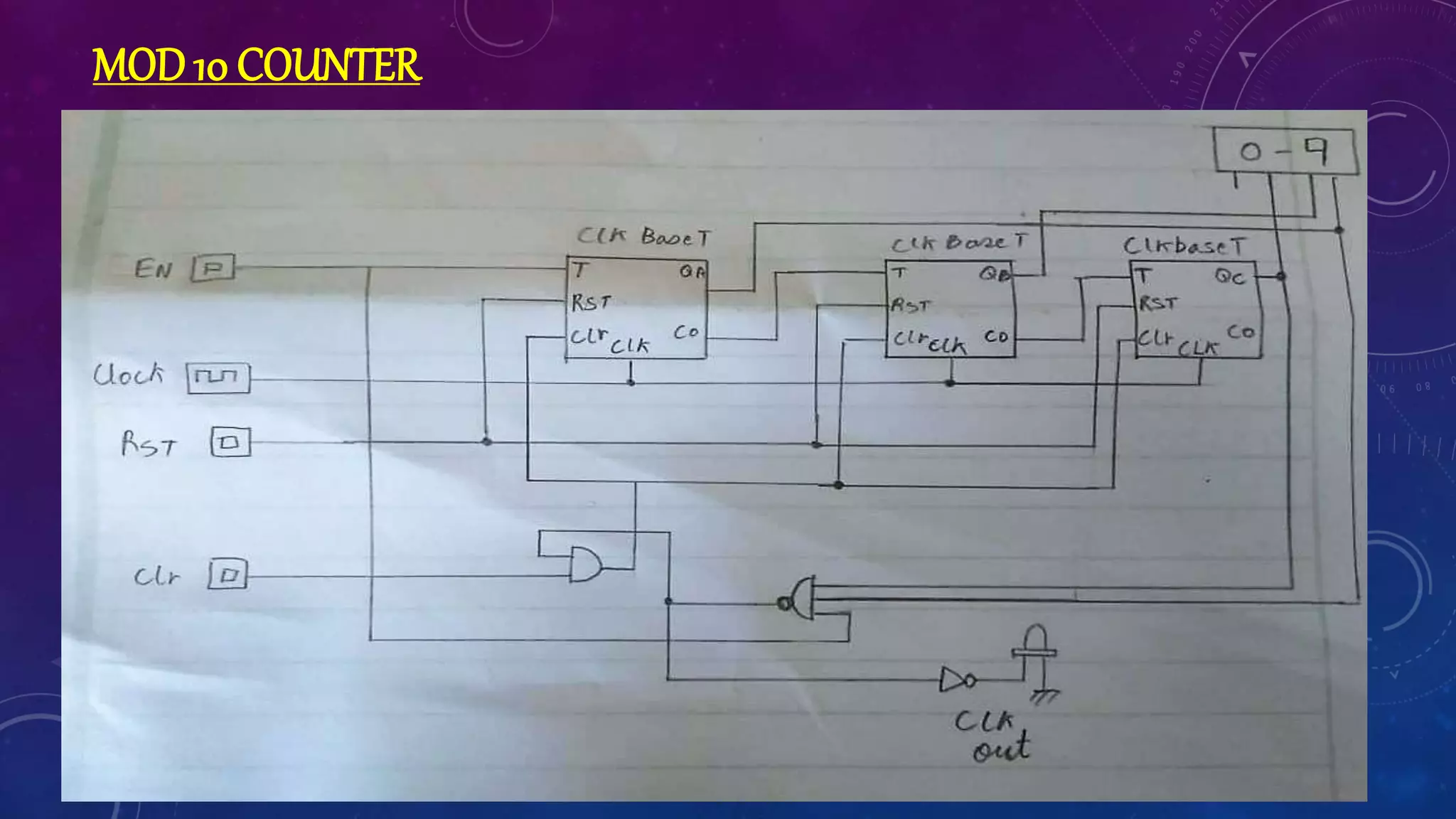

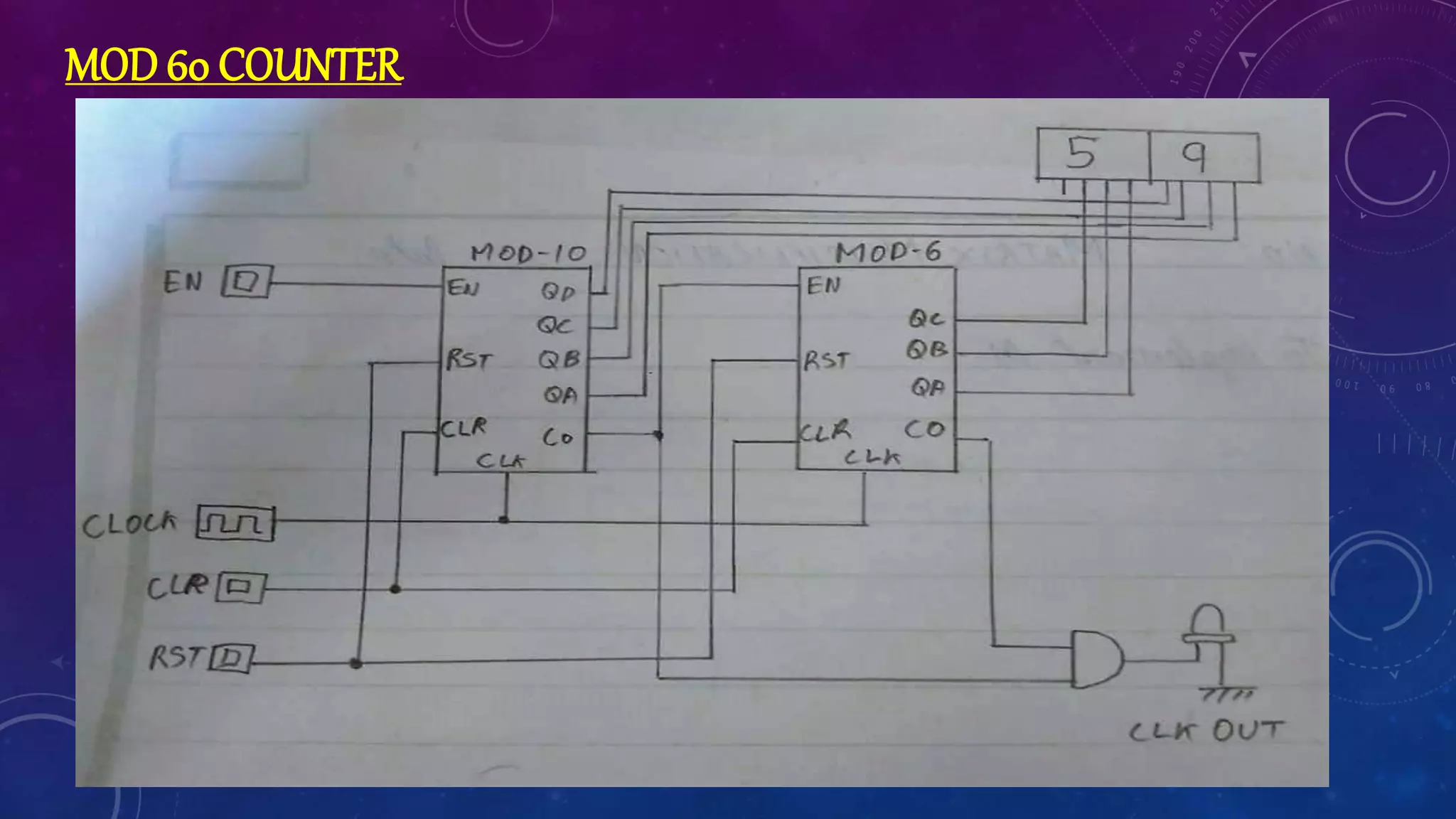

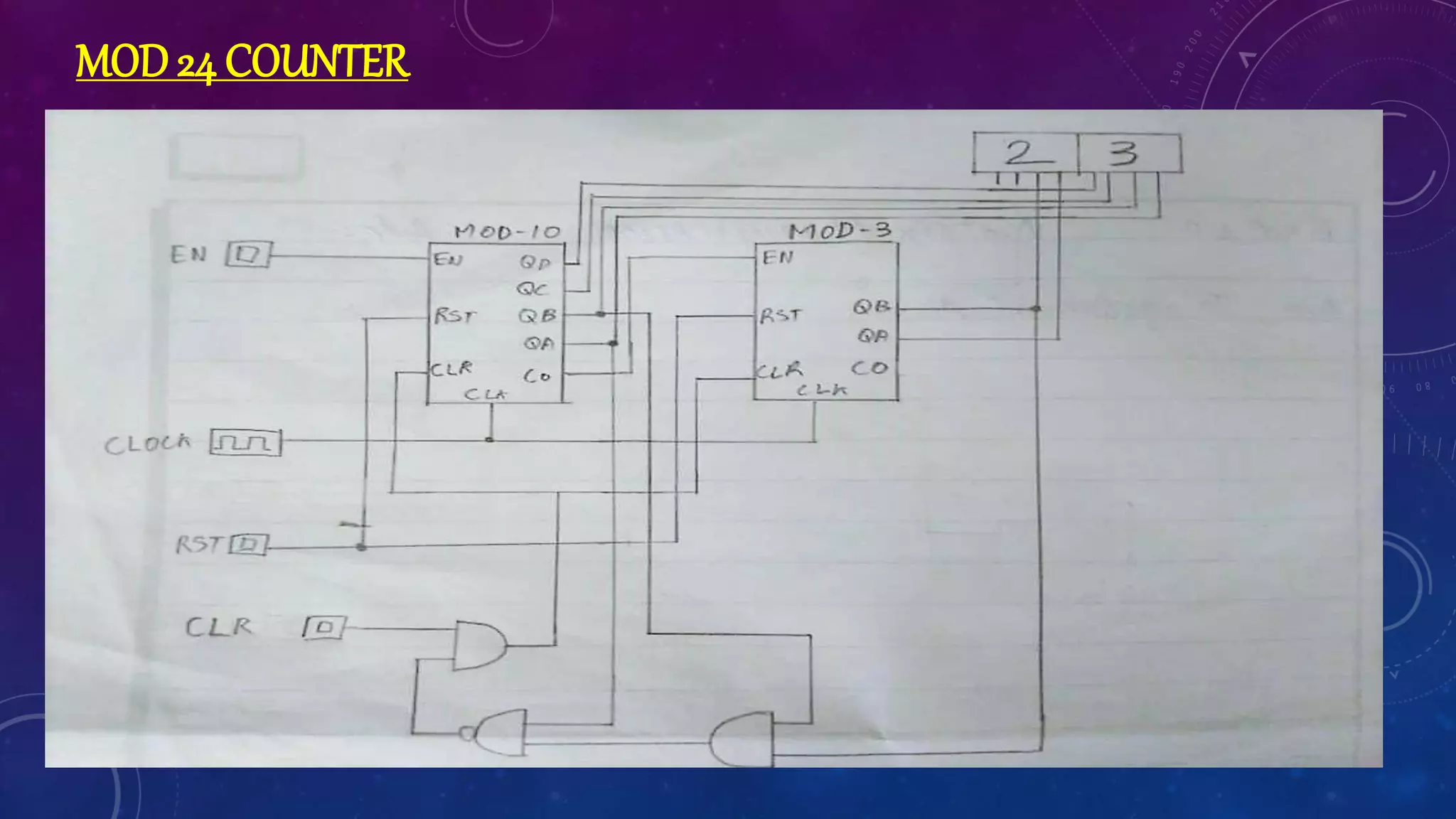

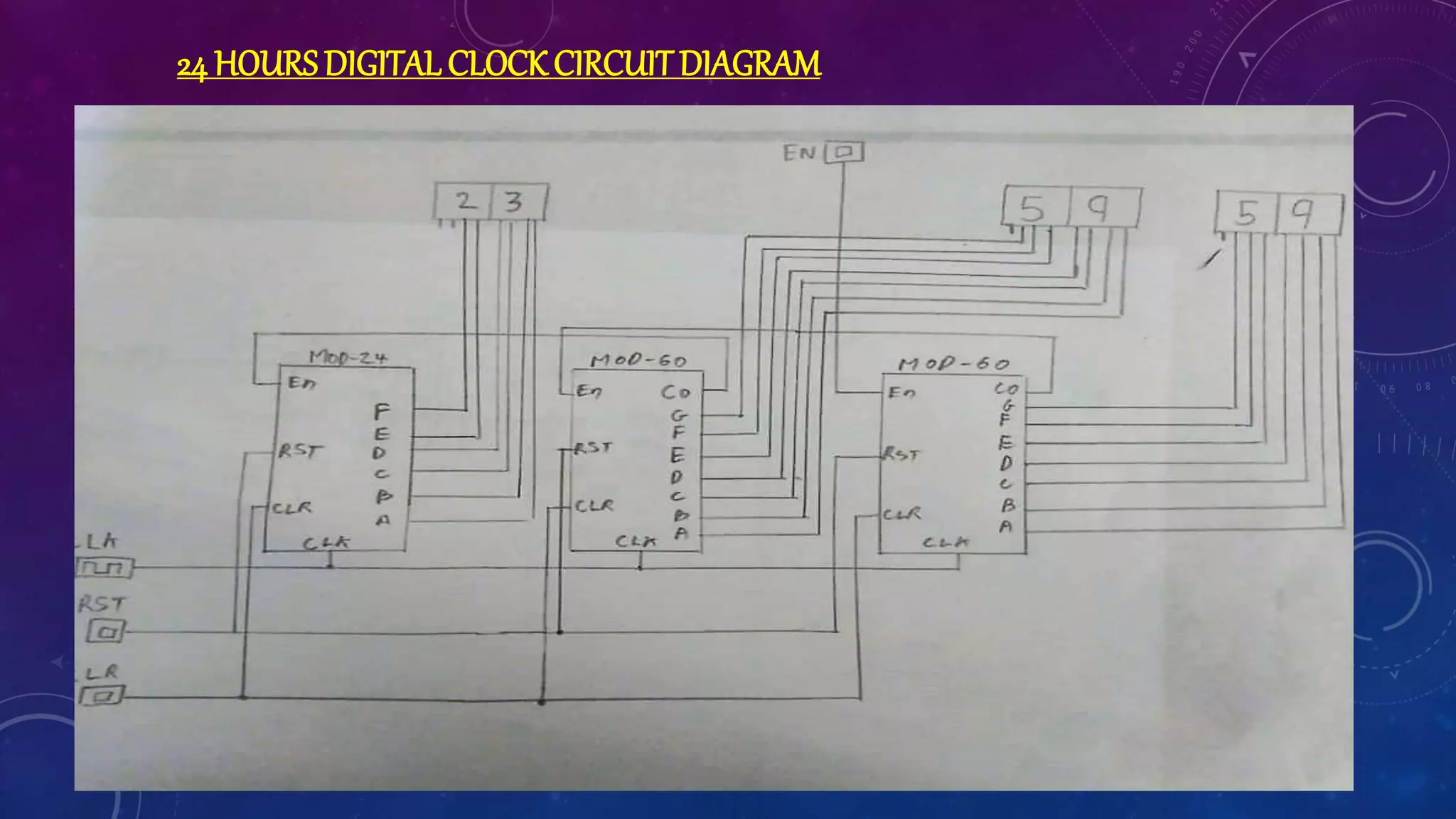

The document details the design and implementation of counters for a digital clock using the DSCH program, which allows for hierarchical logic design and simulation. It explains various modulus counters (mod 3, mod 6, mod 10, mod 24, and mod 60) that track time by counting seconds, minutes, and hours, organized through flip-flops and logic gates. The integration of these counters into a comprehensive digital clock circuit that resets automatically after reaching their limits is also described.