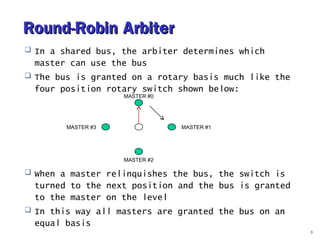

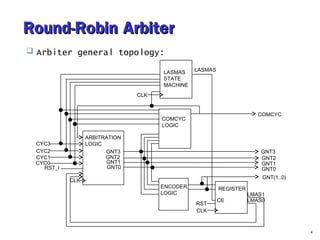

The document describes a round-robin arbiter module that determines which master can use a shared bus. It uses a rotating priority scheme to grant access to each master in turn. The arbiter logic includes request detection, priority encoding, state tracking to grant the next master, and arbitration logic to assert the appropriate grant lines. Verification is done through testing and simulation of sample waveforms.

![RRoouunndd--RRoobbiinn AArrbbiitteerr

Bus requests arrive at inputs [ CYC0] to [CYC3]

If bus is free, one of the 4 grant lines ([GNT0] to

[GNT1]) is asserted which corresponds to the

request signals

5](https://image.slidesharecdn.com/wishbonetutorials-141019181439-conversion-gate01/85/Wishbone-tutorials-5-320.jpg)

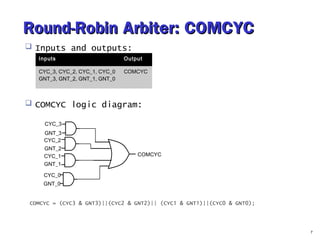

![Round-RRoobbiinn AArrbbiitteerr:: CCOOMMCCYYCC

The [COMCYC] indicates whether the bus is free or

busy

It is asserted whenever a master has both requested

the bus and has been granted the bus by the arbiter

6](https://image.slidesharecdn.com/wishbonetutorials-141019181439-conversion-gate01/85/Wishbone-tutorials-6-320.jpg)

![Round-Robin AArrbbiitteerr:: EEnnccooddeerr LLooggiicc

Grant line [GNT0] to [GNT3] are encoded as

[GNT(1..0)]

This is used with the [COMCYC] signal to indicate

which master has been granted the bus

When [COMCYC] is asserted, the master located on

[GNT(1..0)] is granted the bus

8](https://image.slidesharecdn.com/wishbonetutorials-141019181439-conversion-gate01/85/Wishbone-tutorials-8-320.jpg)

![Round-Robin AArrbbiitteerr:: EEnnccooddeerr LLooggiicc

Inputs and outputs:

Encoder logic diagram:

9

Inputs Outputs

GNT_3, GNT_2, GNT_1, GNT_0 GNT[1], GNT[0]

GNT_3

GNT_1

GNT[1] = GNT_2 || GNT_3

GNT[0] = GNT3 || GNT1

GNT_2

0

0

0

0

0

GNT_3 GNT_2 GNT_1 GNT_0 GNT[1] GNT[0]

0 0 0 1 0 0

0 0 1 0 0 1

0 1 0 0 1 0

1 0 0 0 1 1](https://image.slidesharecdn.com/wishbonetutorials-141019181439-conversion-gate01/85/Wishbone-tutorials-9-320.jpg)

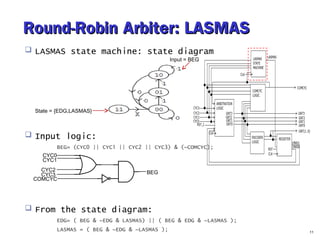

![Round-RRoobbiinn AArrbbiitteerr:: LLAASSMMAASS

Round-robin arbiters keep track of the level of the

previous master

The level is saved in a register that latches the

state of grant signals [GNT(1..0)]

The register latches the grant signal when

indicated by the LASMAS state machine

10

CE](https://image.slidesharecdn.com/wishbonetutorials-141019181439-conversion-gate01/85/Wishbone-tutorials-10-320.jpg)