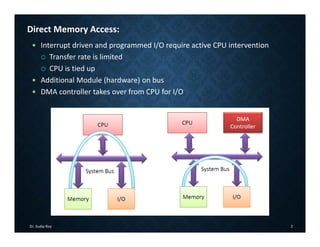

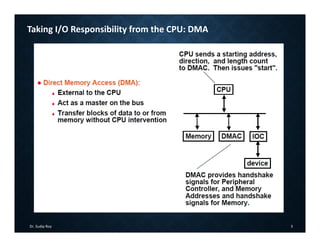

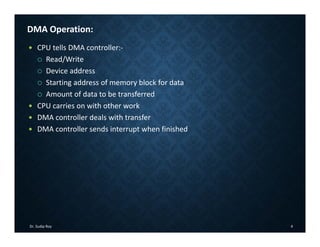

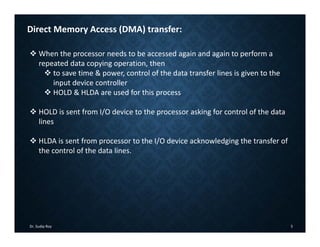

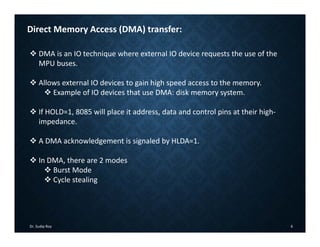

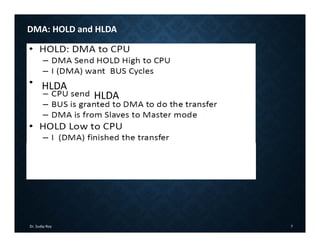

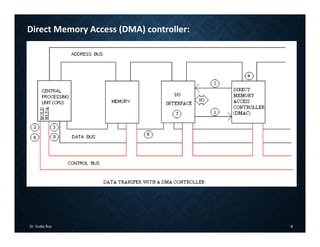

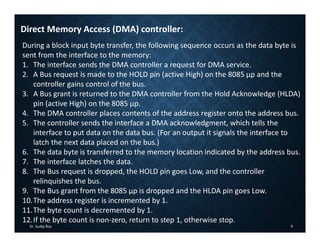

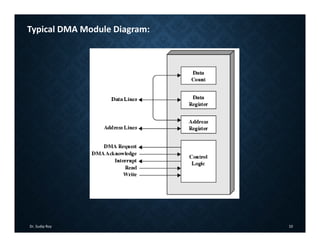

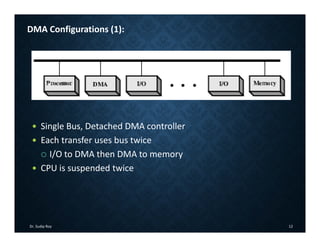

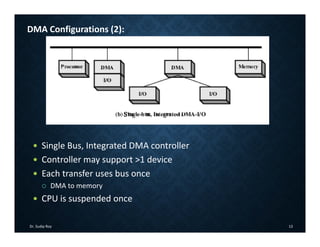

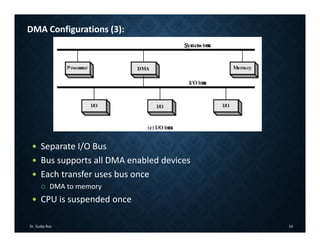

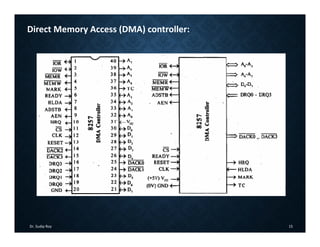

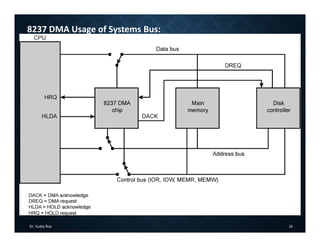

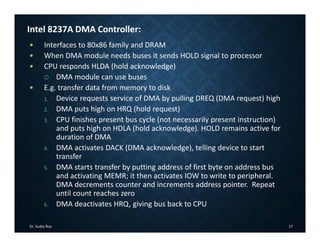

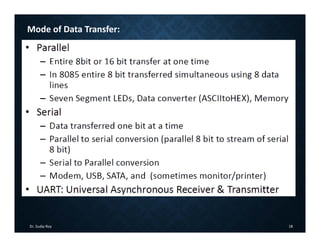

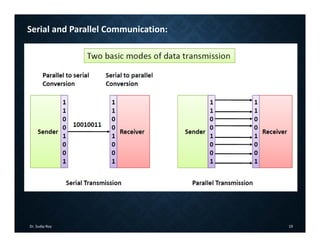

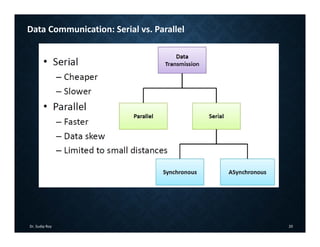

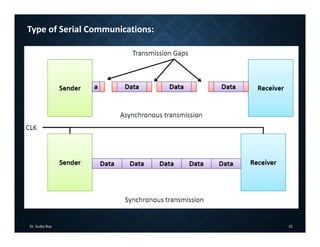

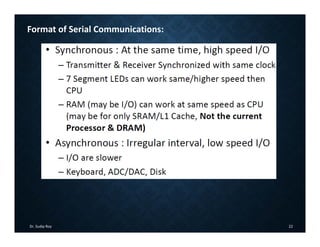

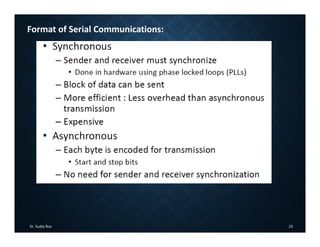

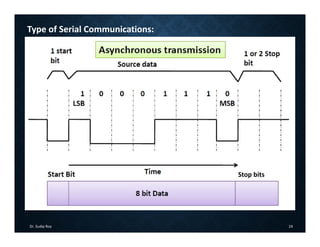

The document discusses Direct Memory Access (DMA) in computer architecture, detailing how it allows I/O devices to transfer data directly to memory without continuous CPU involvement. It explains the operation of the DMA controller, including the sequences of control signals and data transfer processes. The document also outlines different DMA configurations and communication types, emphasizing efficiencies in data transfer compared to traditional methods.