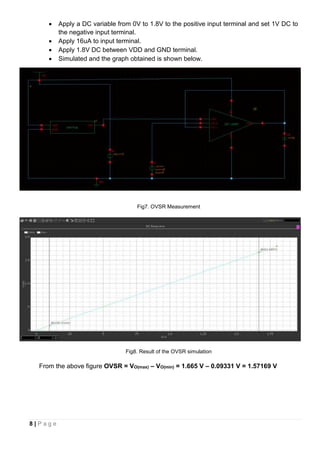

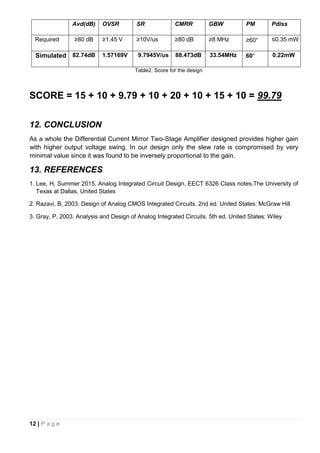

The document describes the design of a differential input, single-ended output two-stage operational amplifier. A current mirror topology is used to meet the design specifications, including a differential voltage gain of at least 80 dB, output voltage swing range of at least 1.45 V, slew rate of at least 10 V/μs, and power dissipation of less than 0.35 mW. The design approach, schematic, analysis of DC operating points, AC performance, and output voltage swing are presented. Simulation results show the amplifier meets all specifications except for a slightly reduced slew rate of 9.79 V/μs.