Embed presentation

Download to read offline

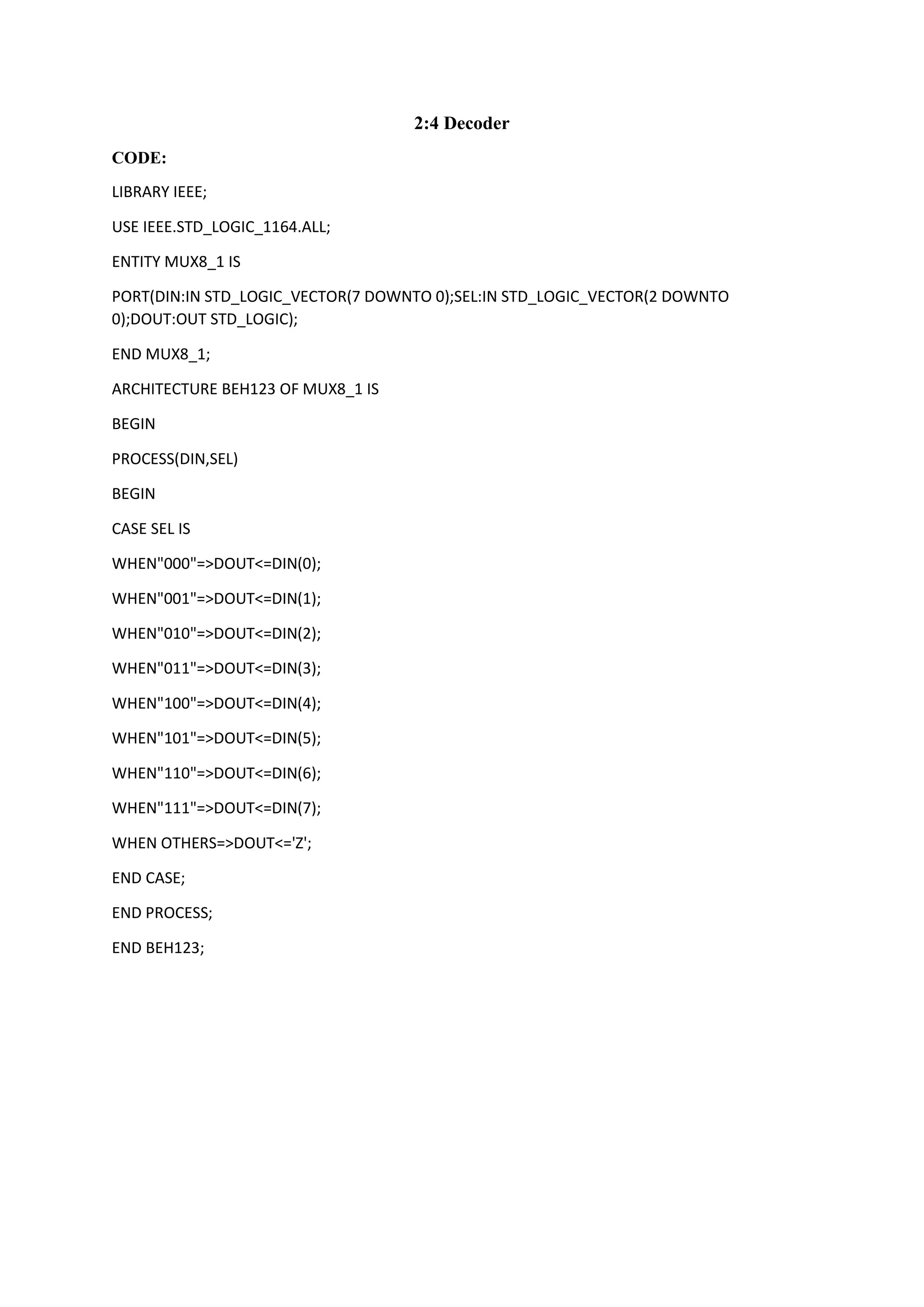

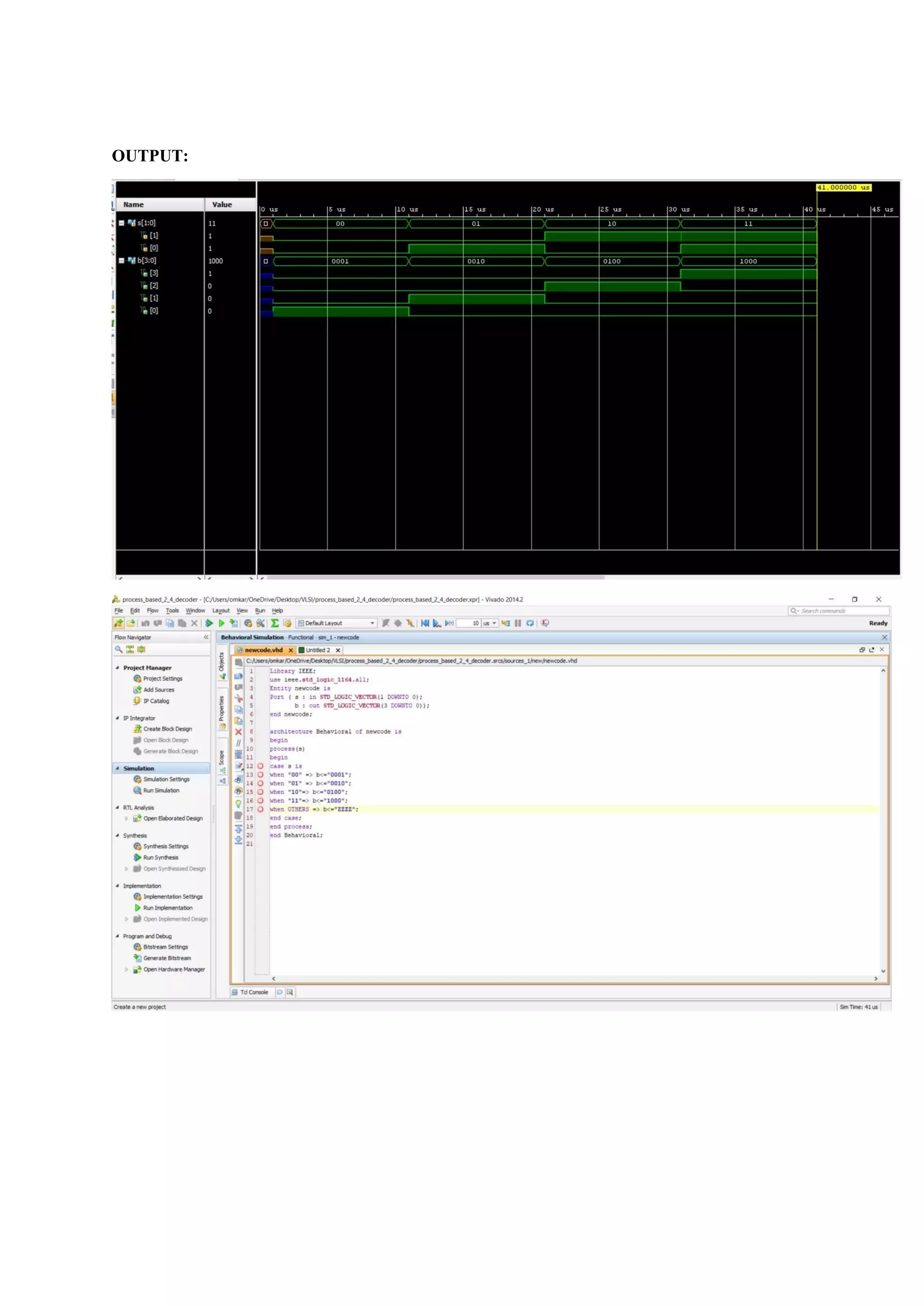

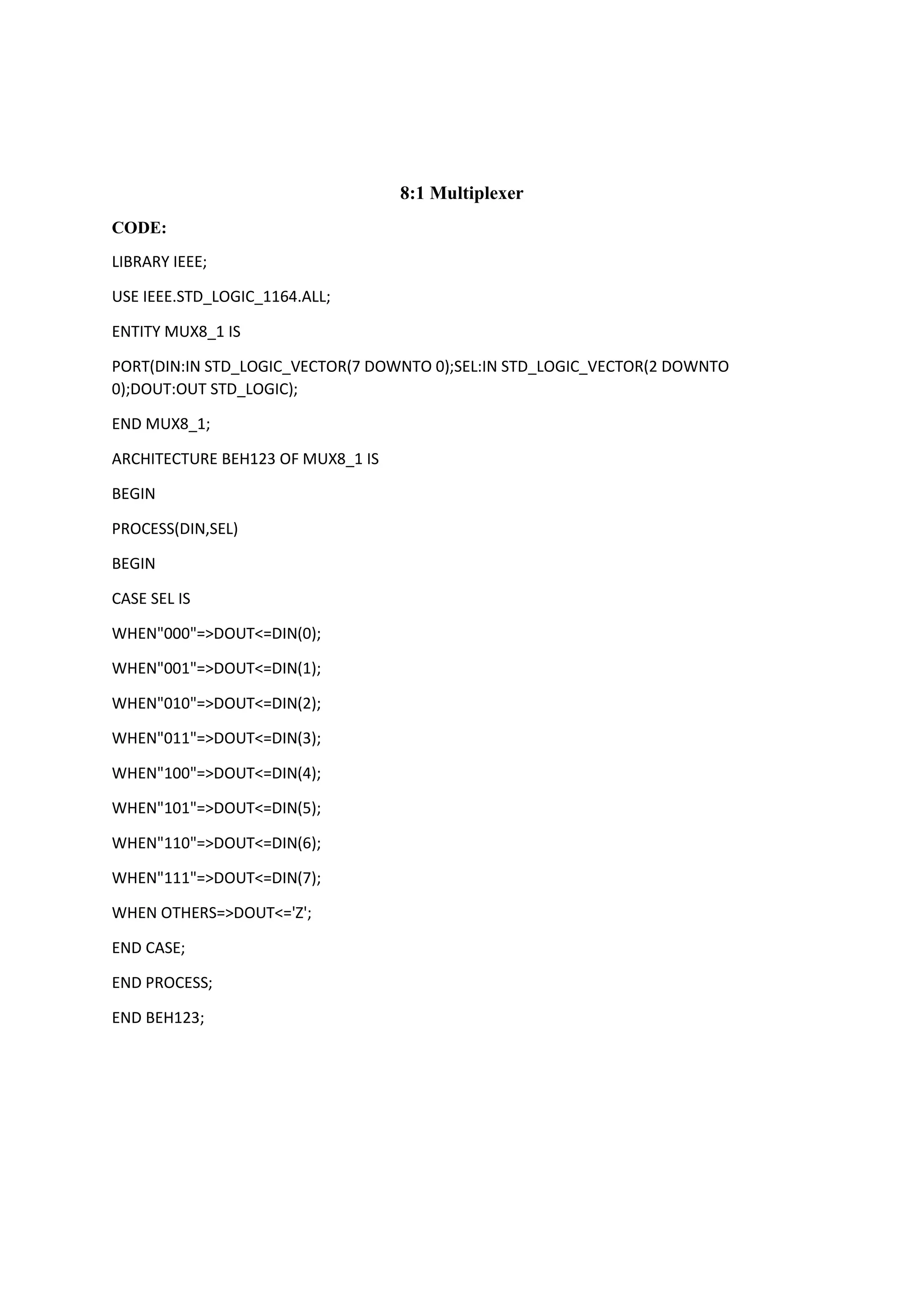

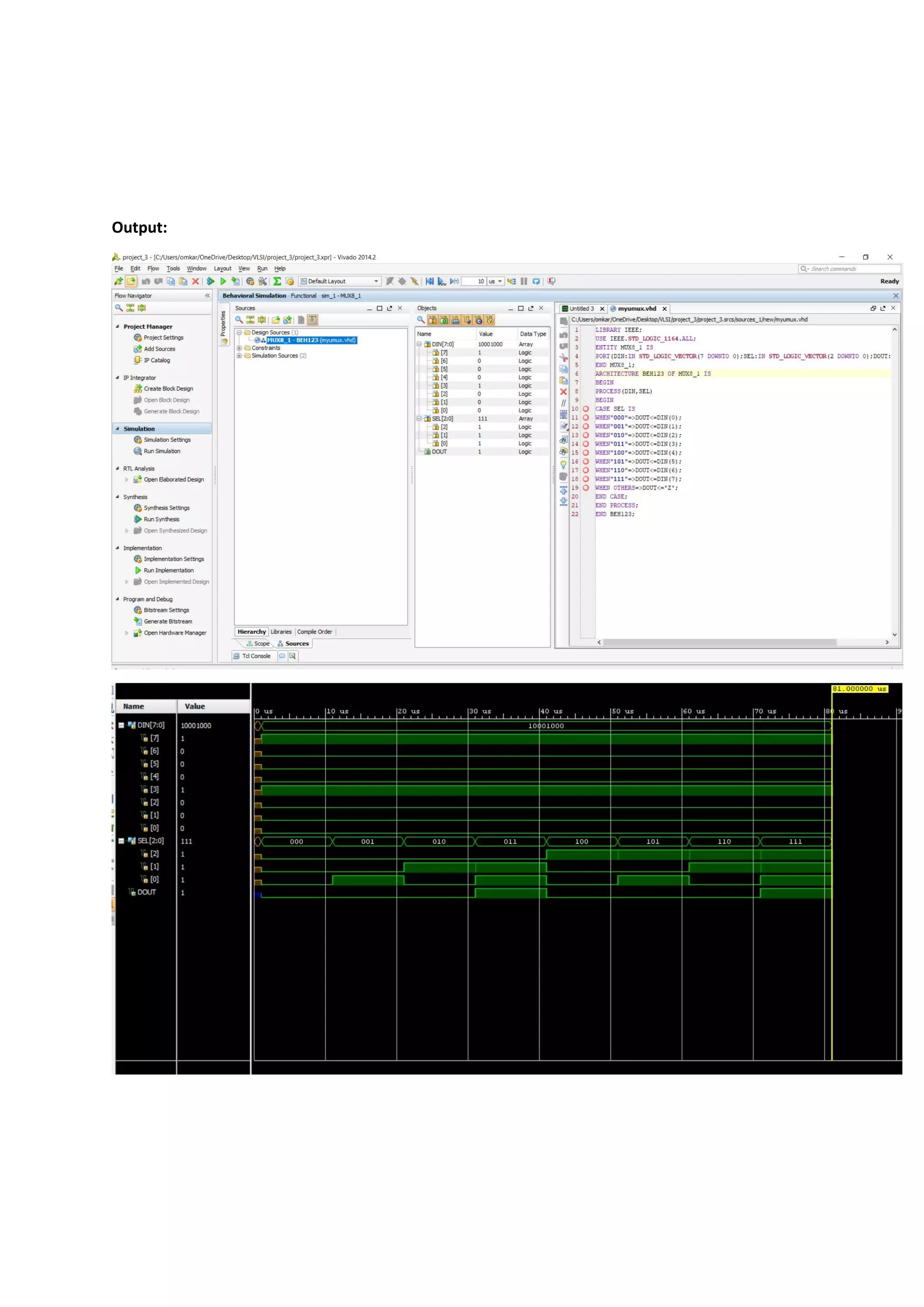

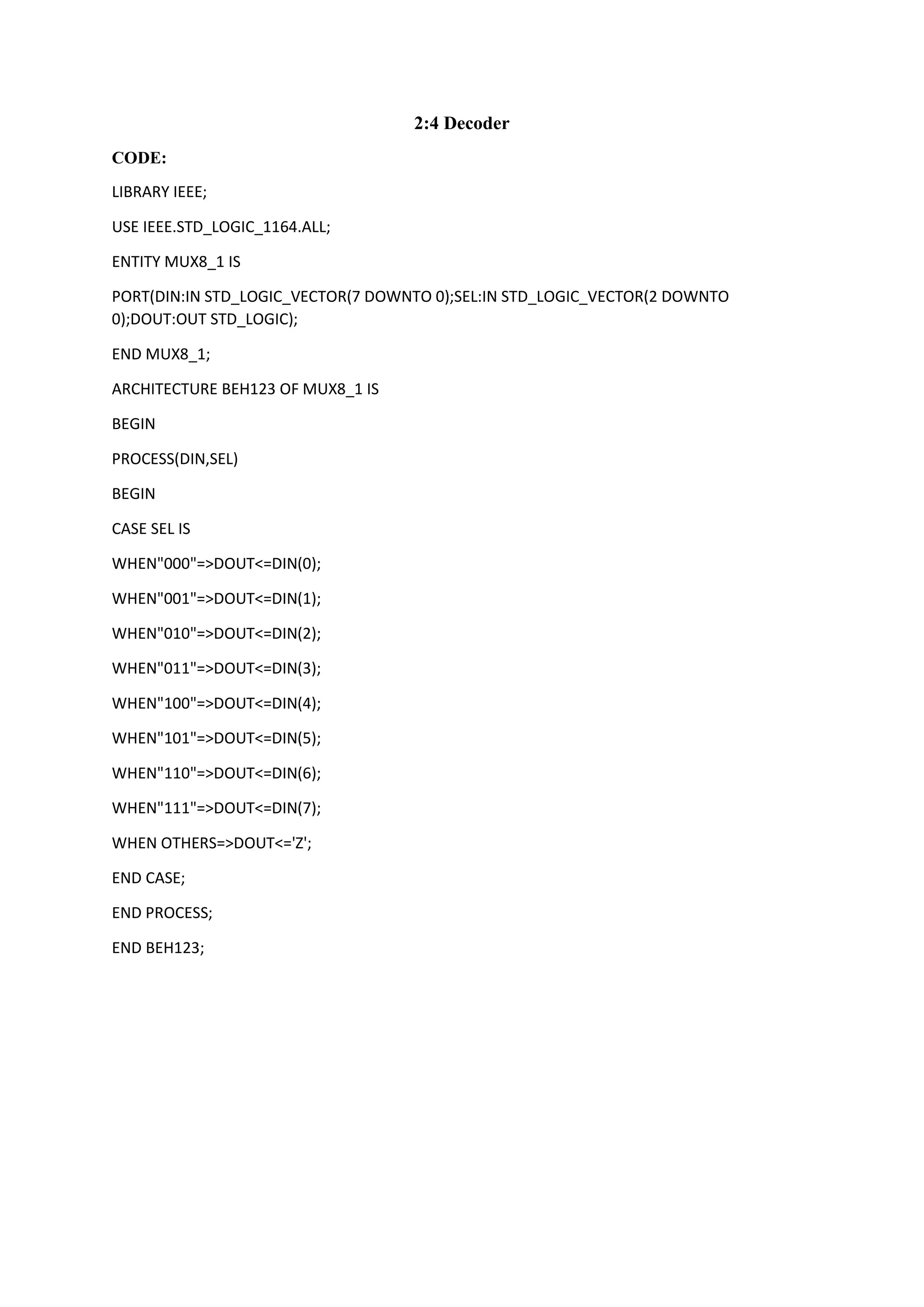

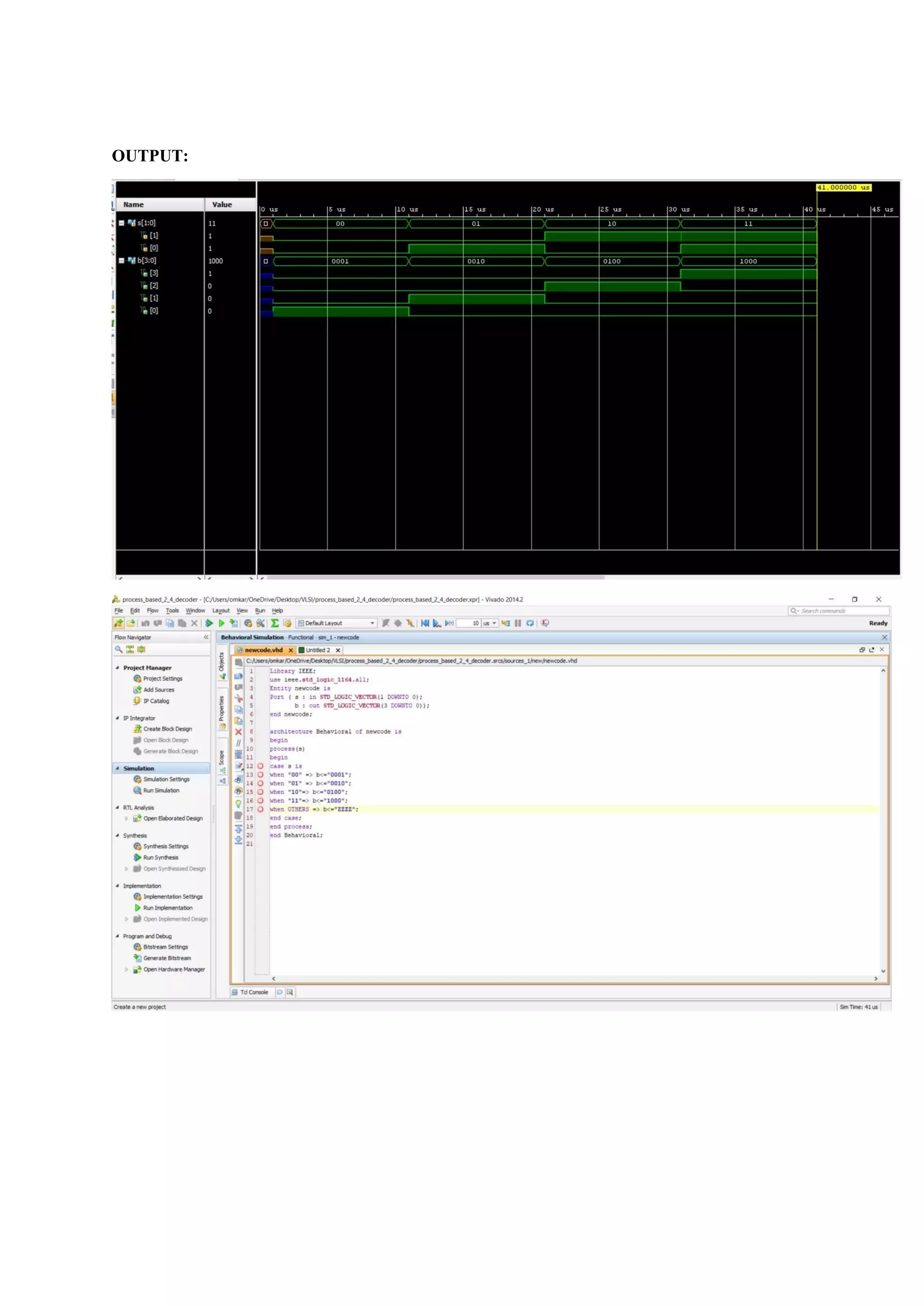

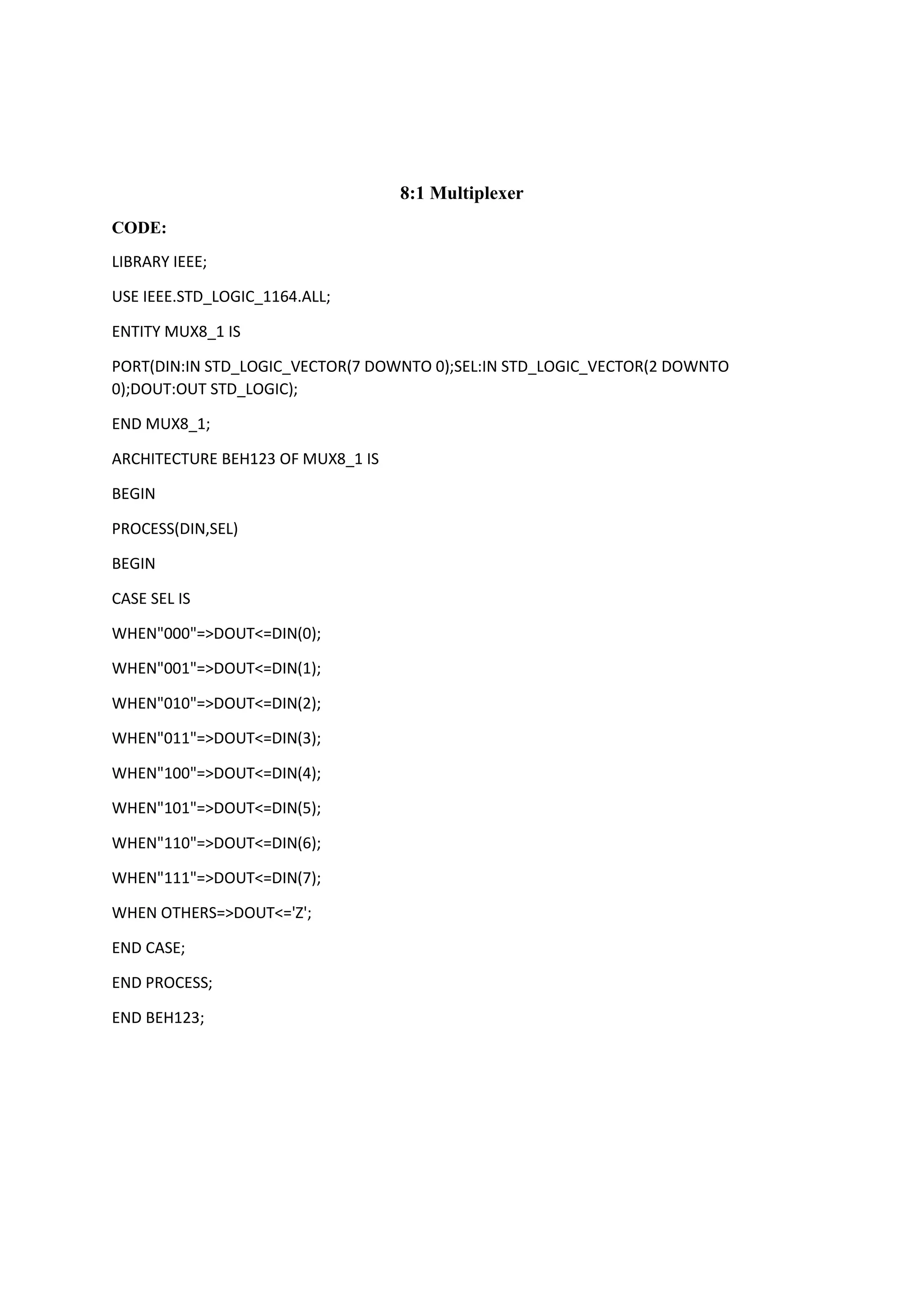

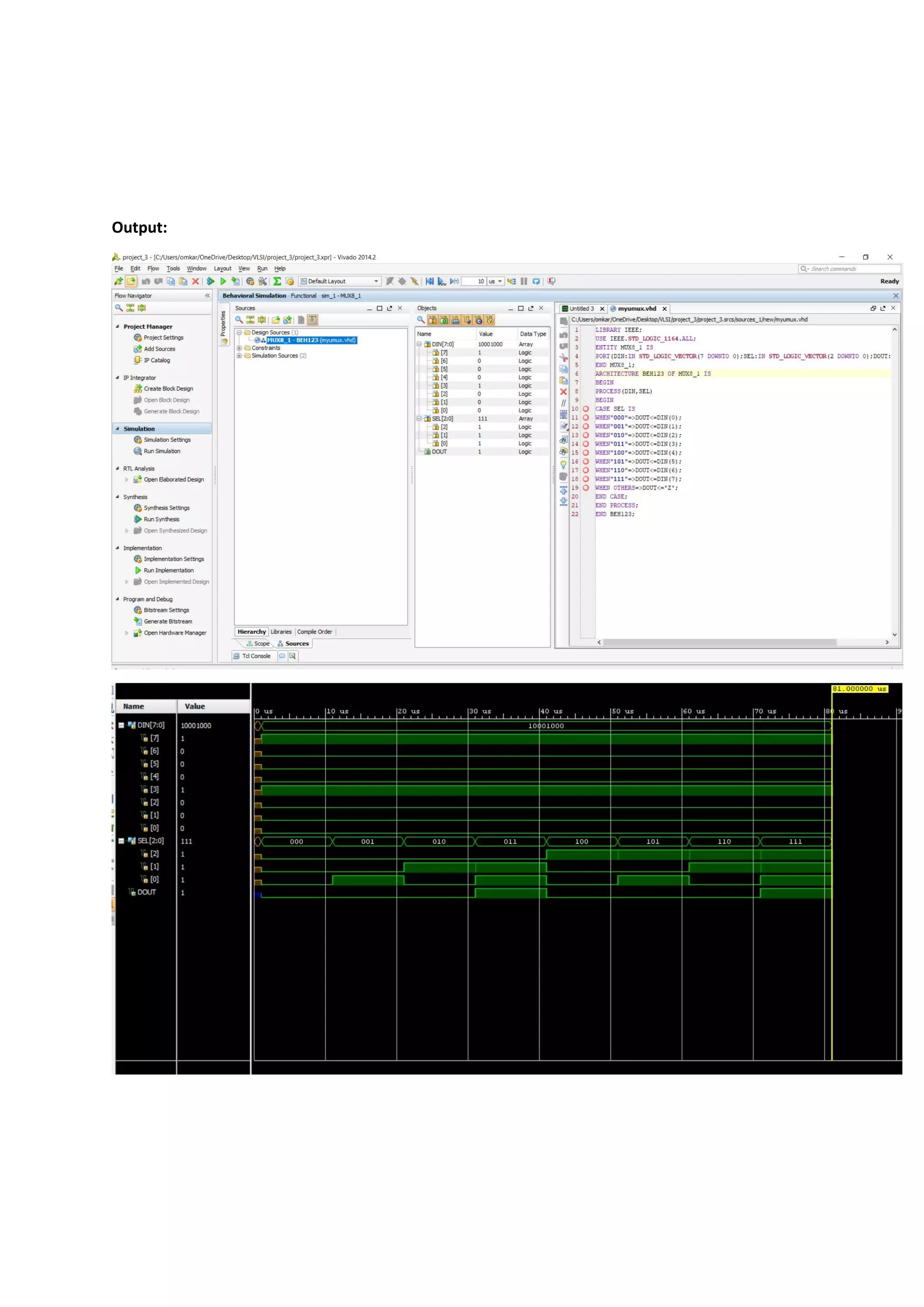

The document describes a VHDL code for an 8-to-1 multiplexer. The multiplexer has 8 inputs, 3 select lines, and 1 output. The VHDL code uses a case statement to select the appropriate input pin to connect to the output pin based on the value on the select lines.