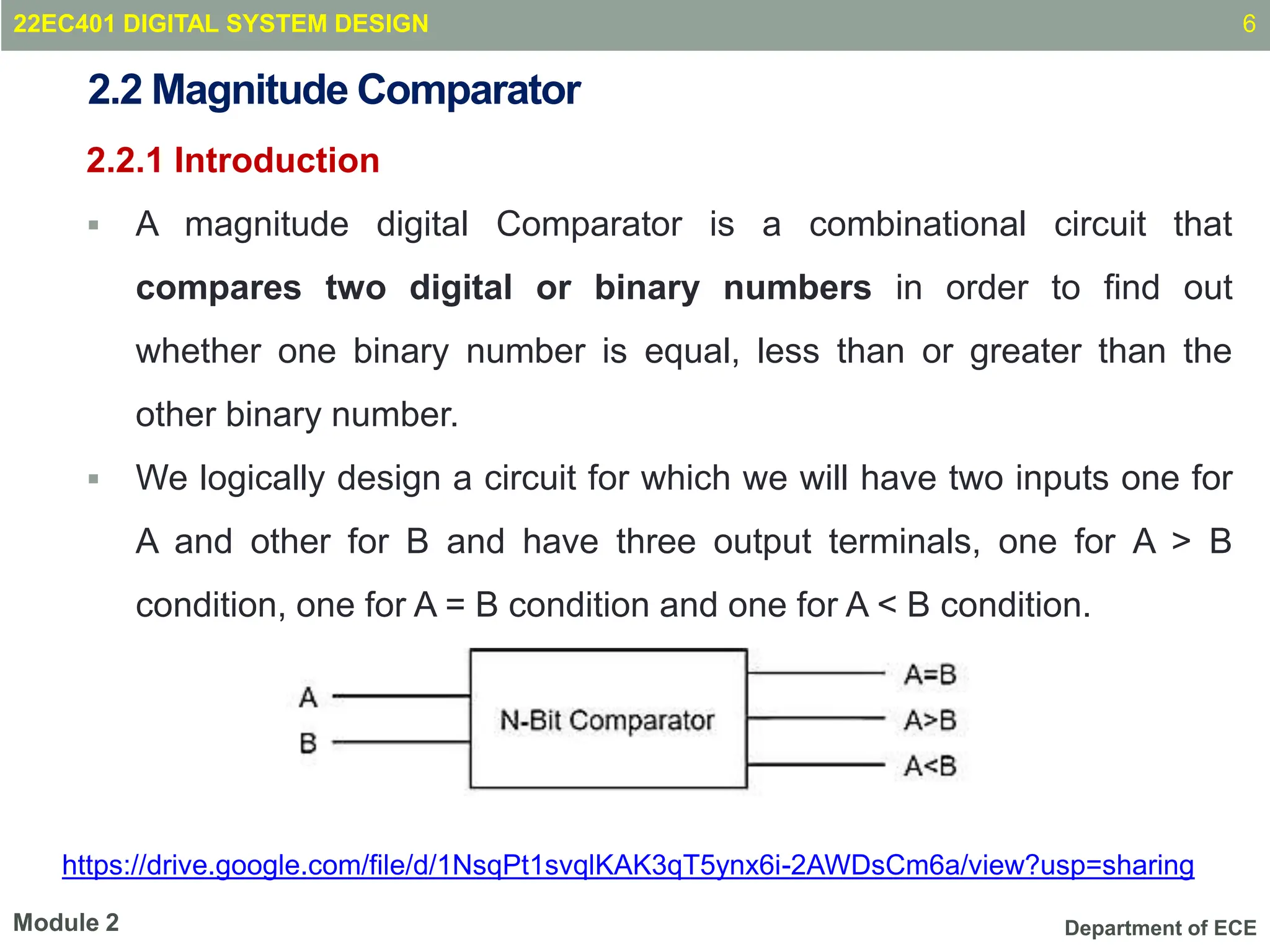

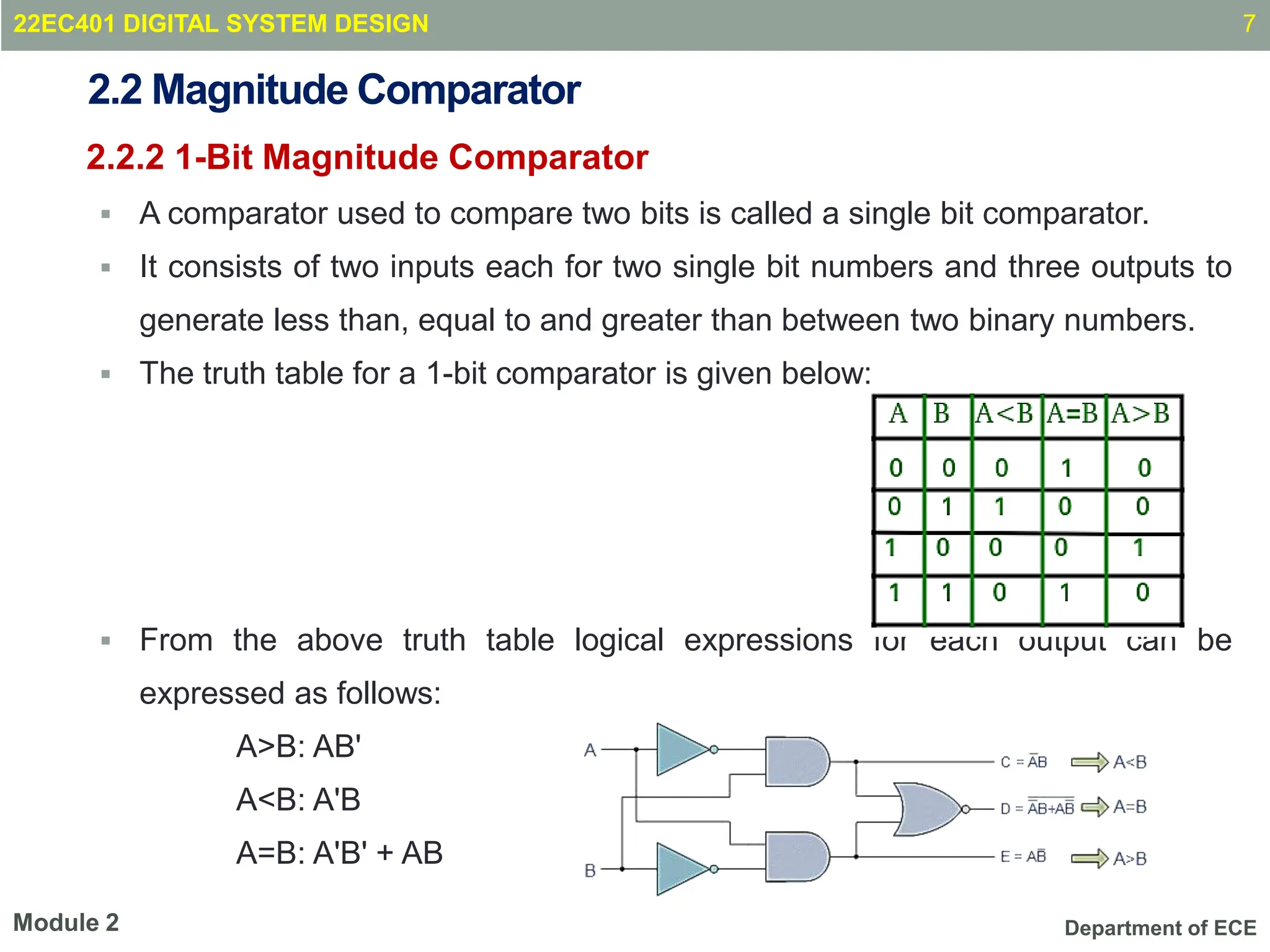

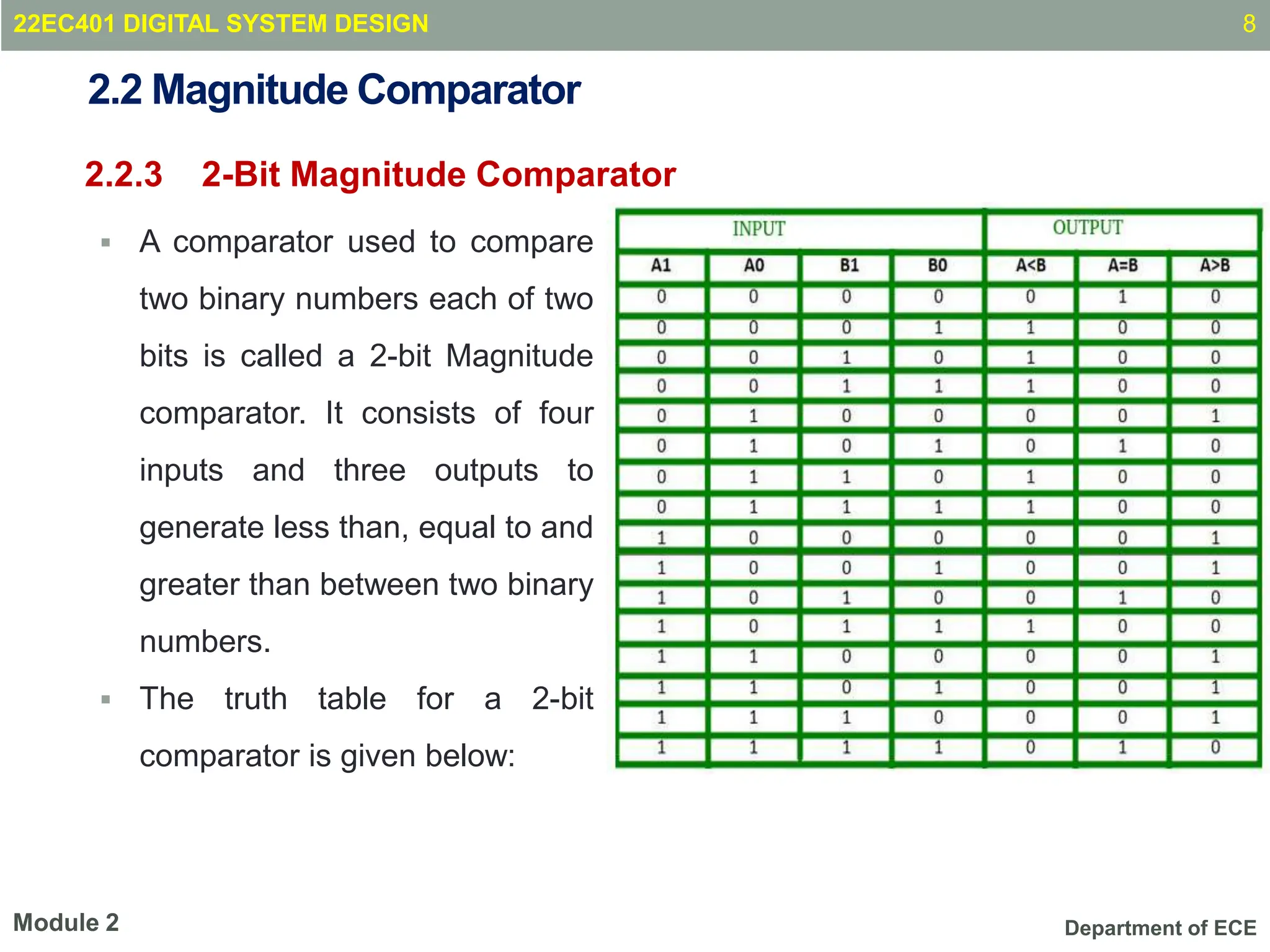

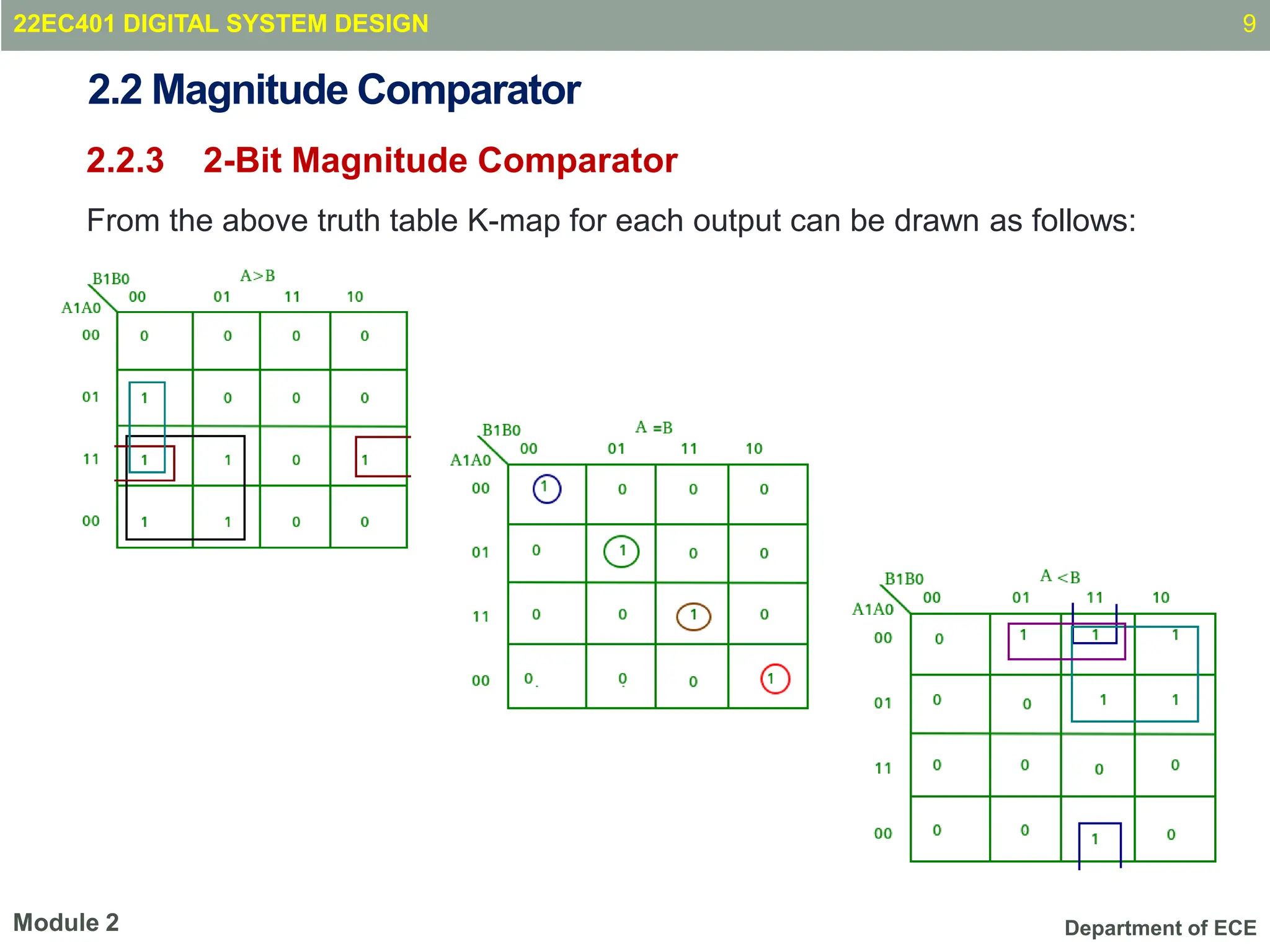

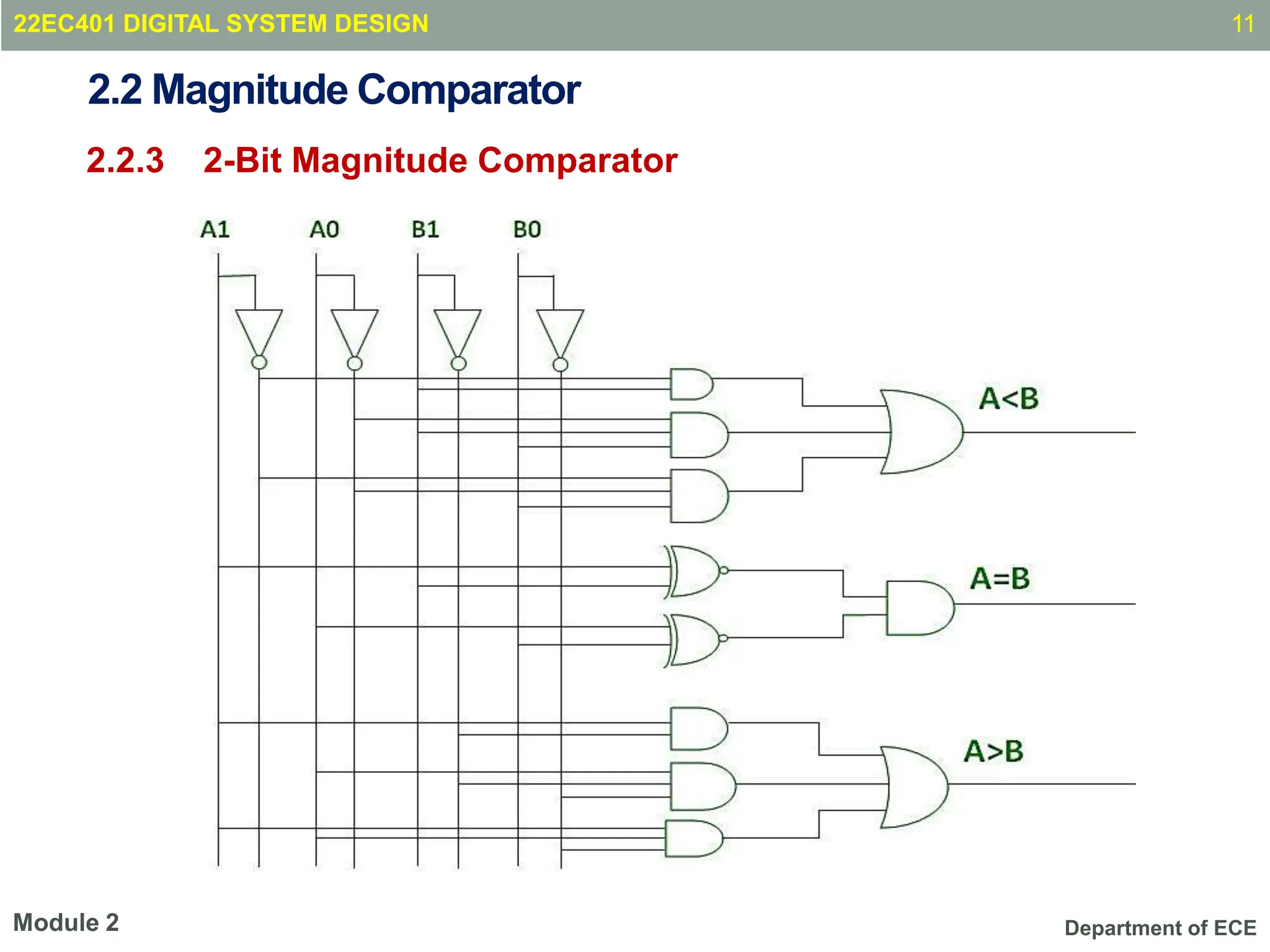

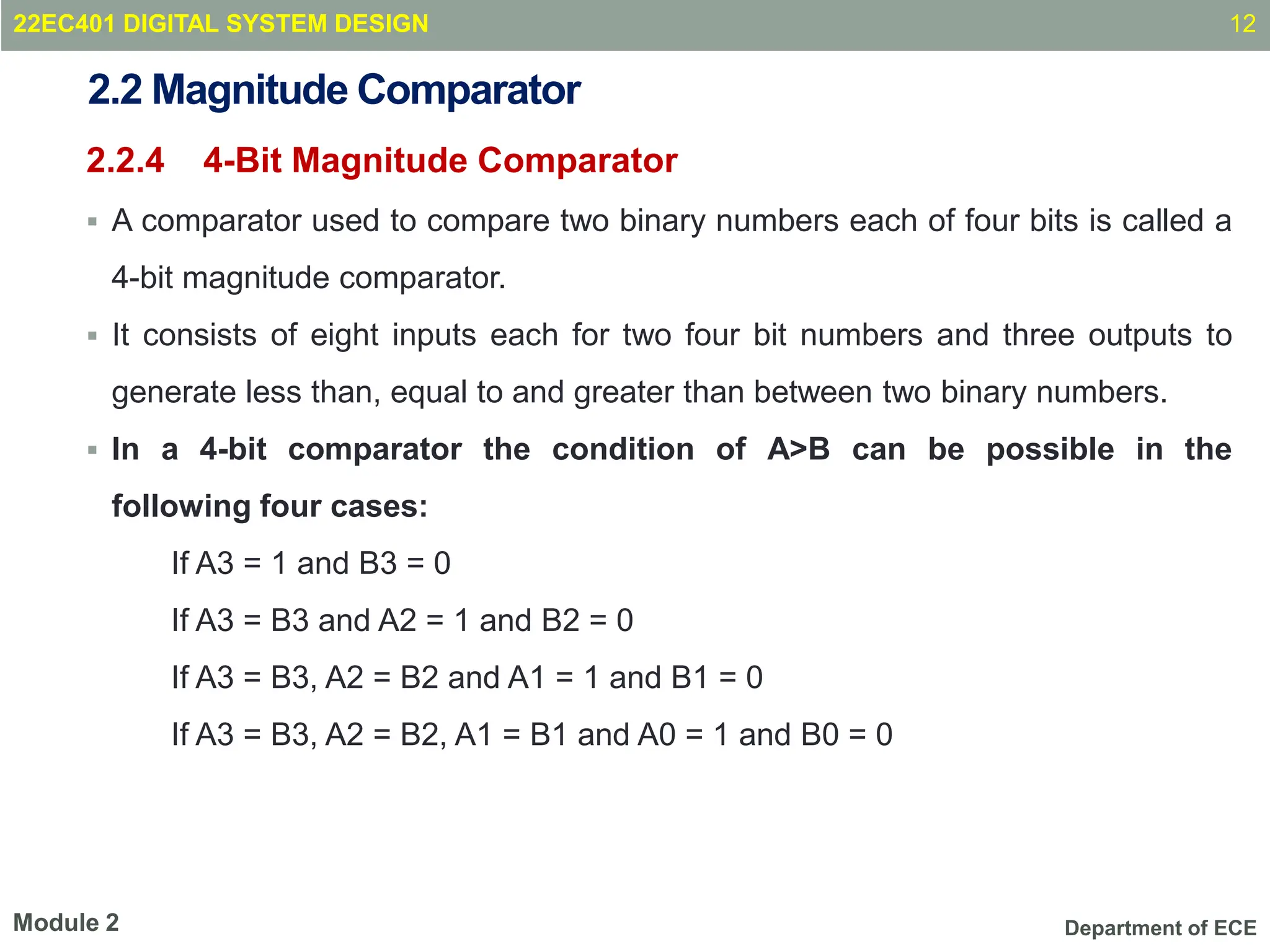

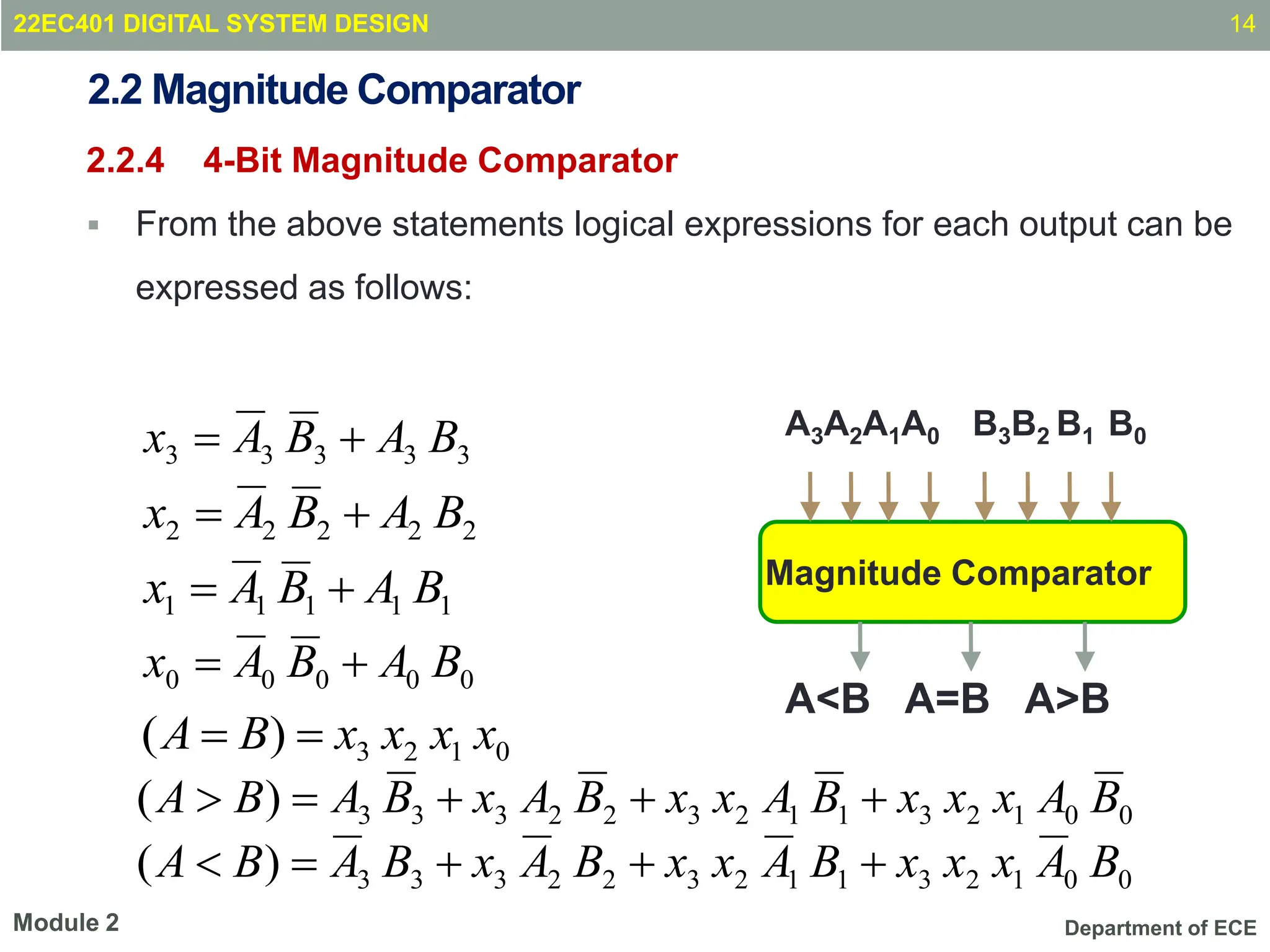

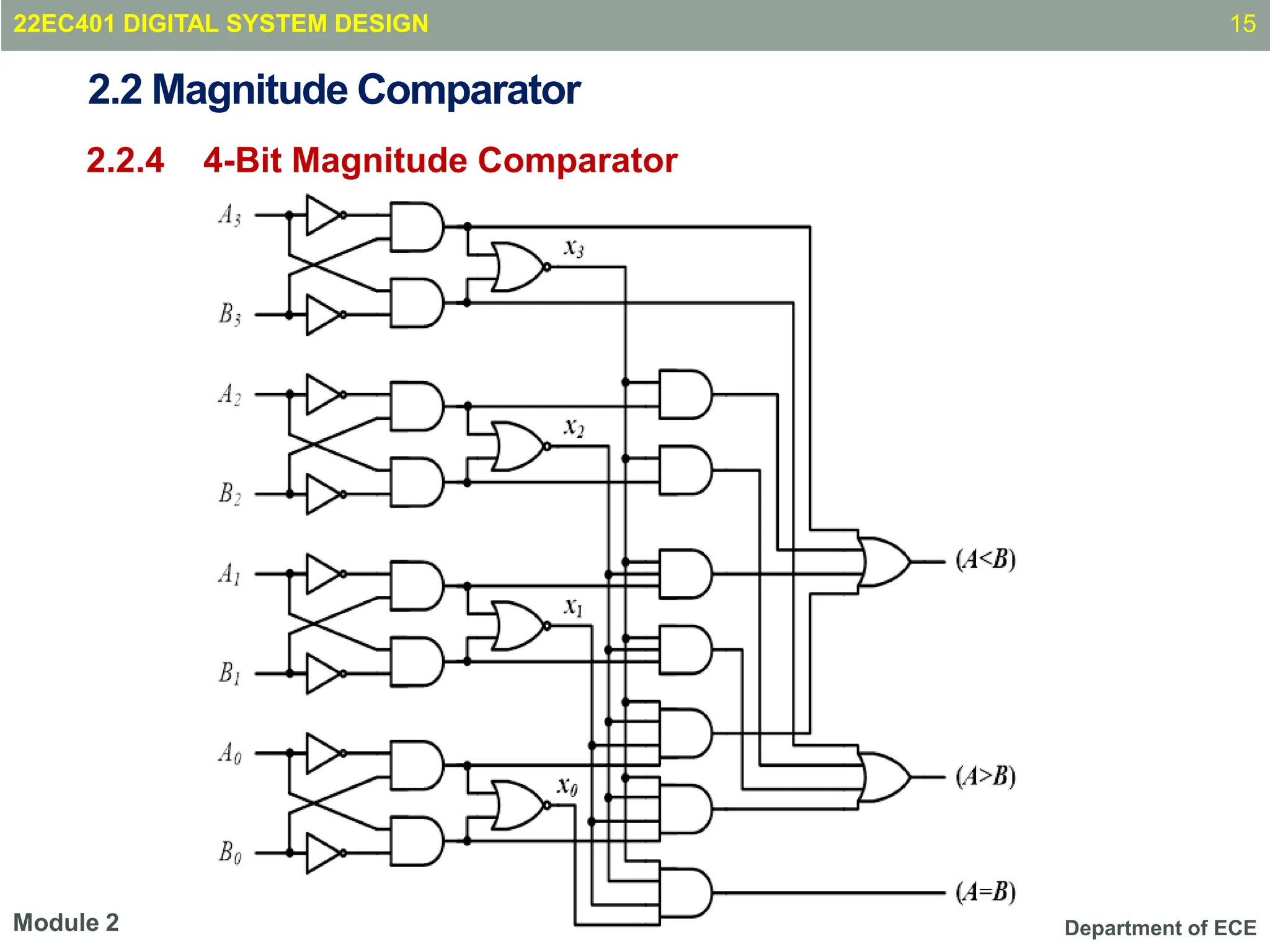

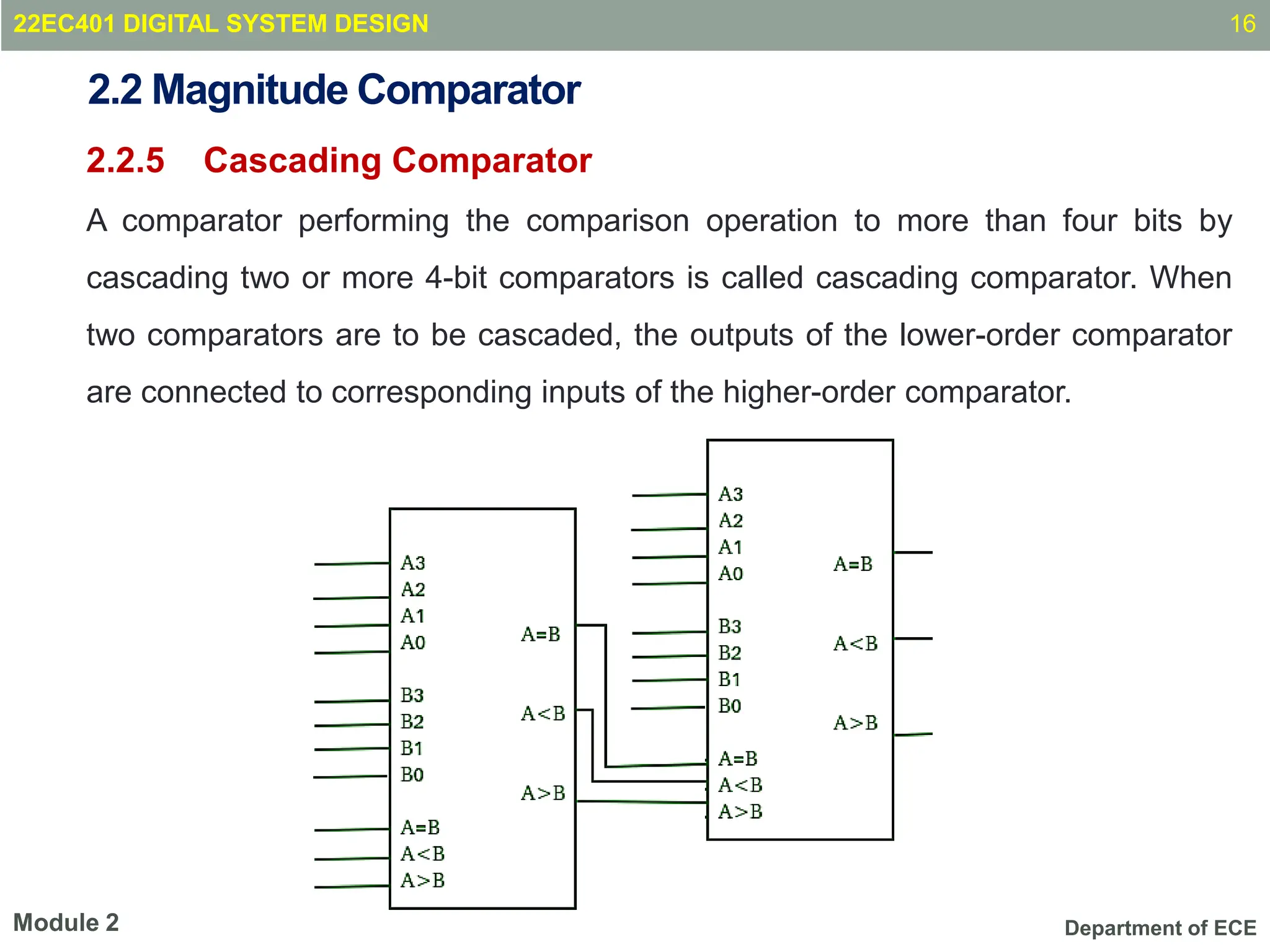

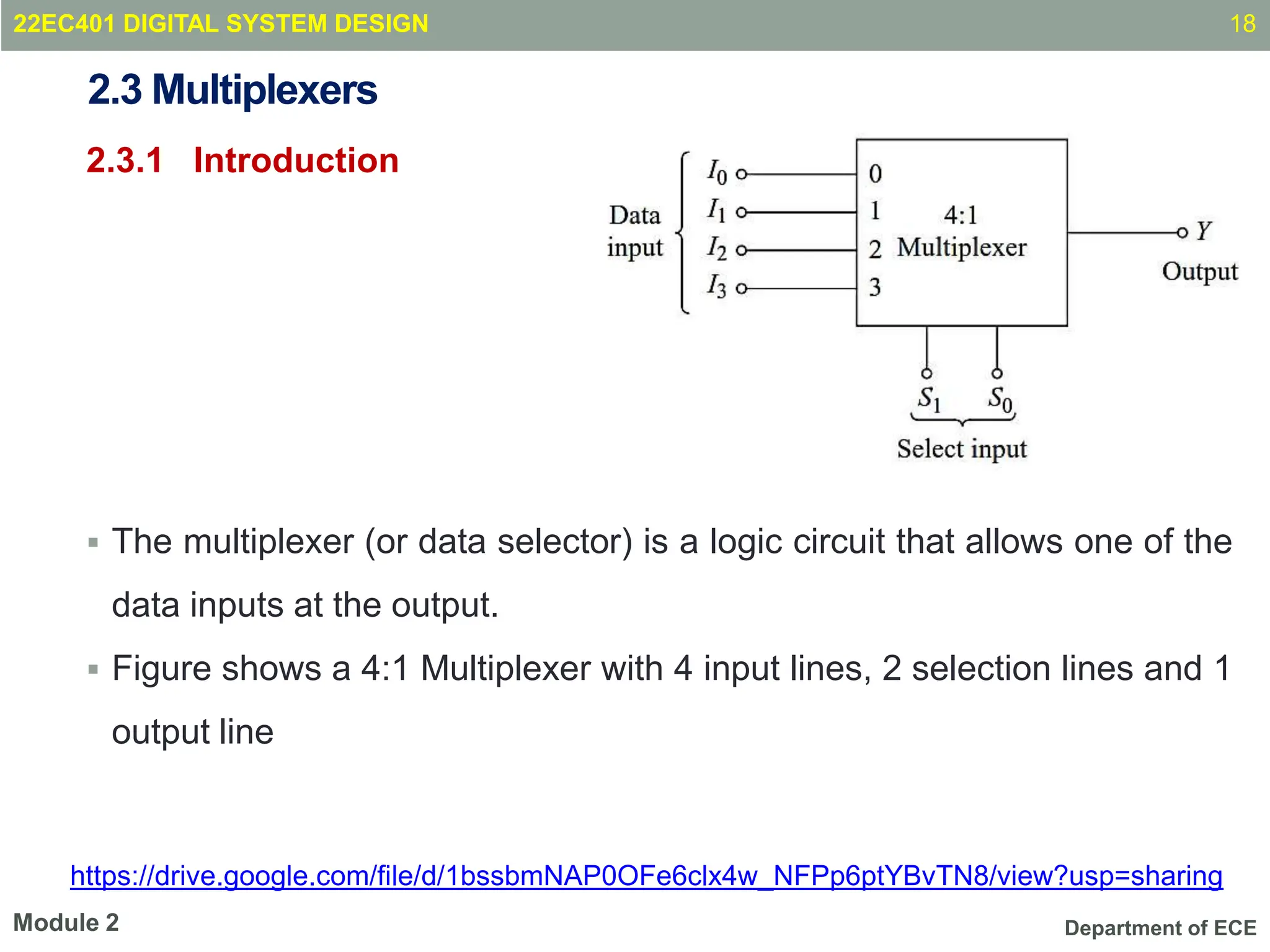

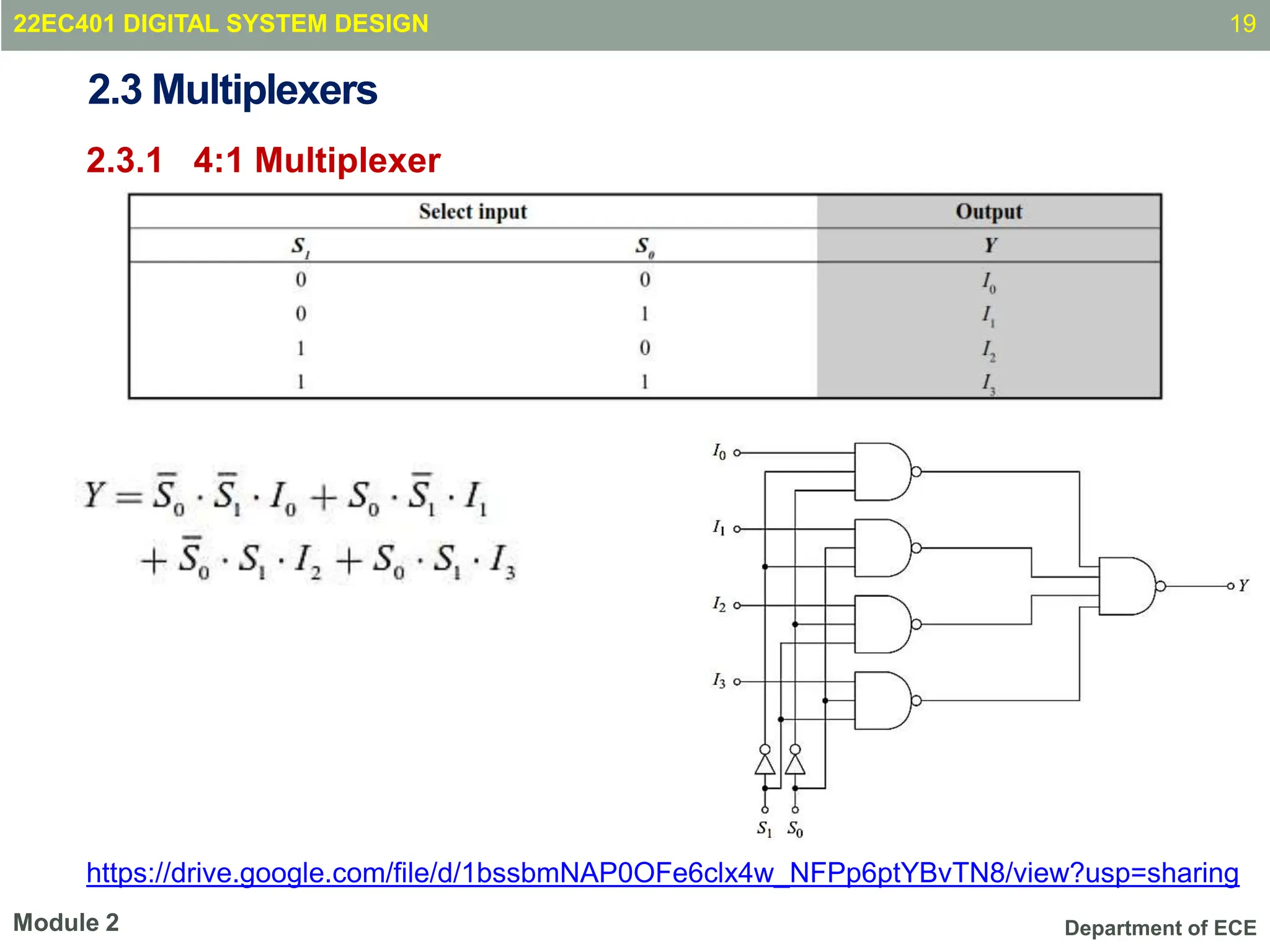

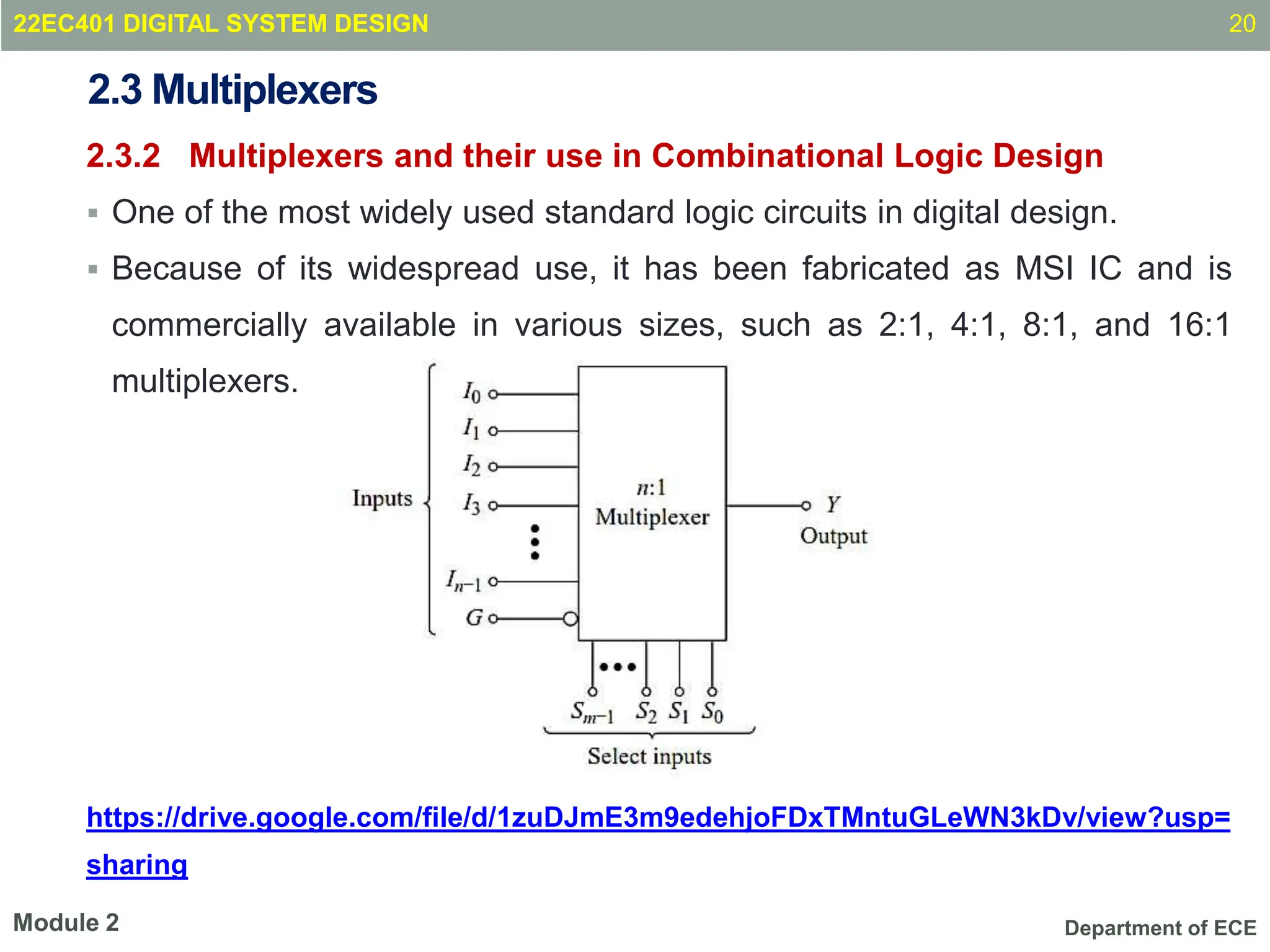

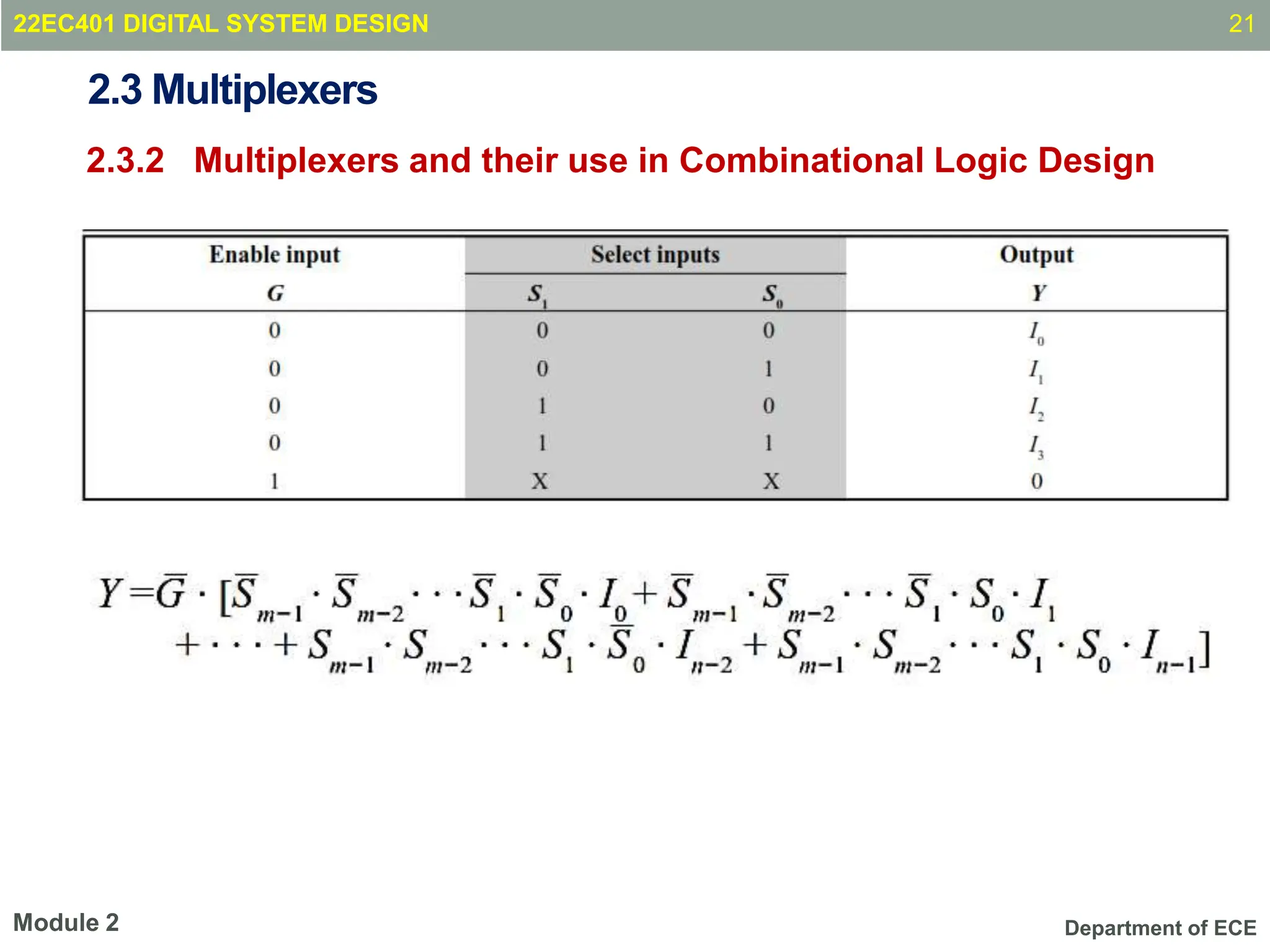

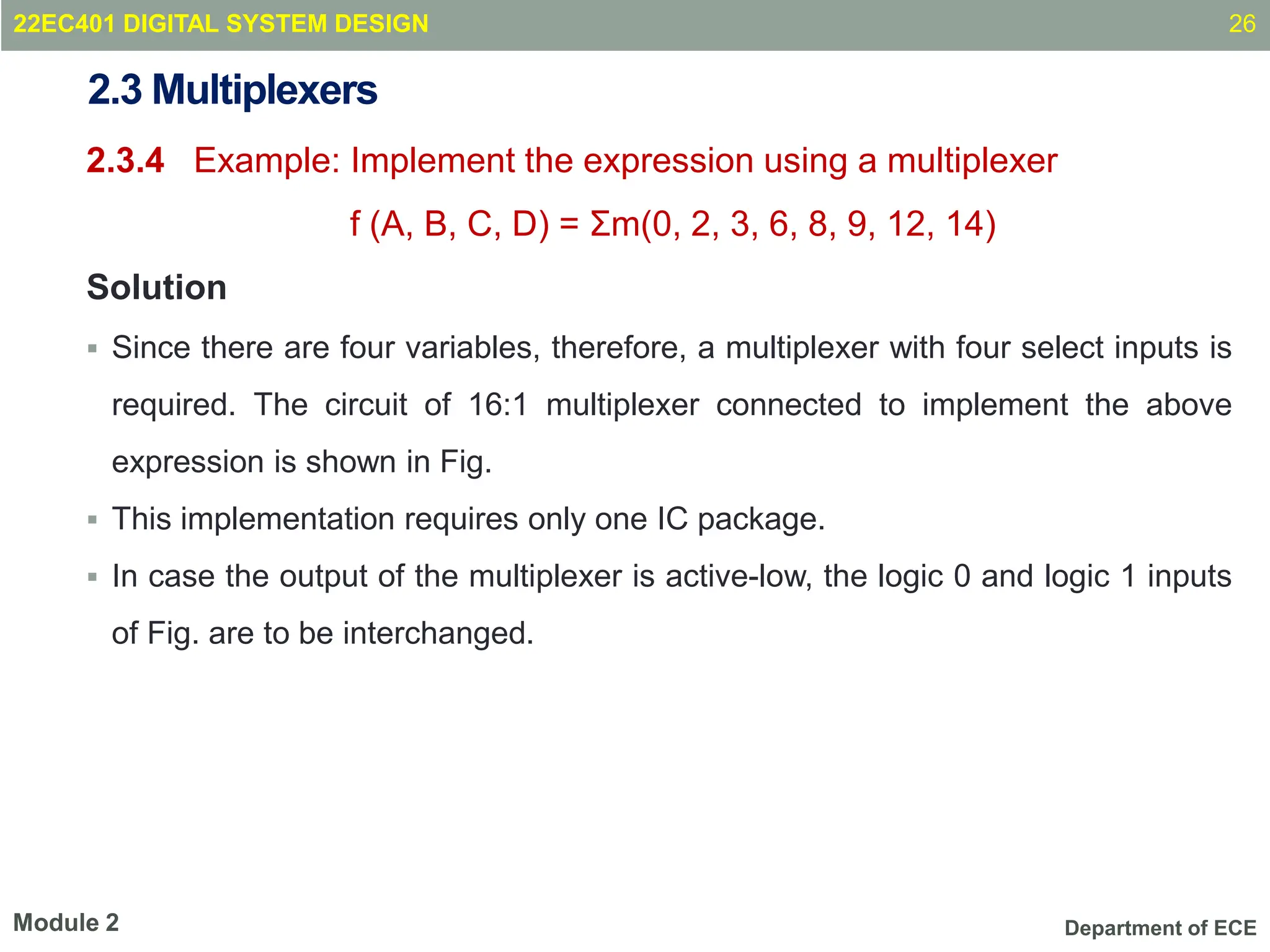

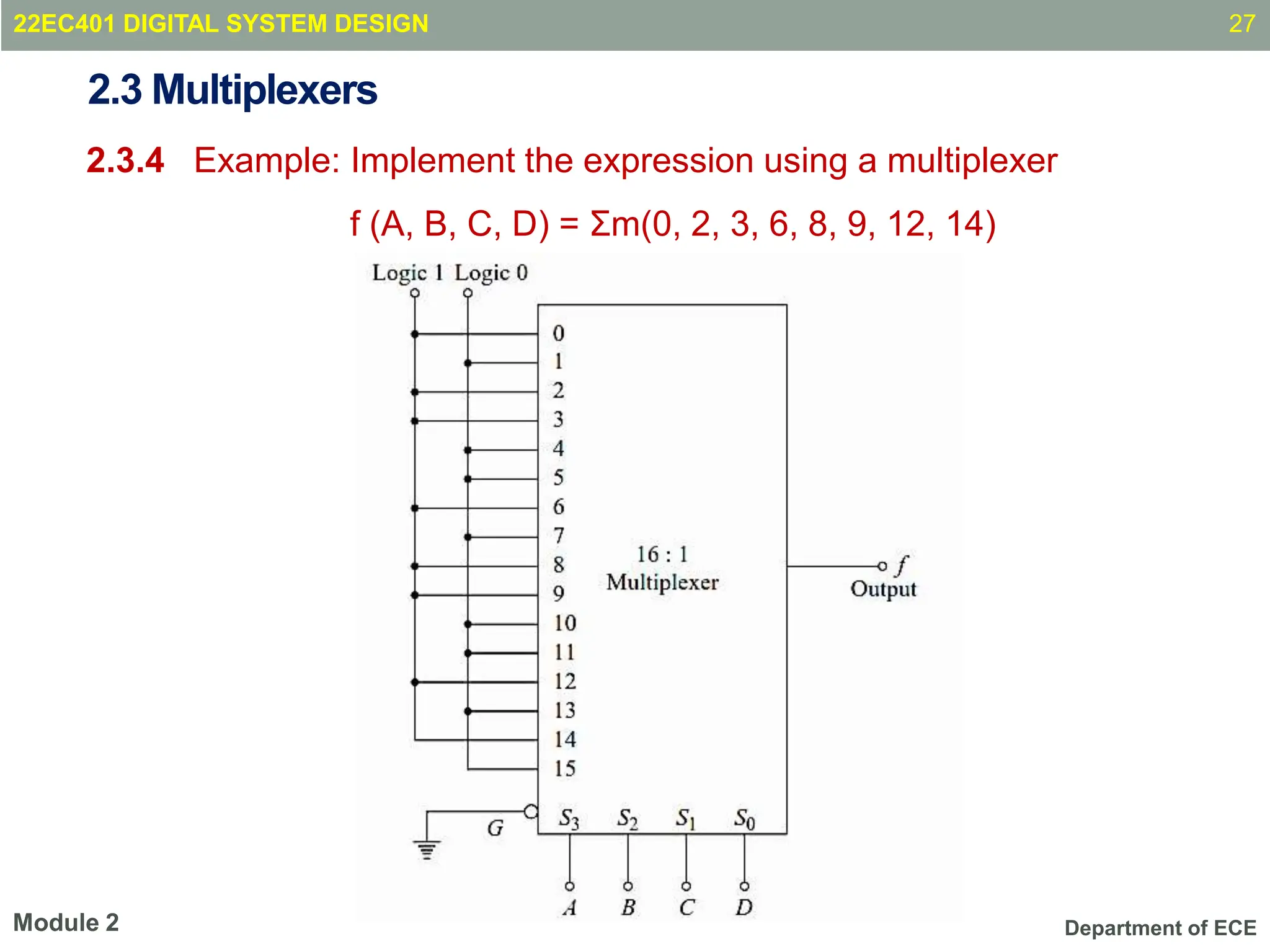

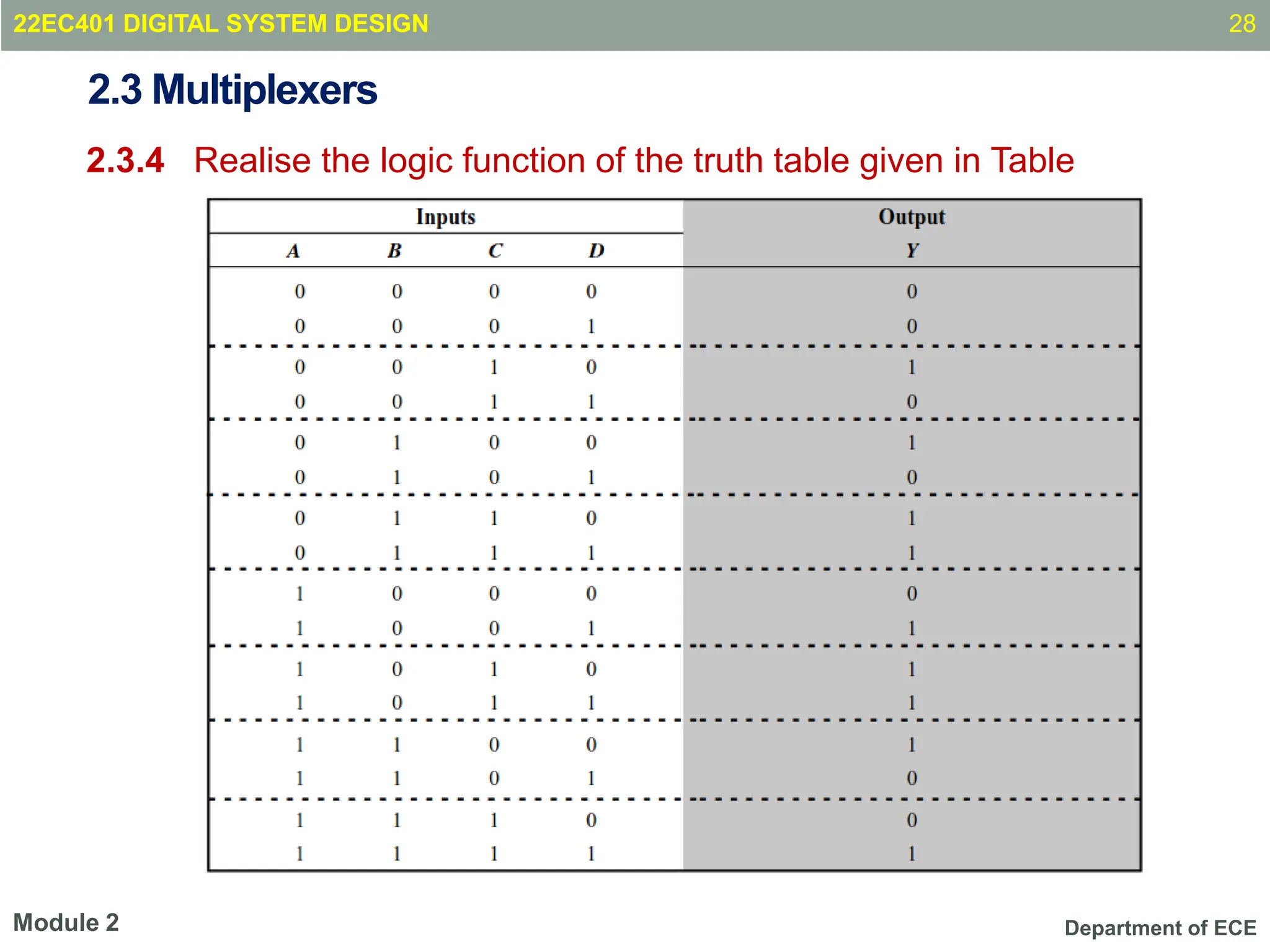

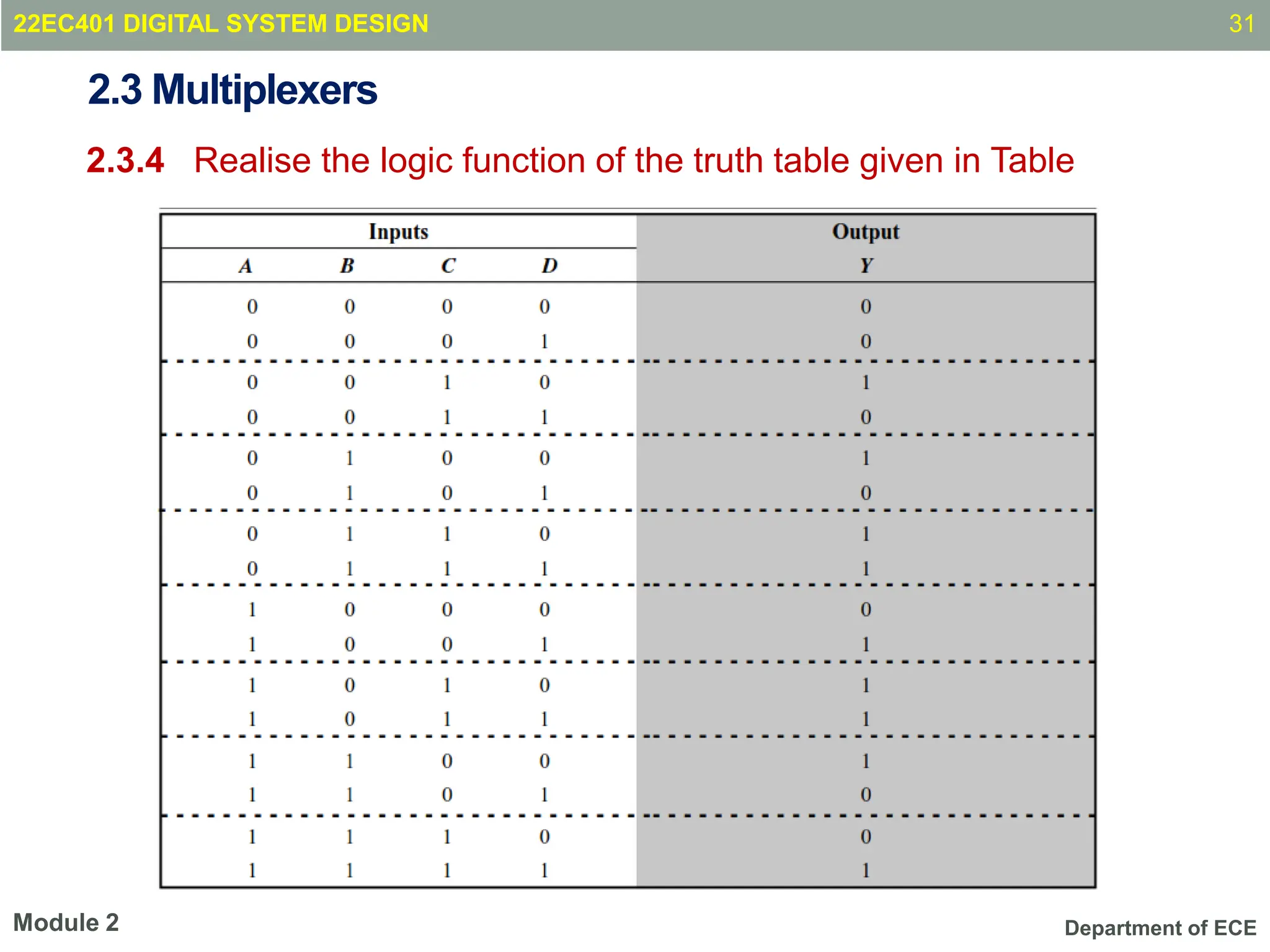

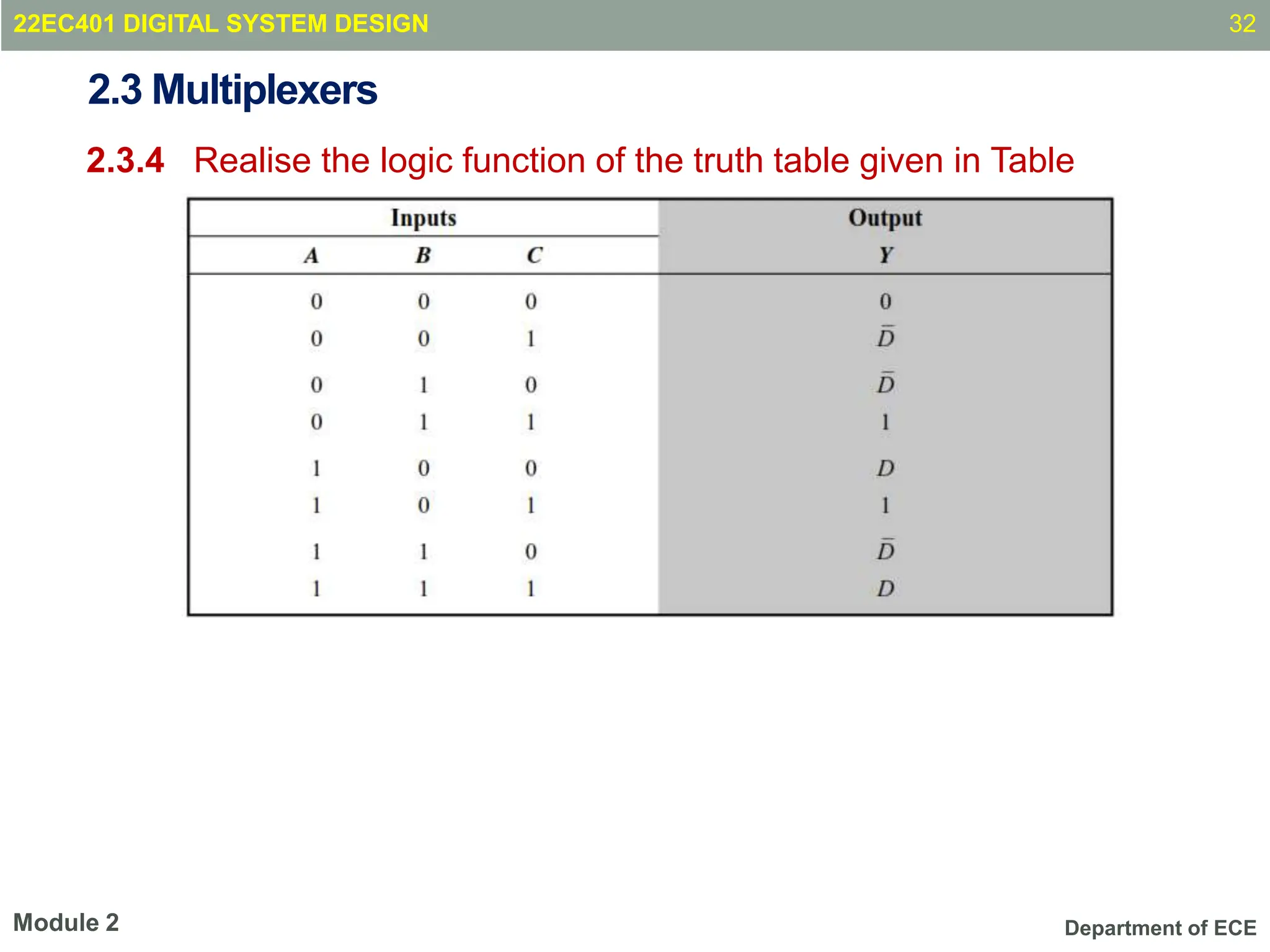

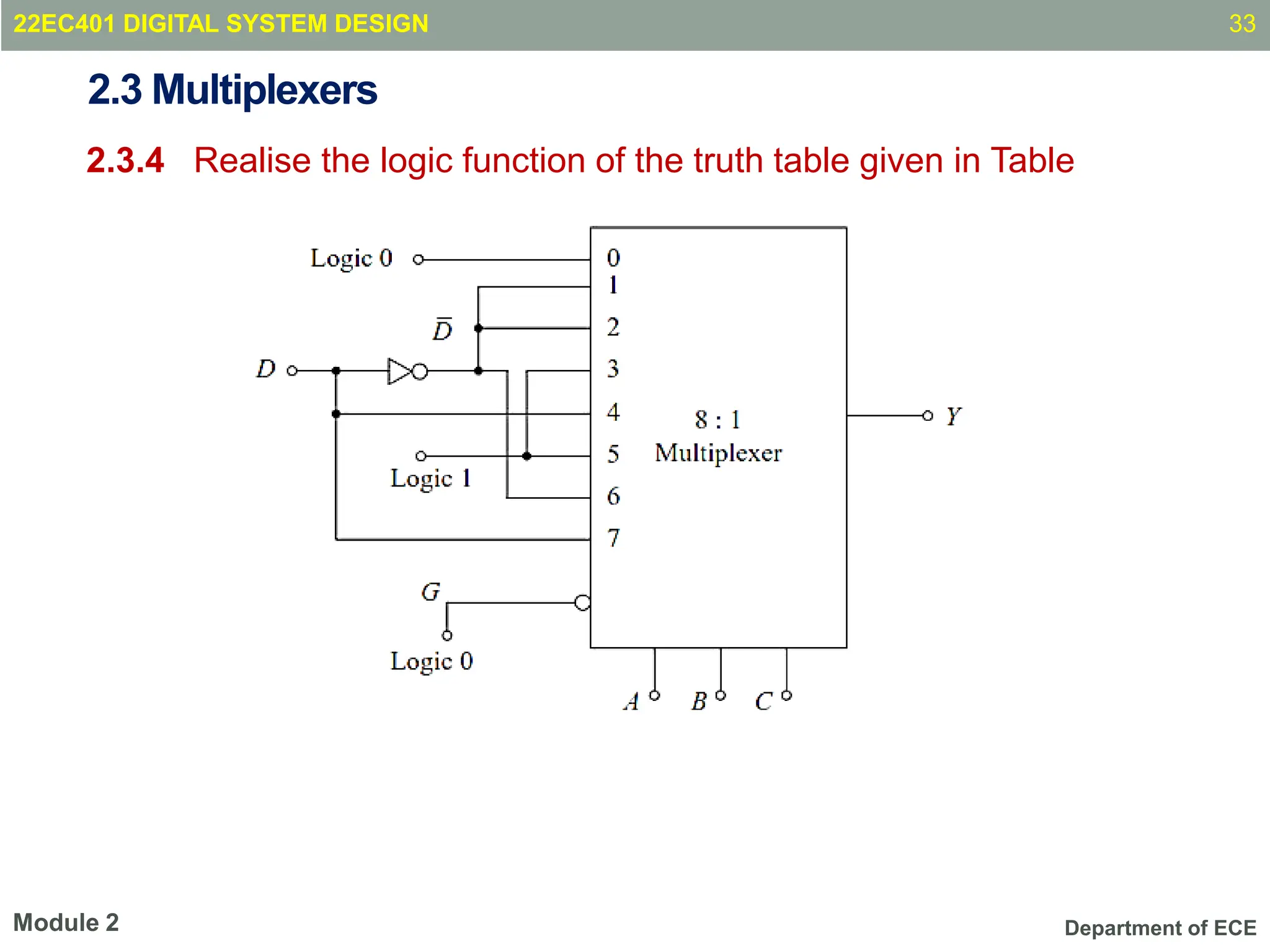

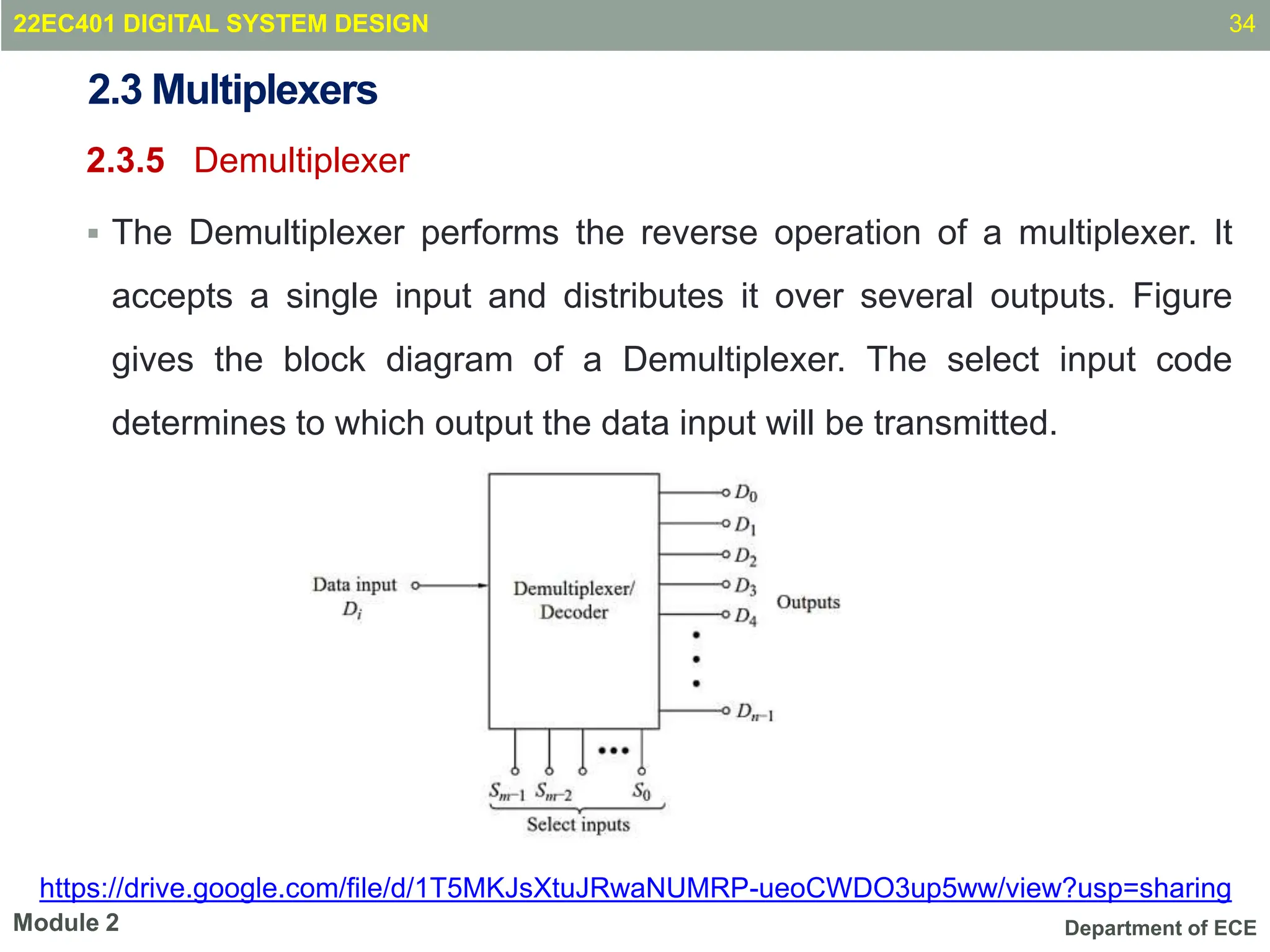

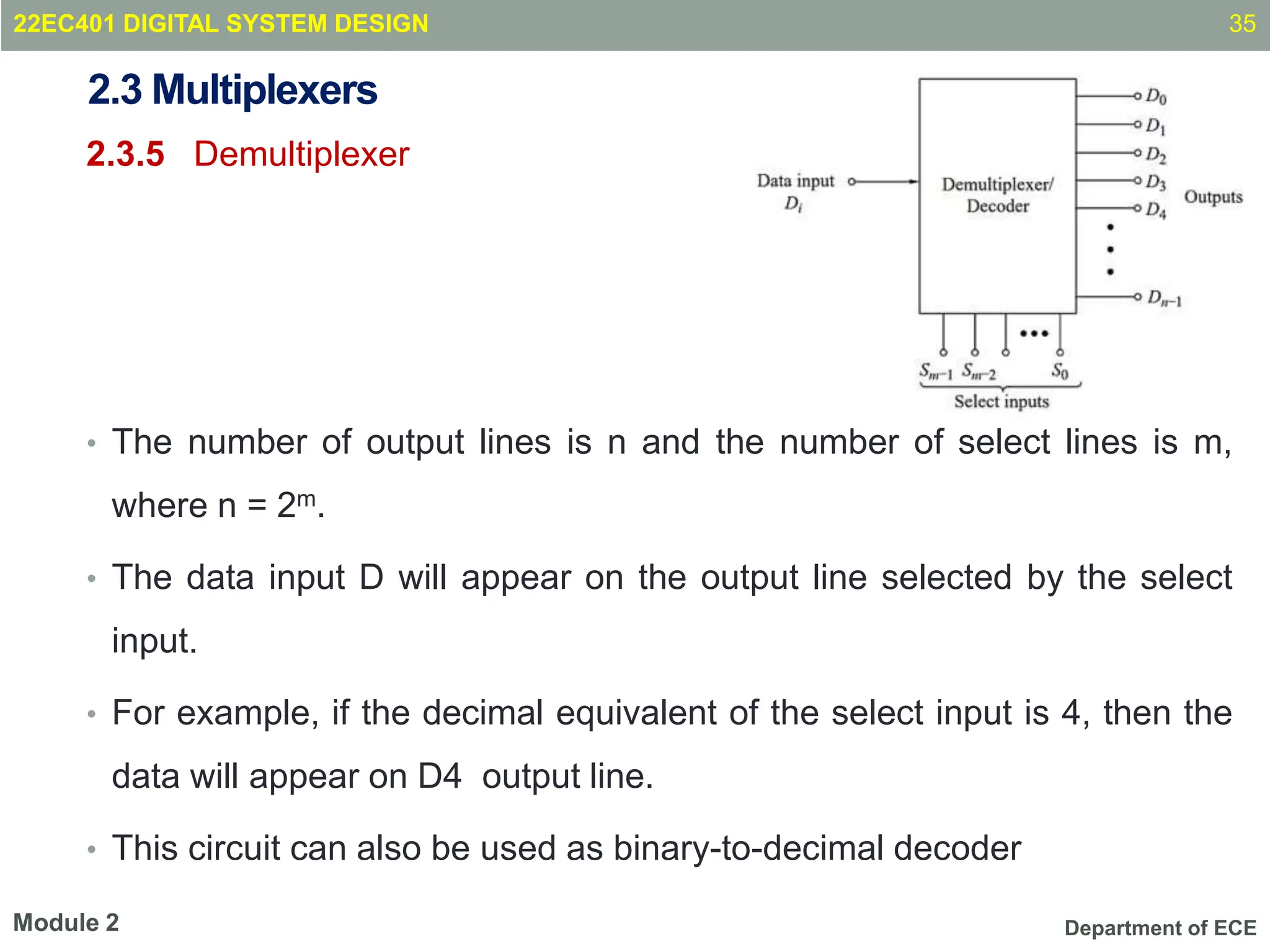

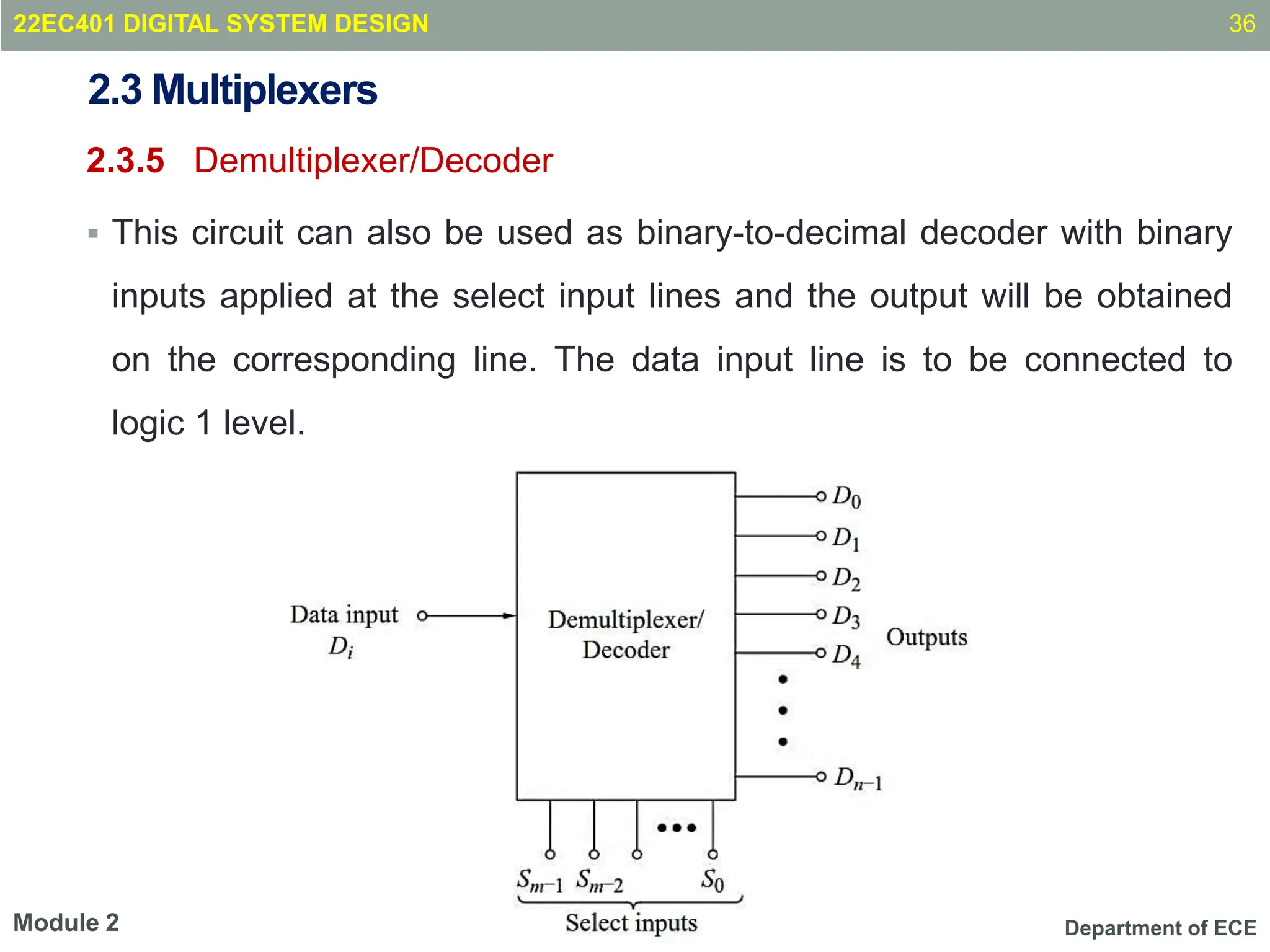

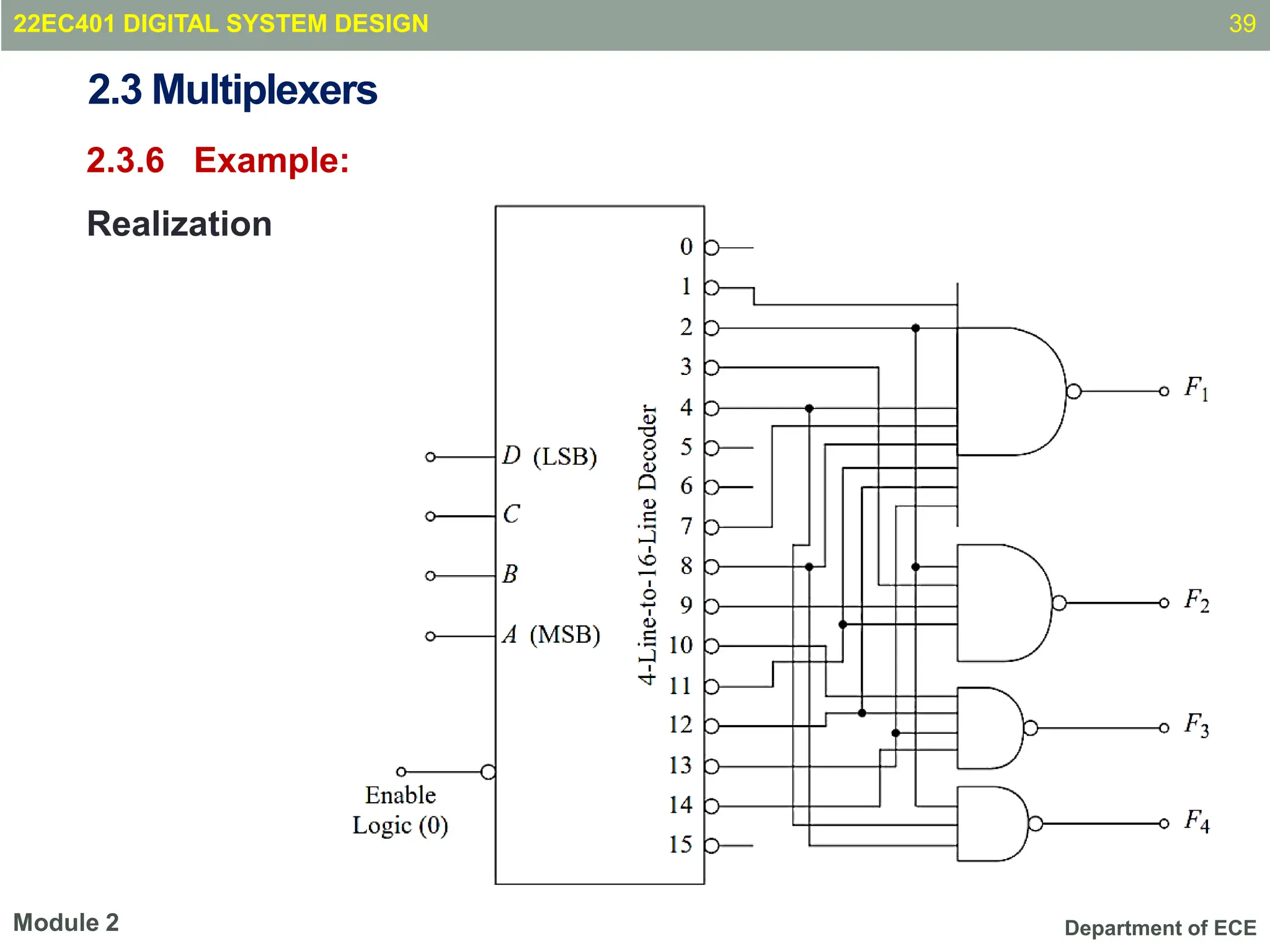

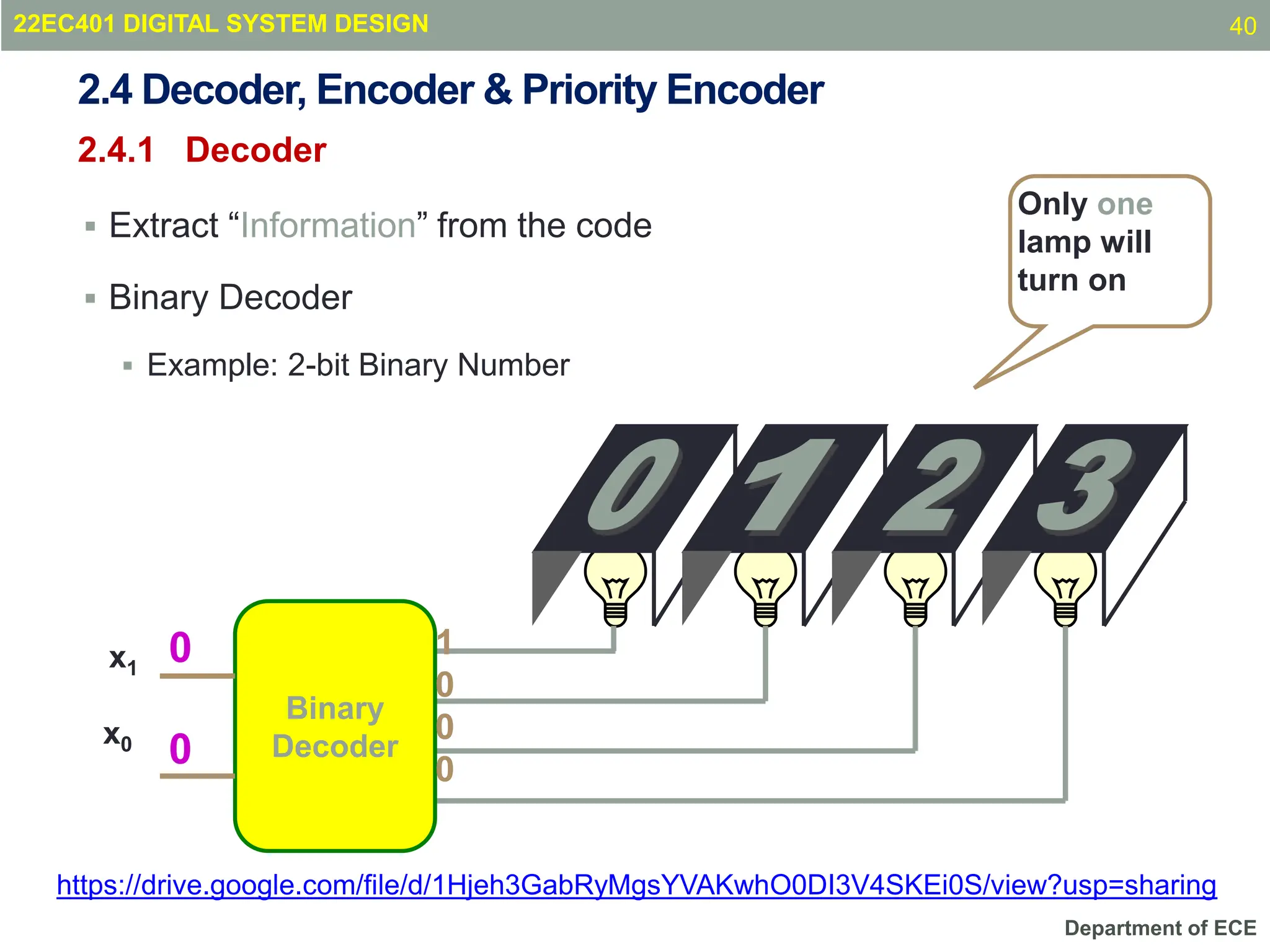

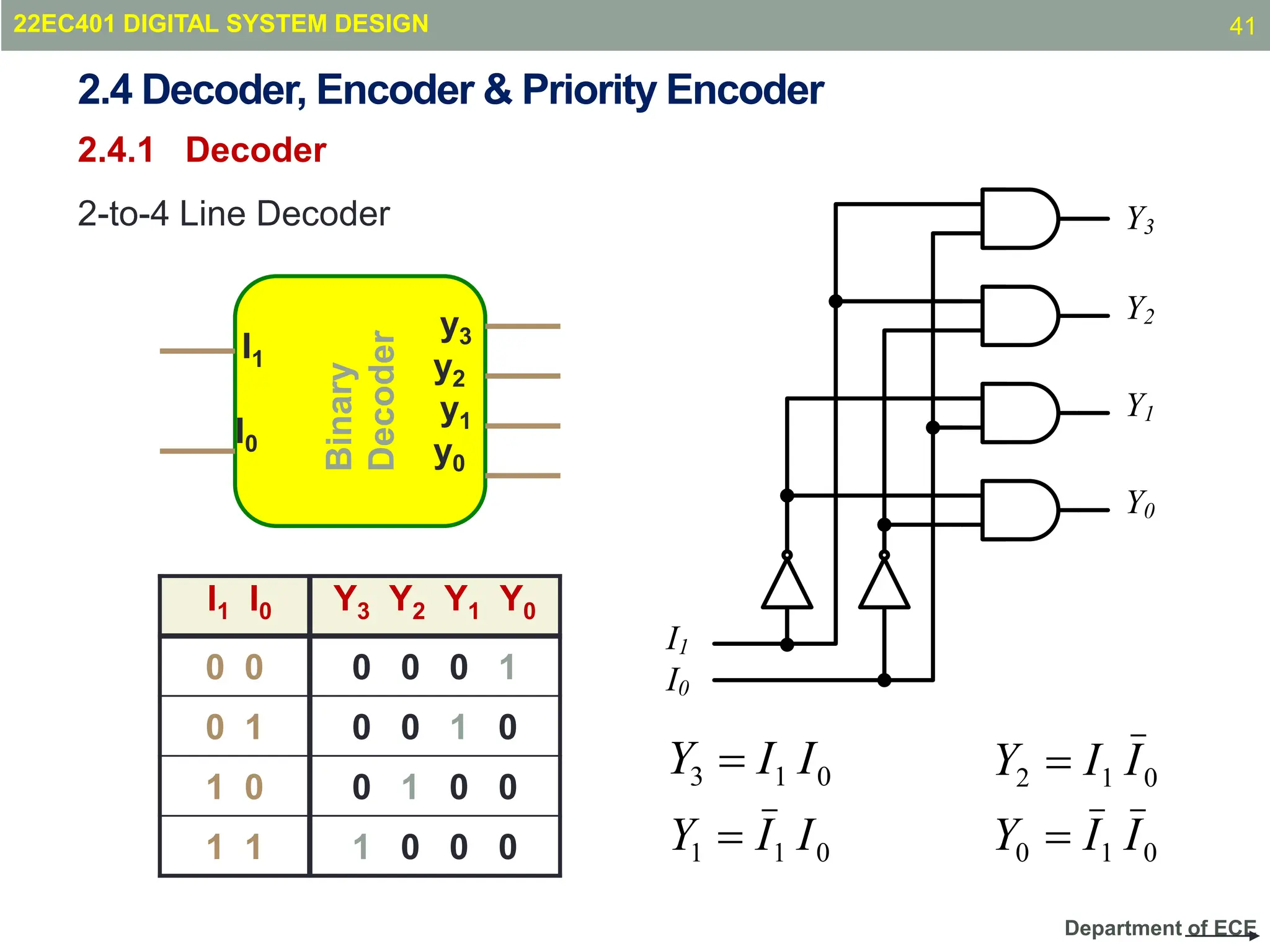

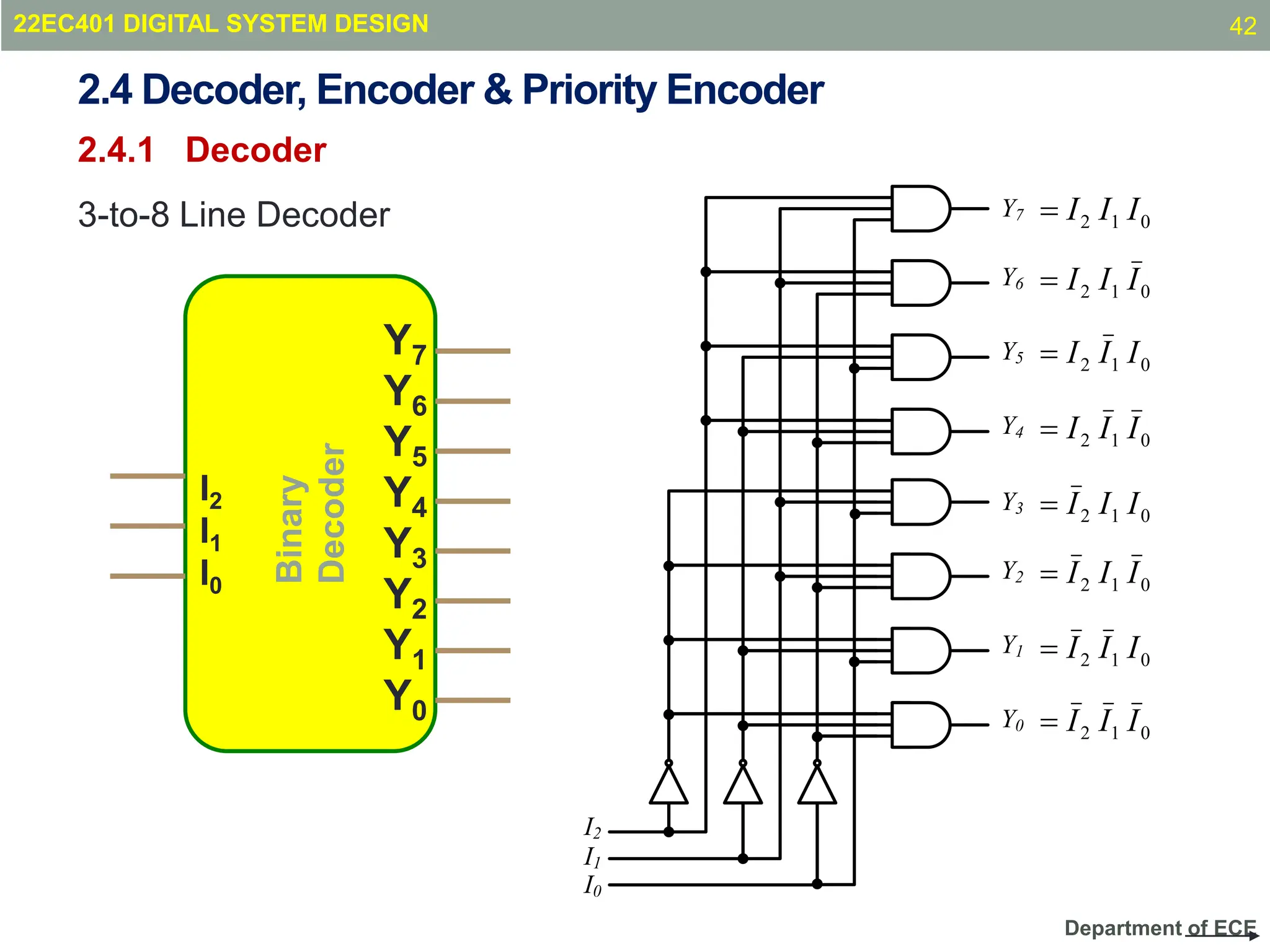

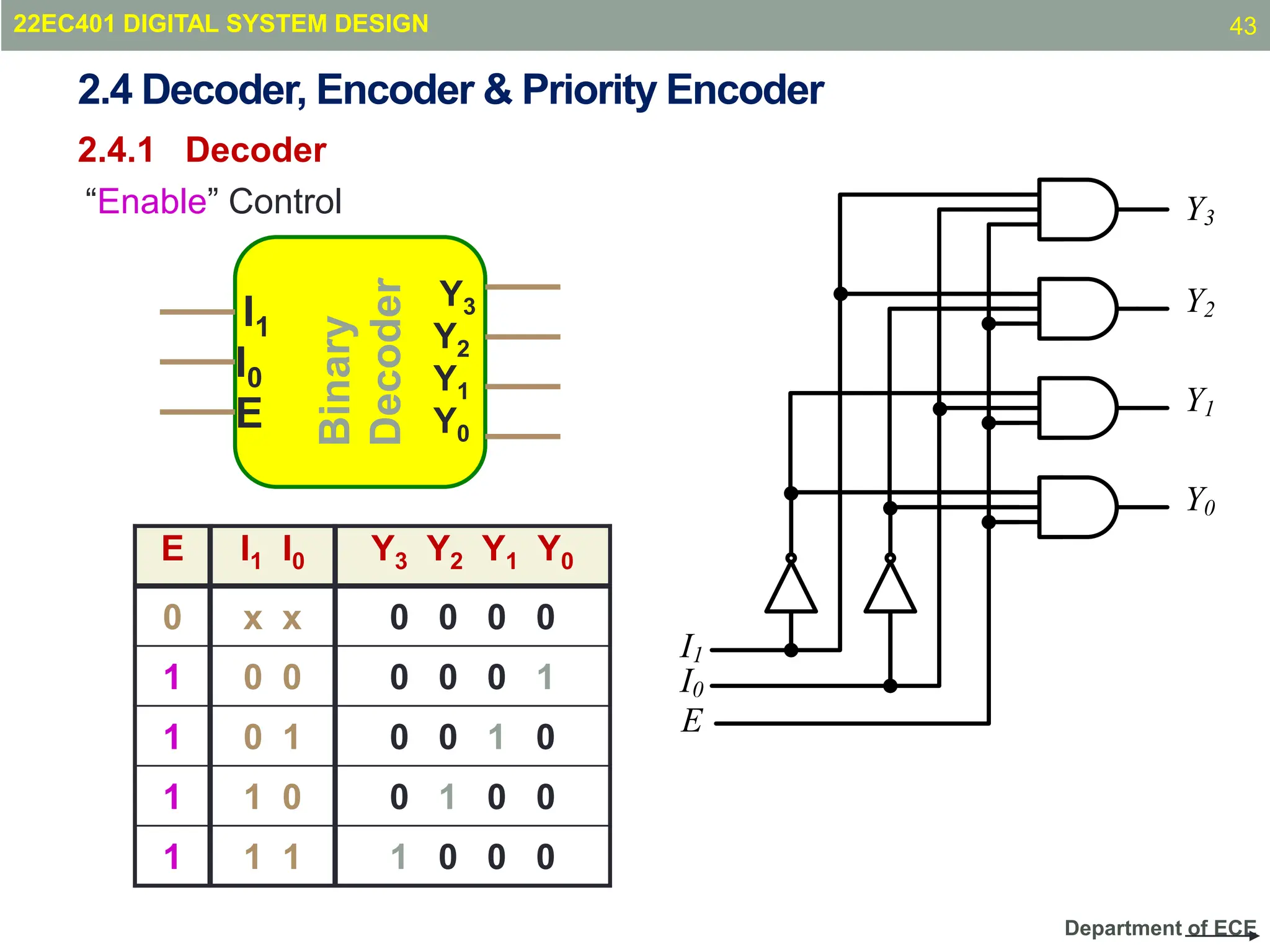

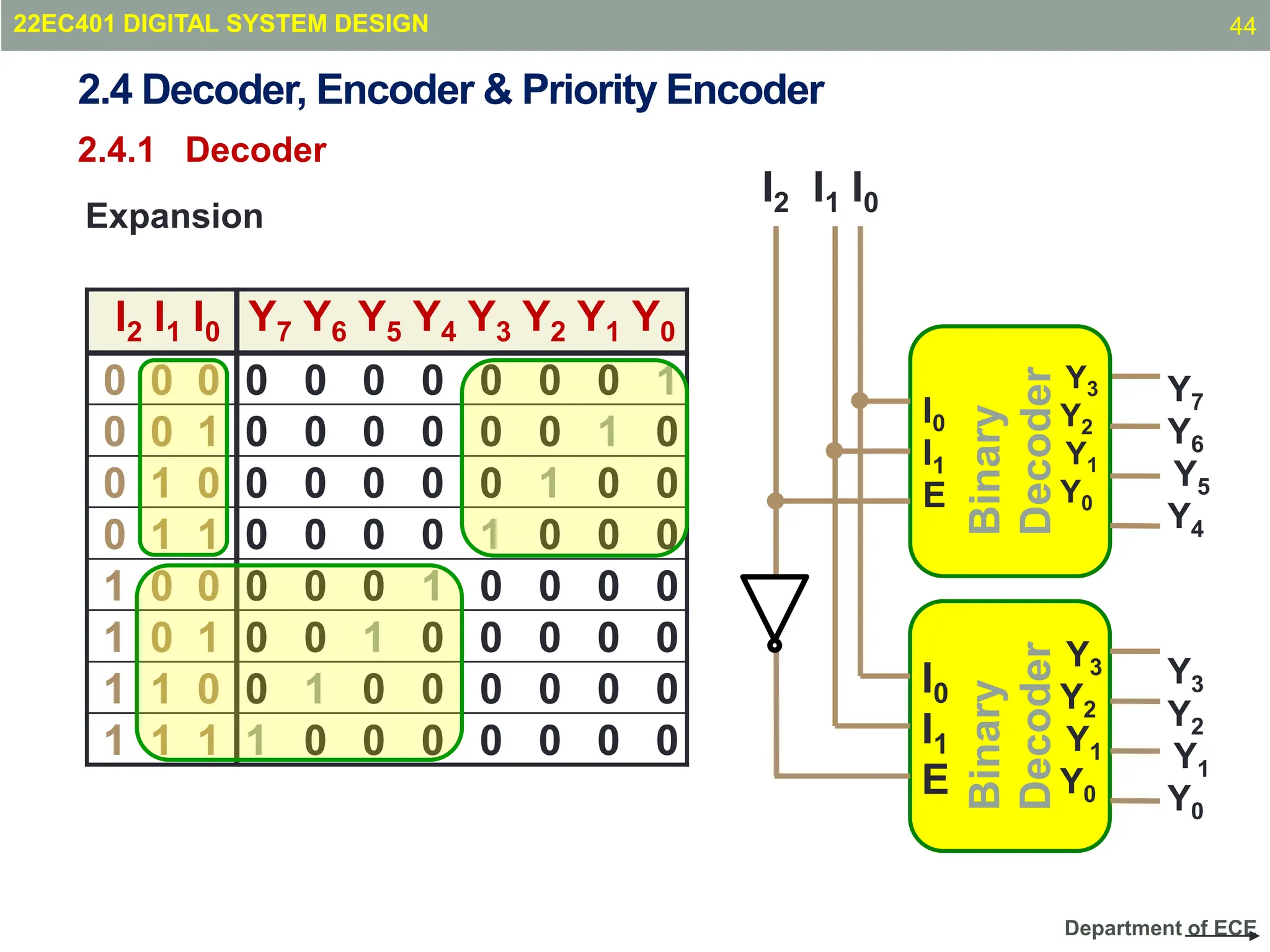

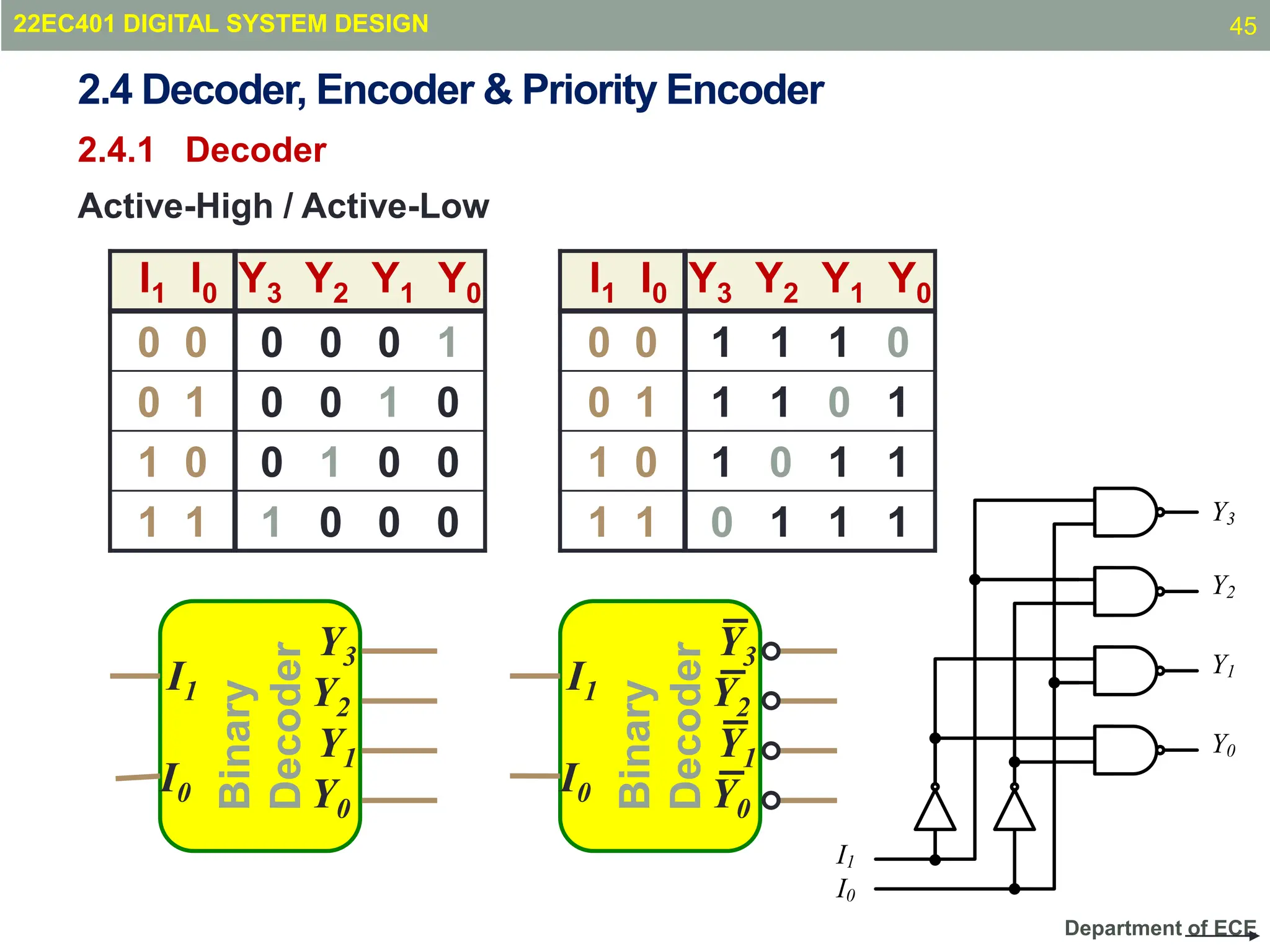

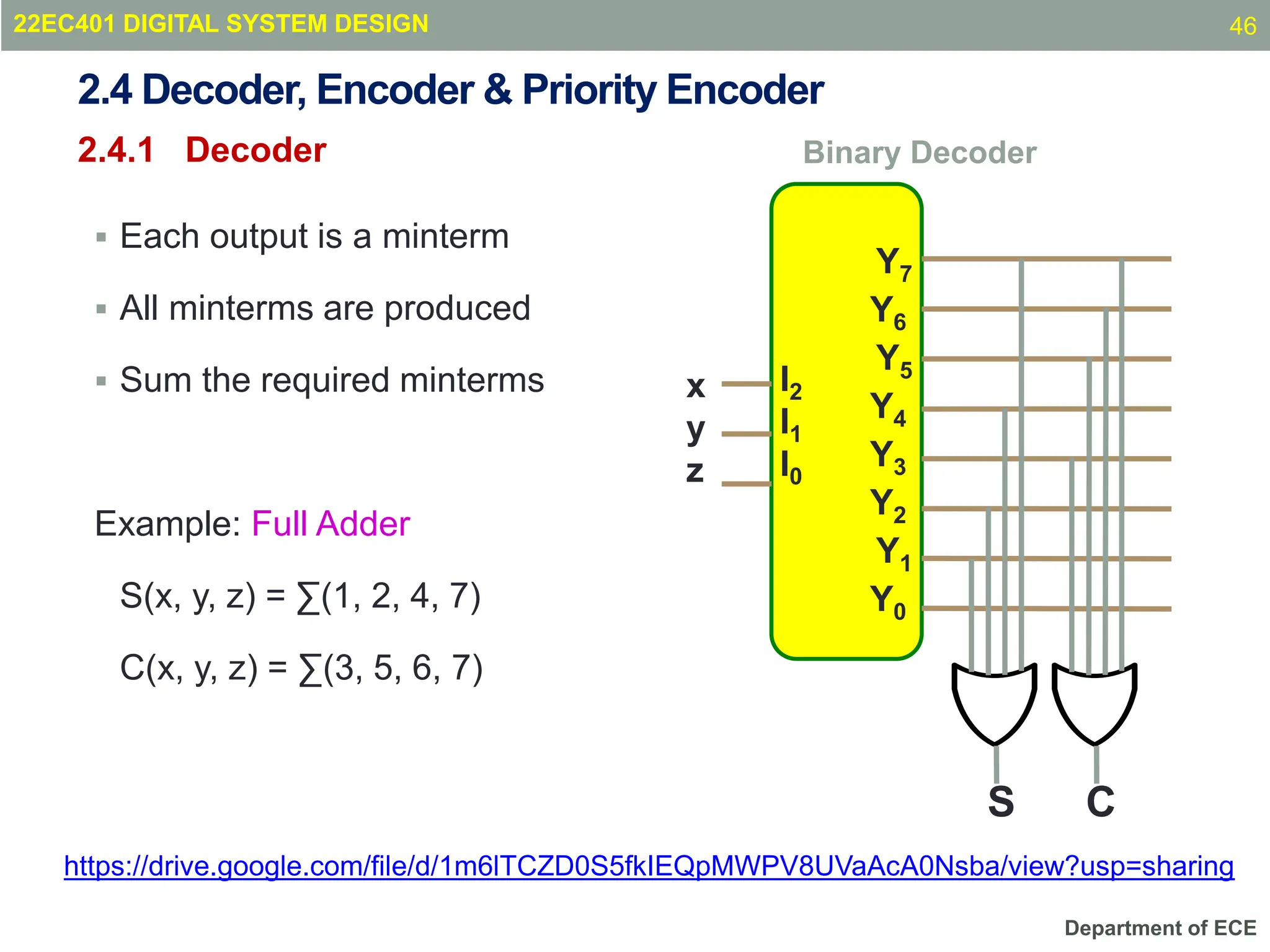

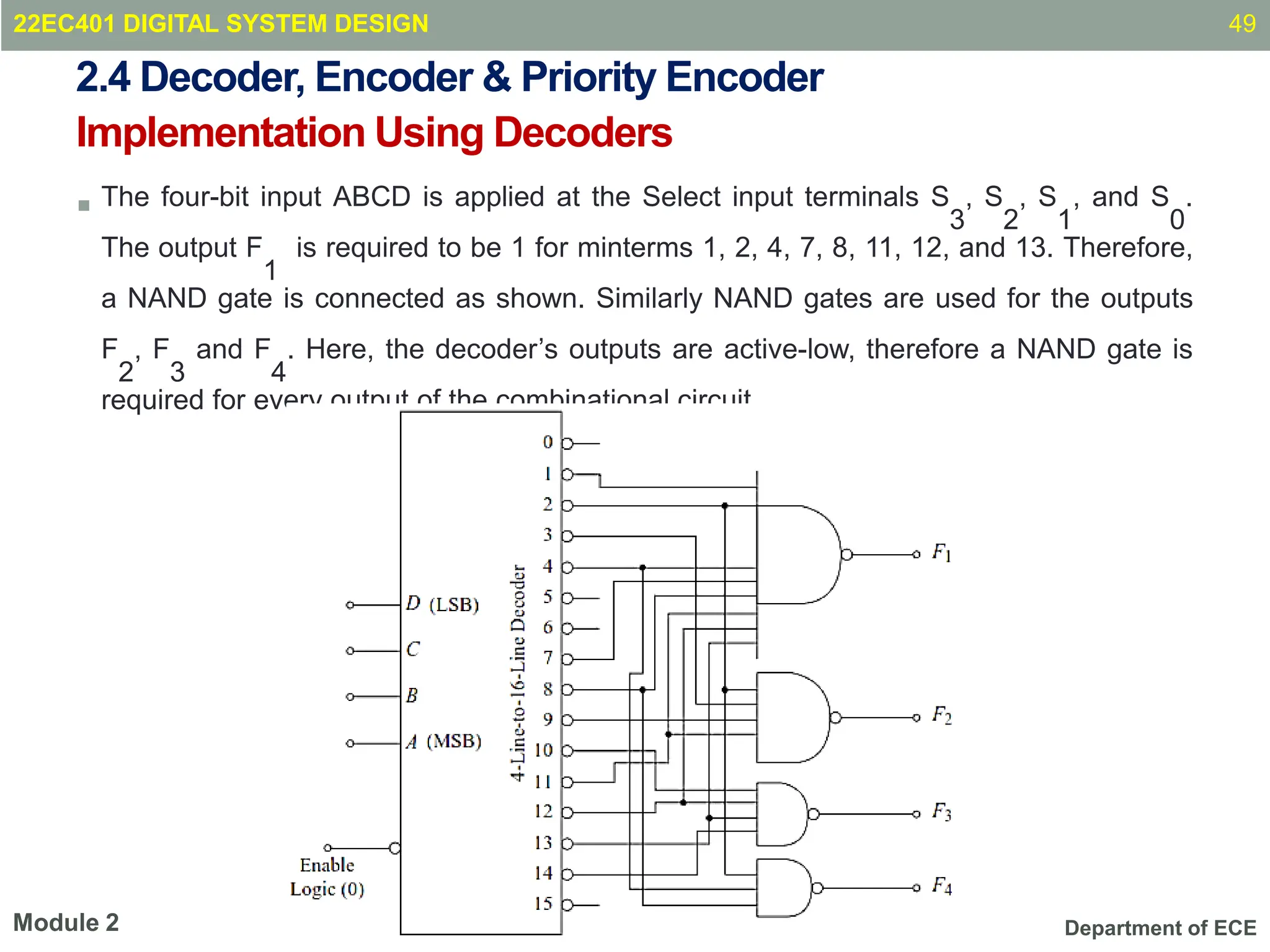

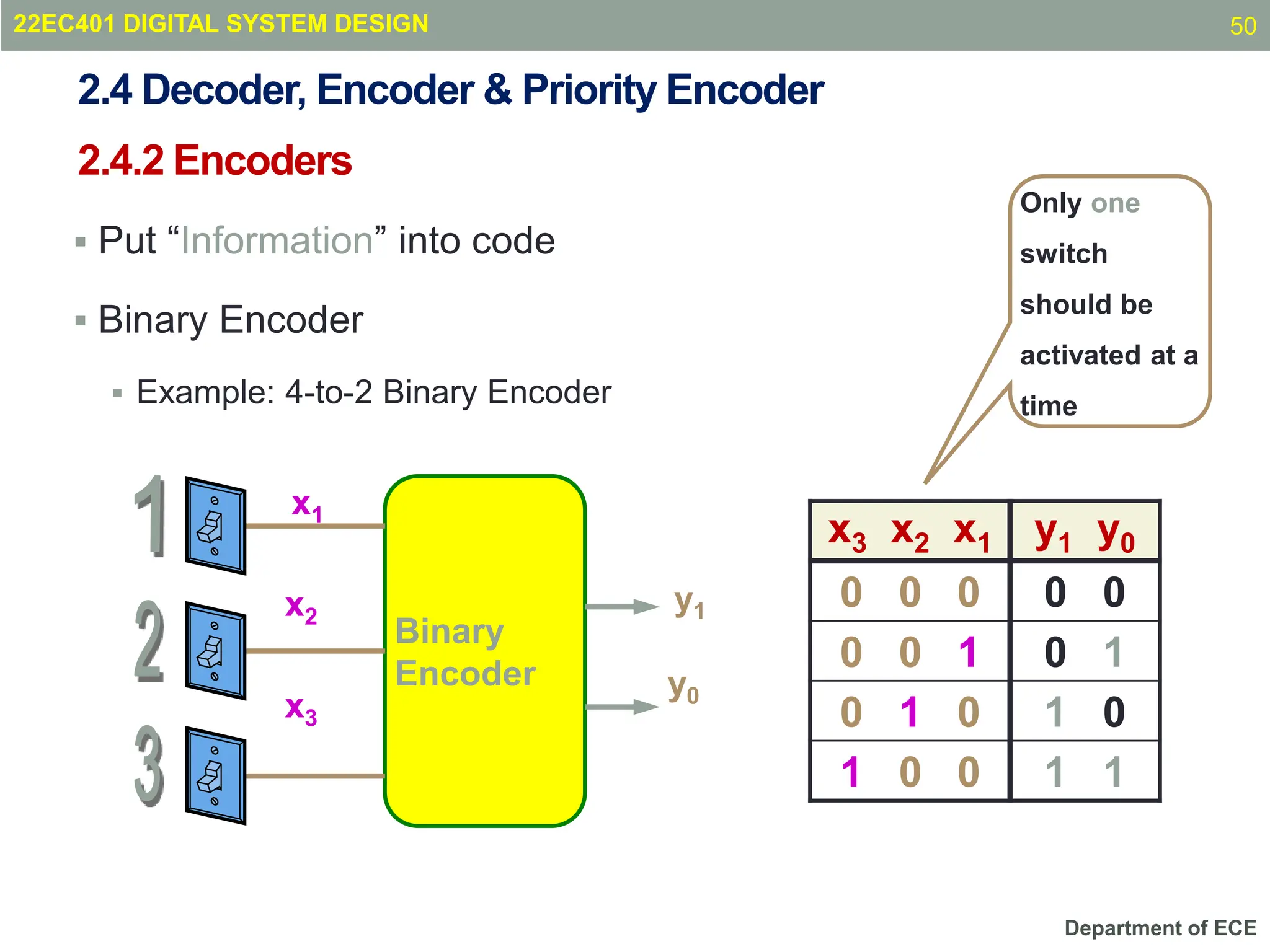

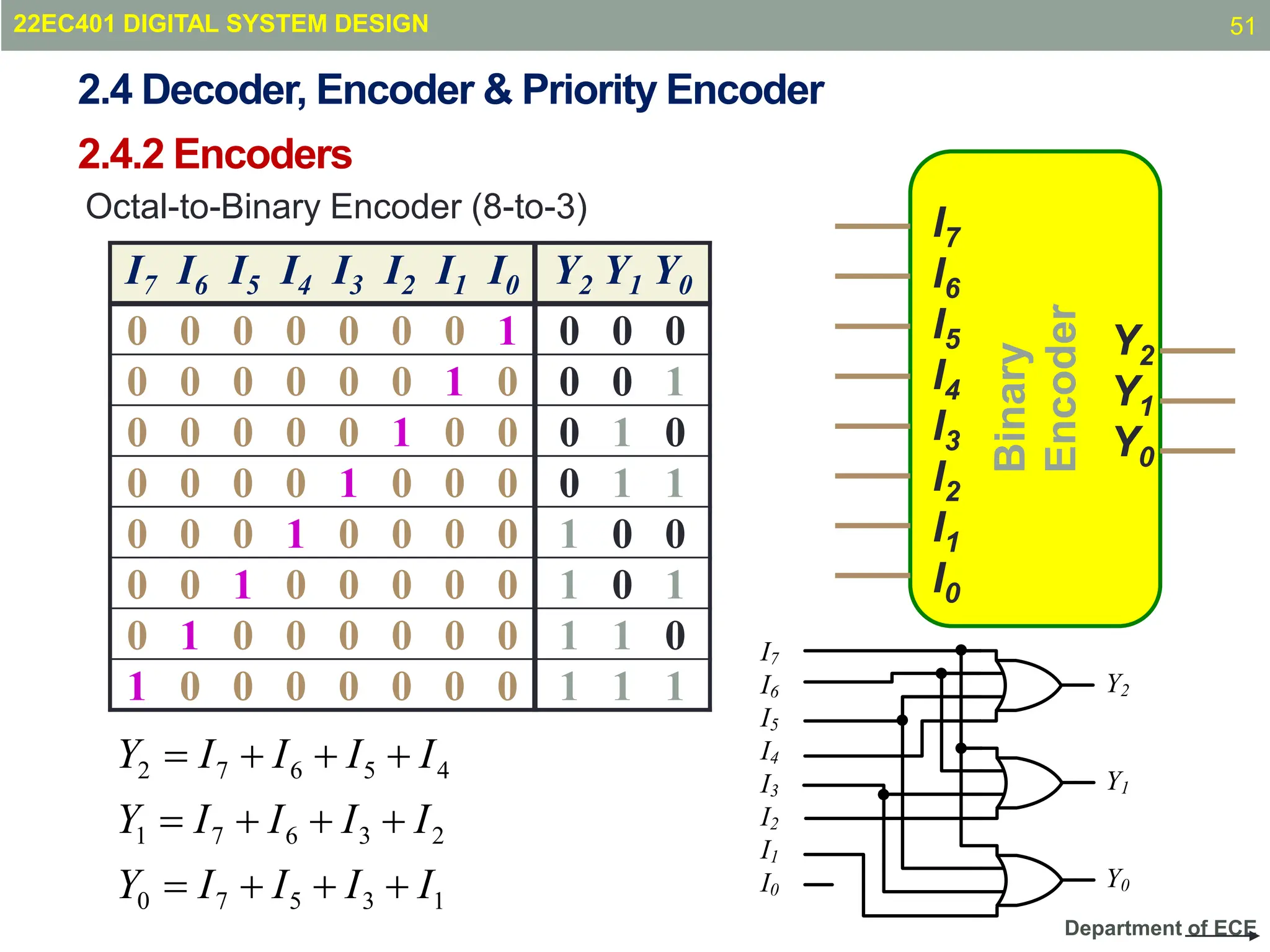

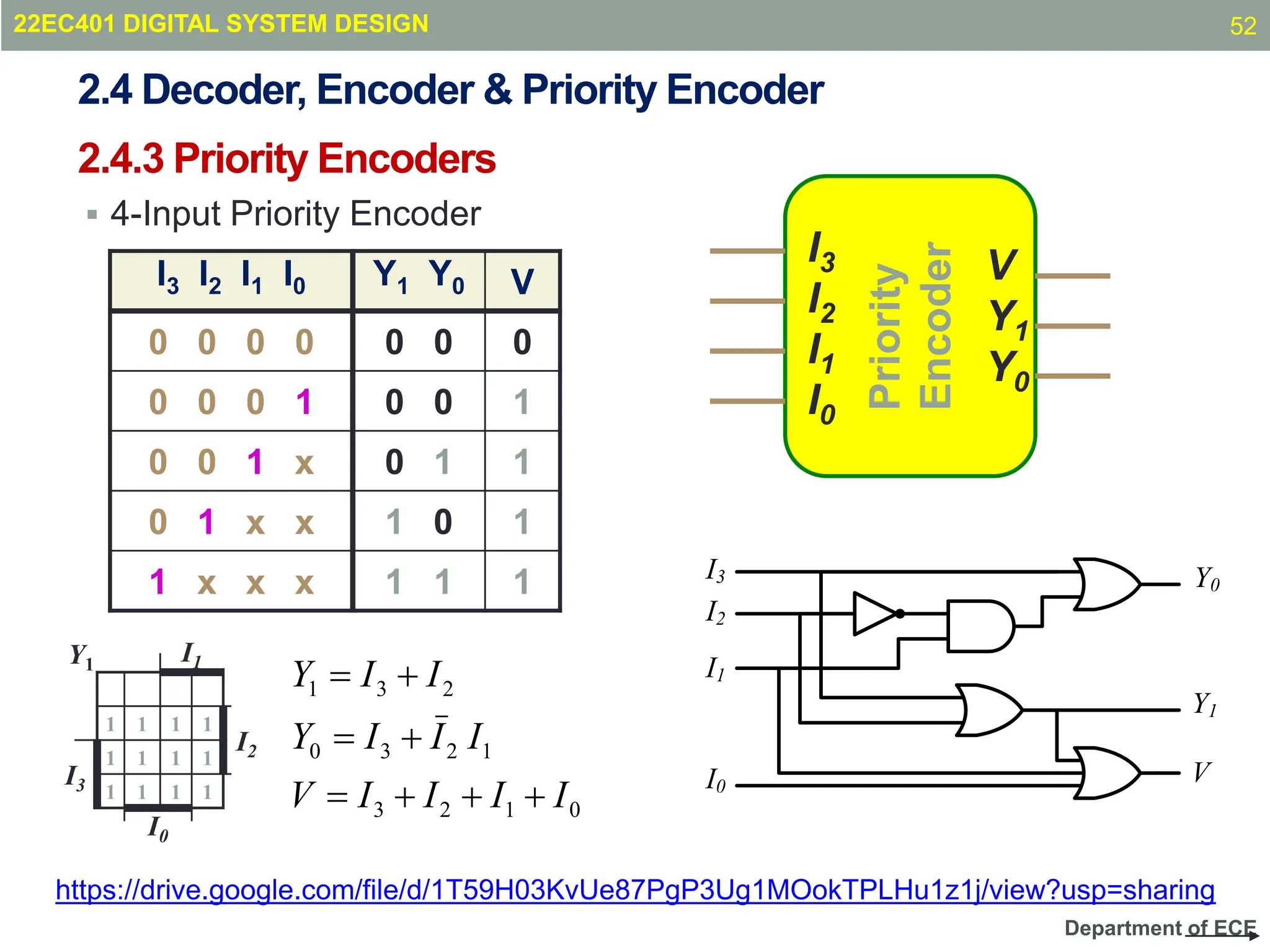

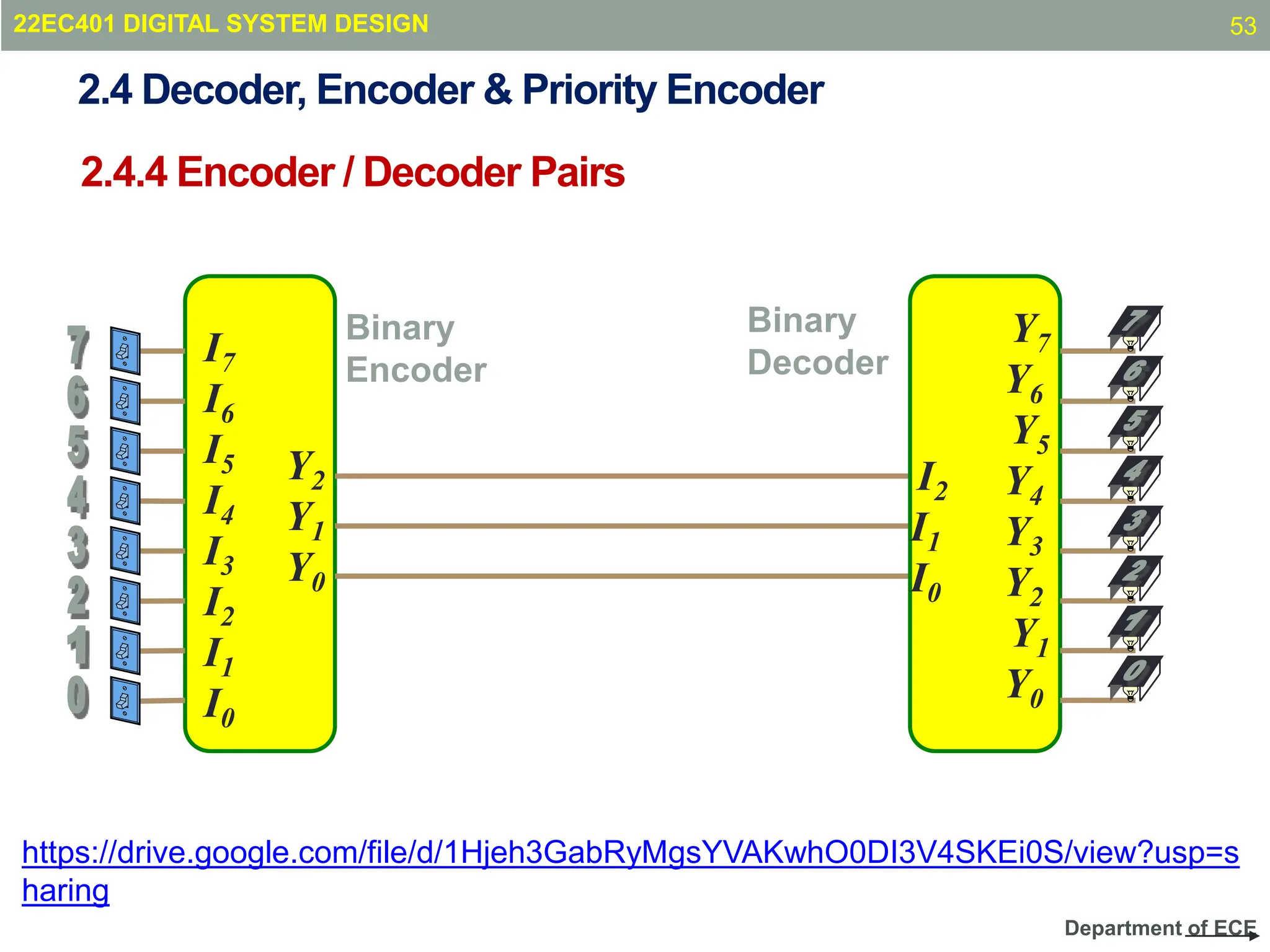

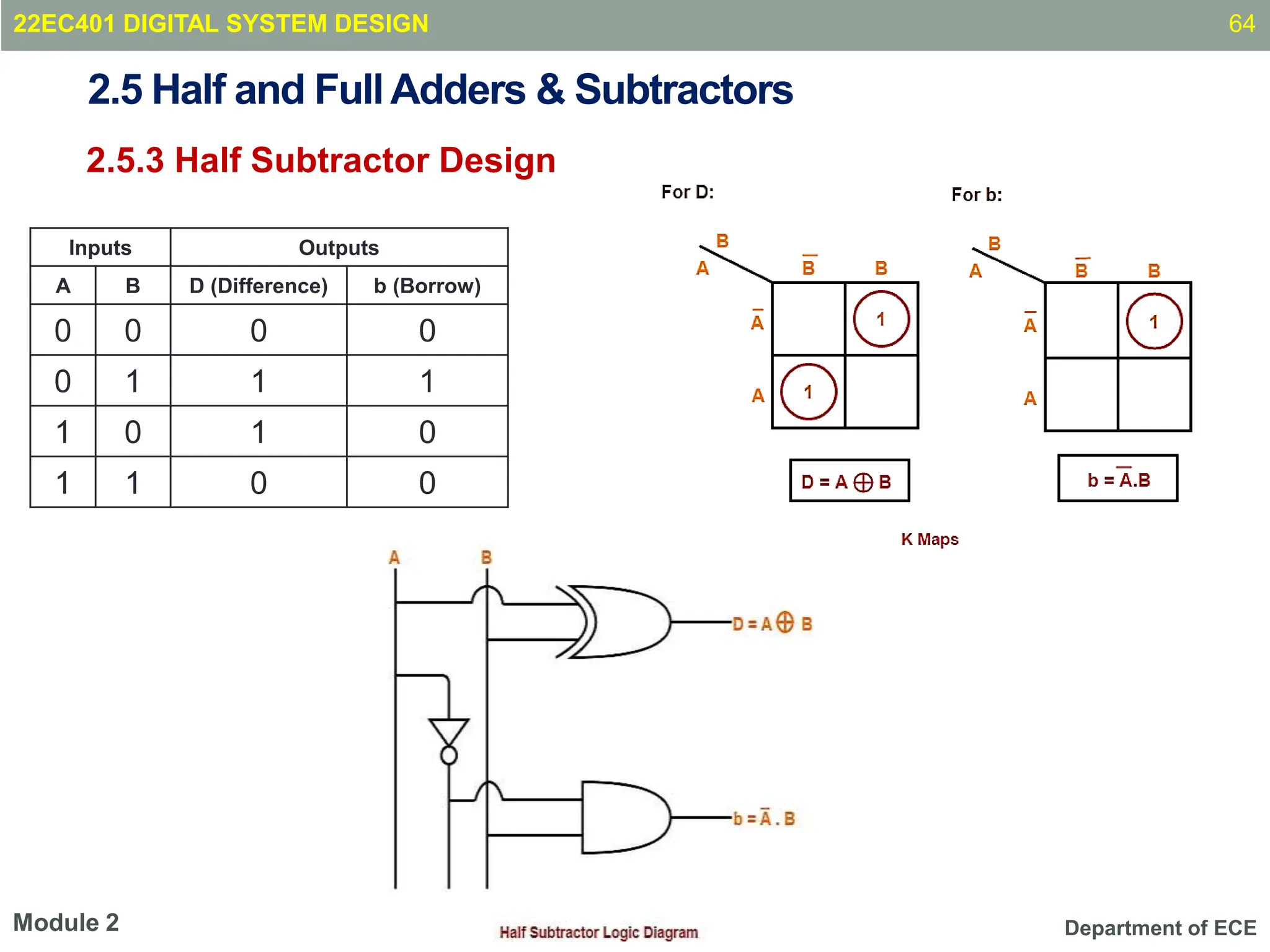

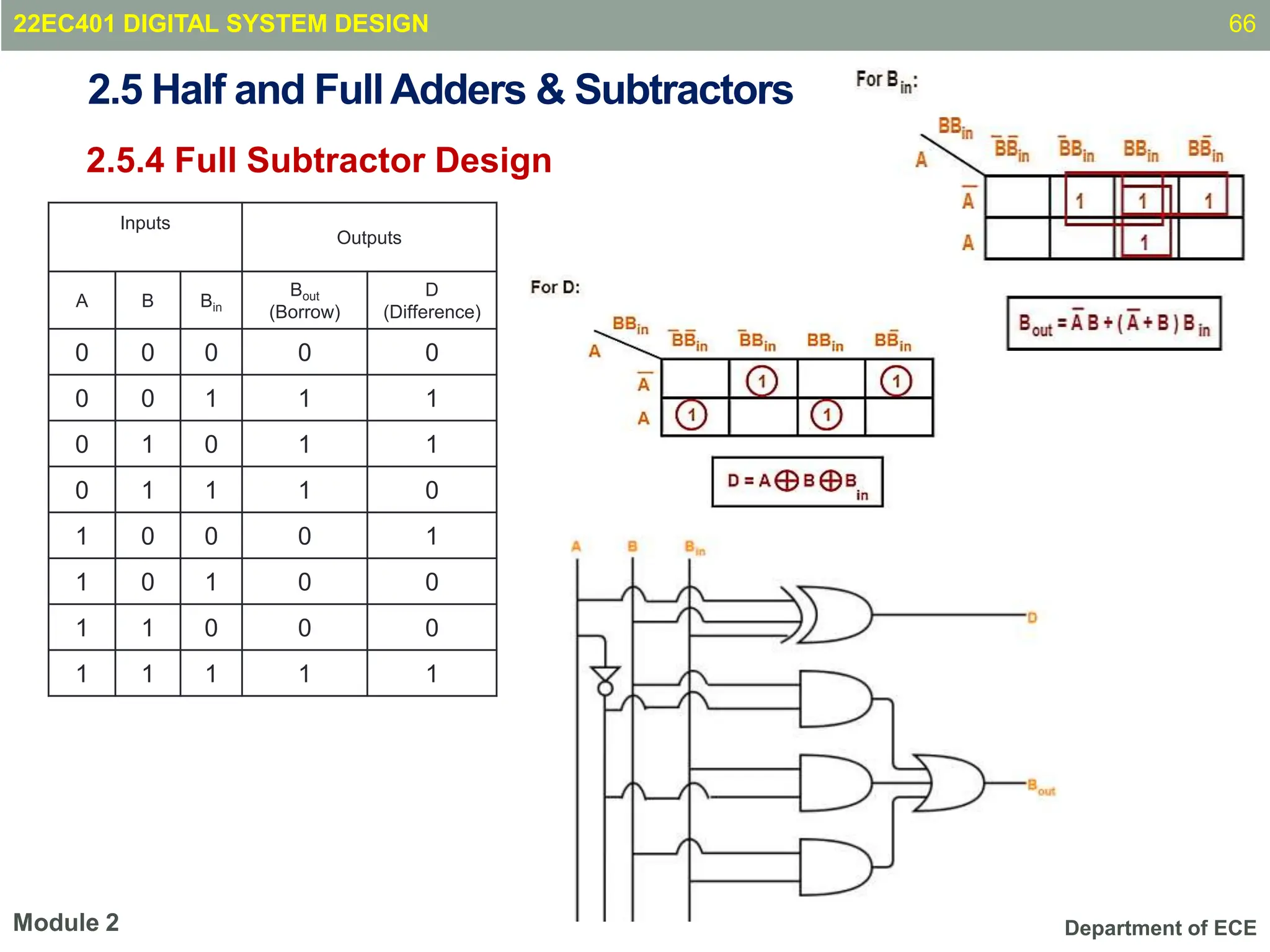

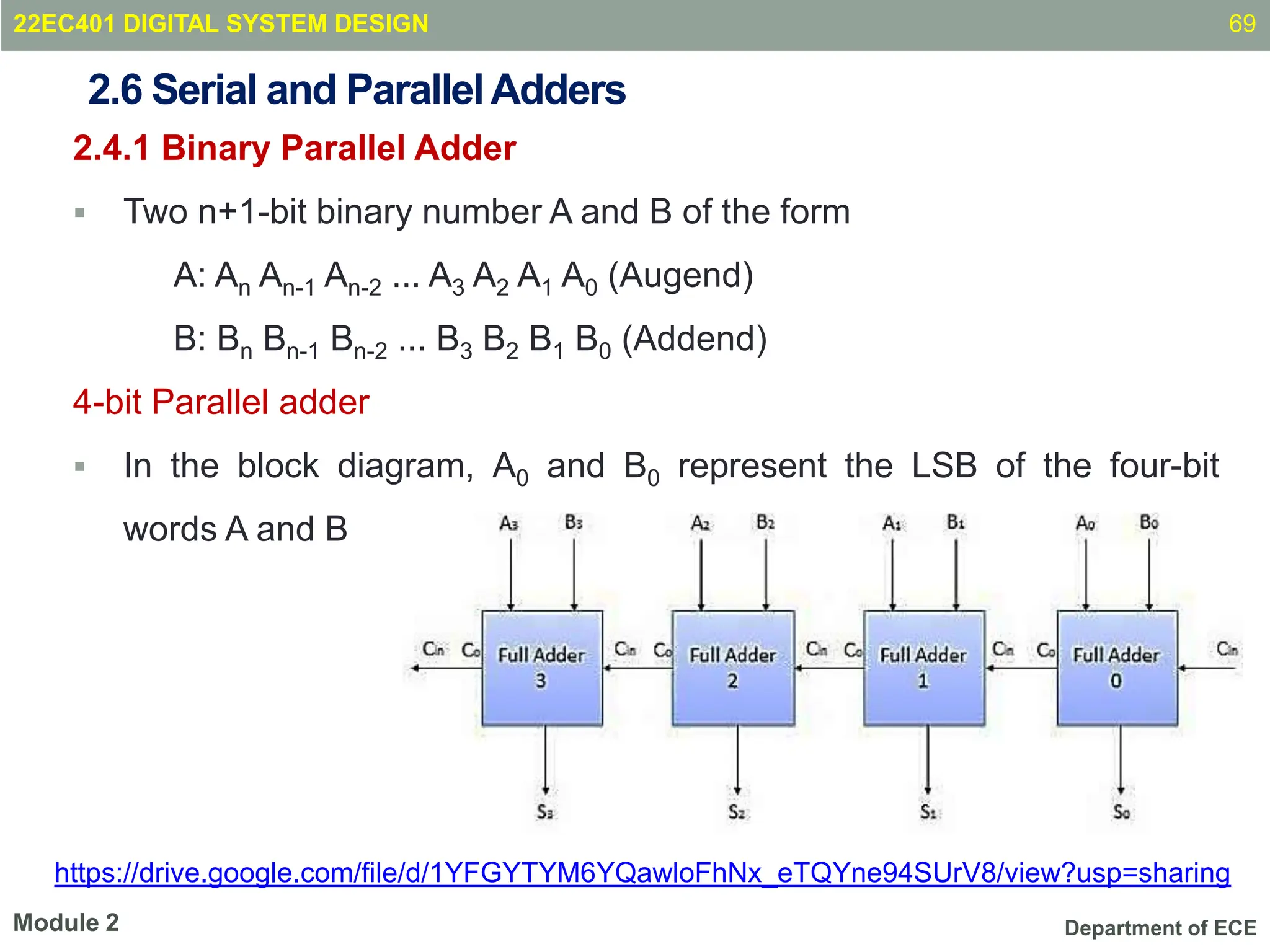

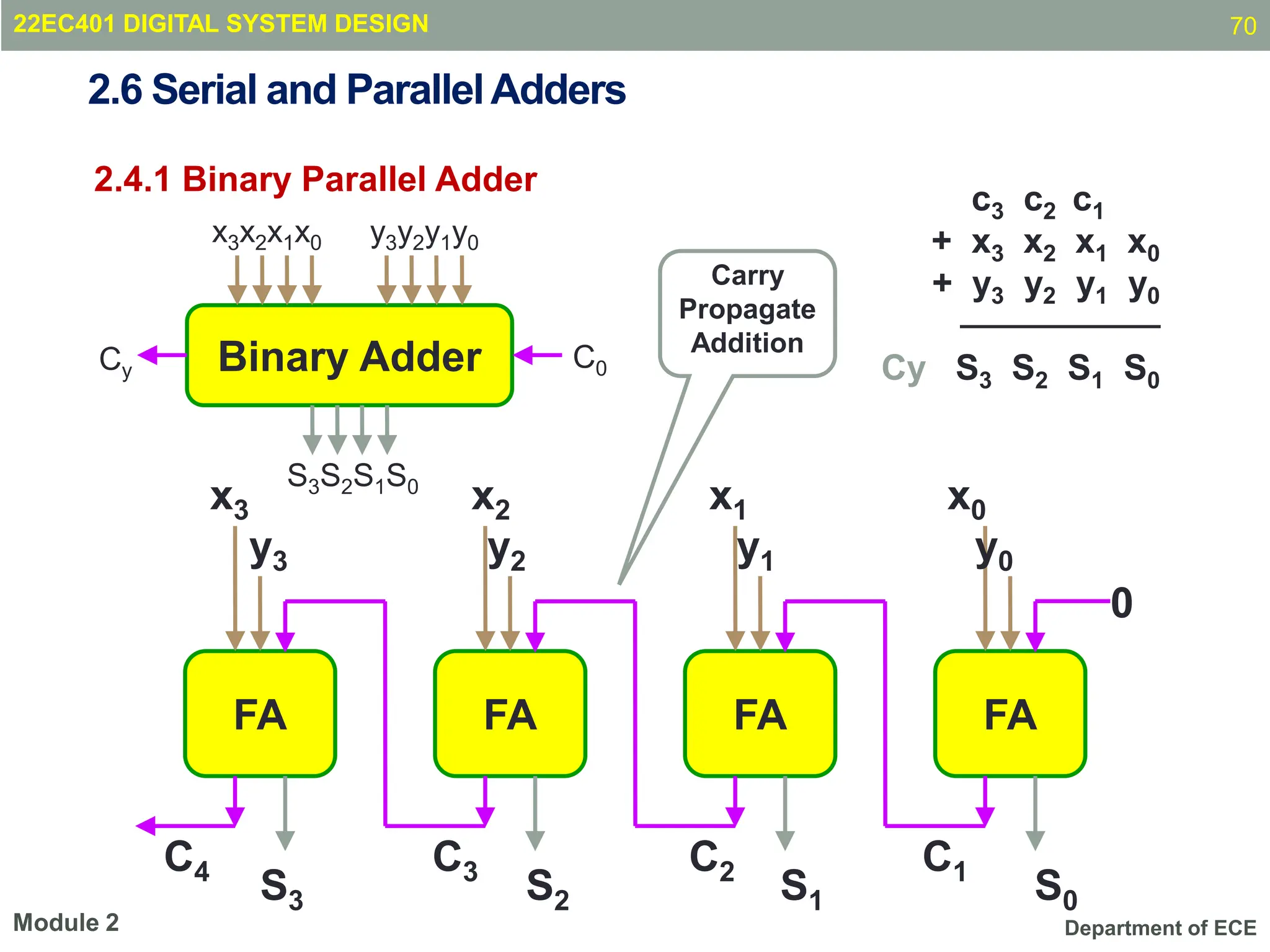

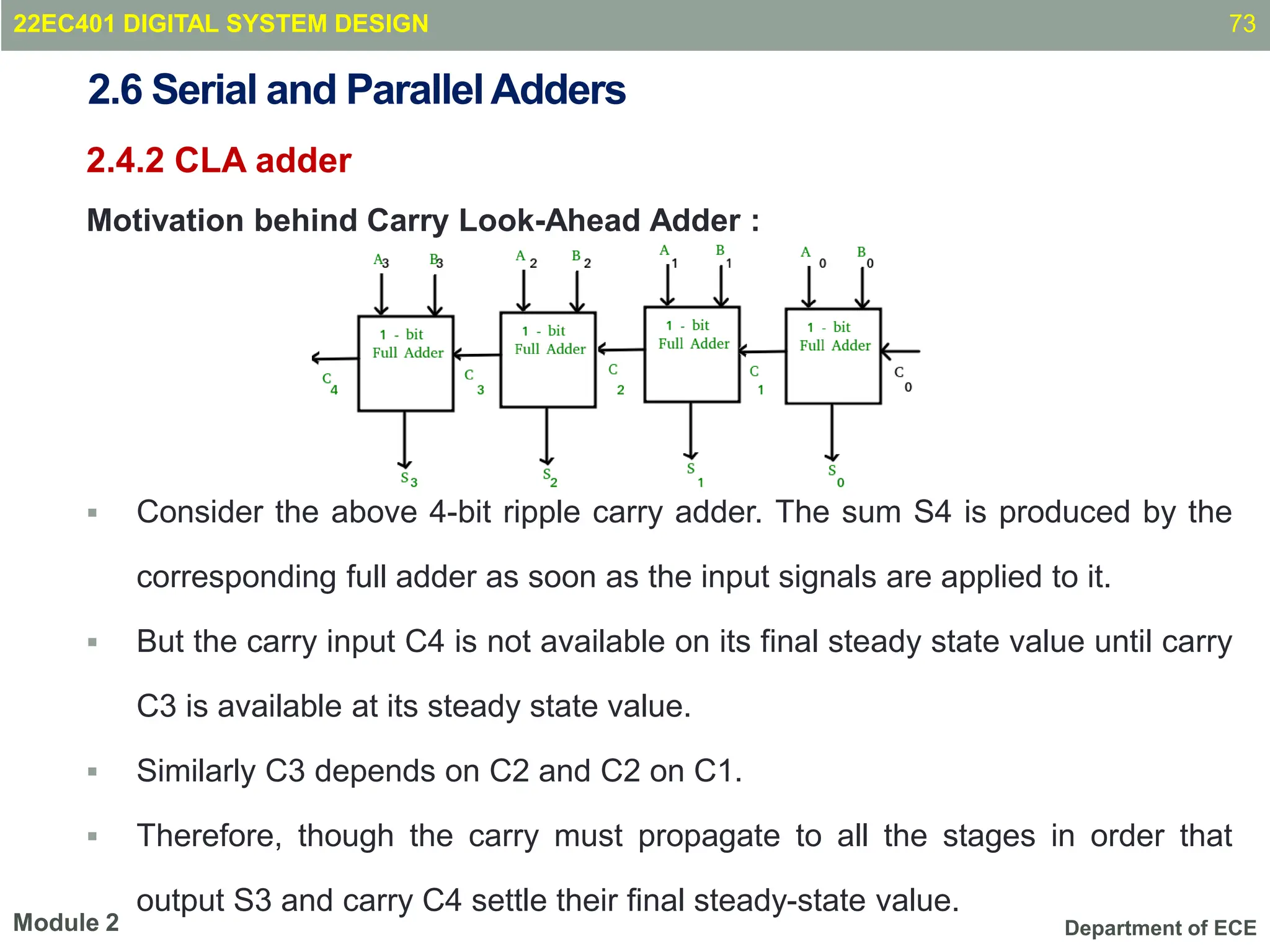

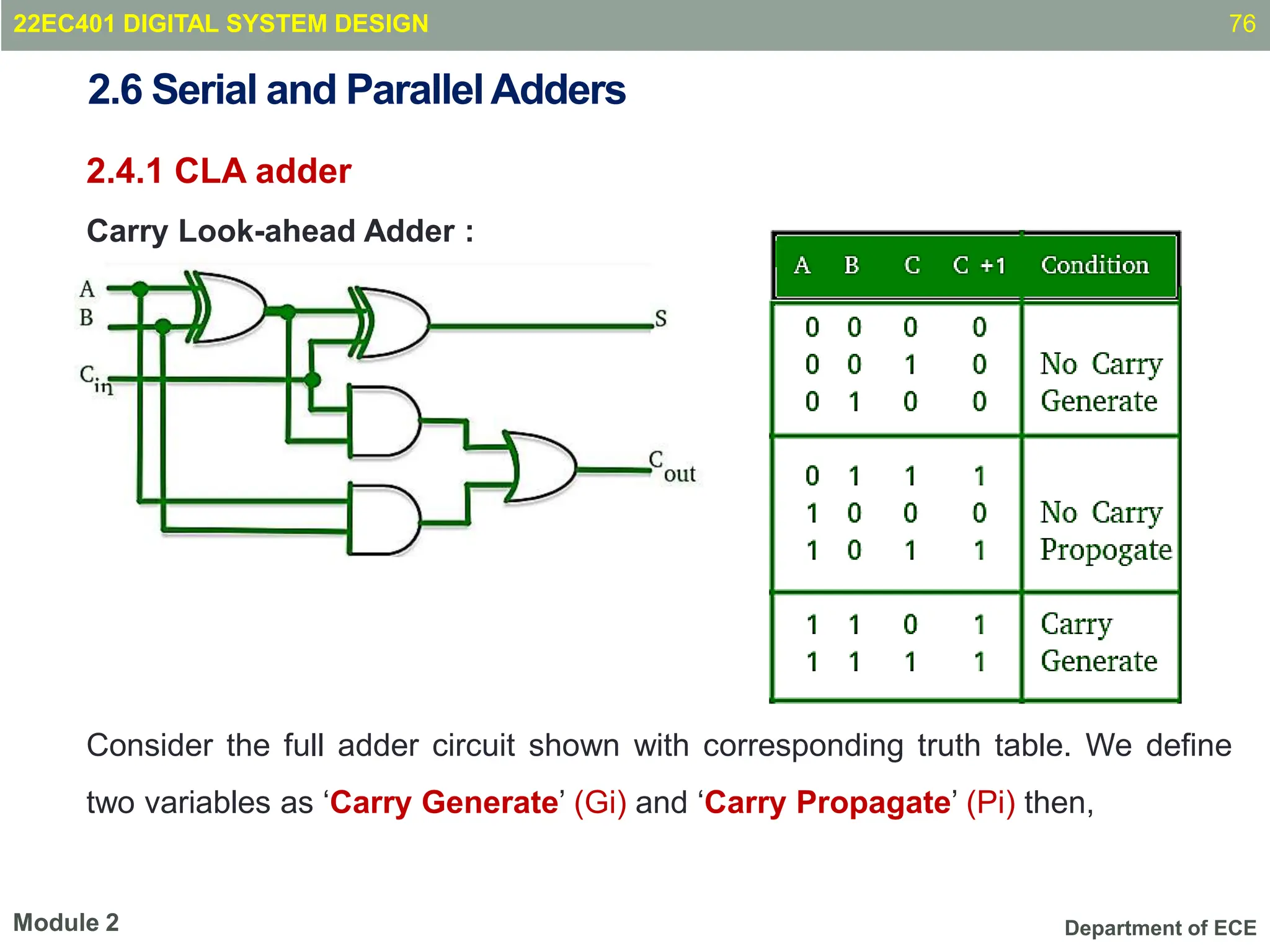

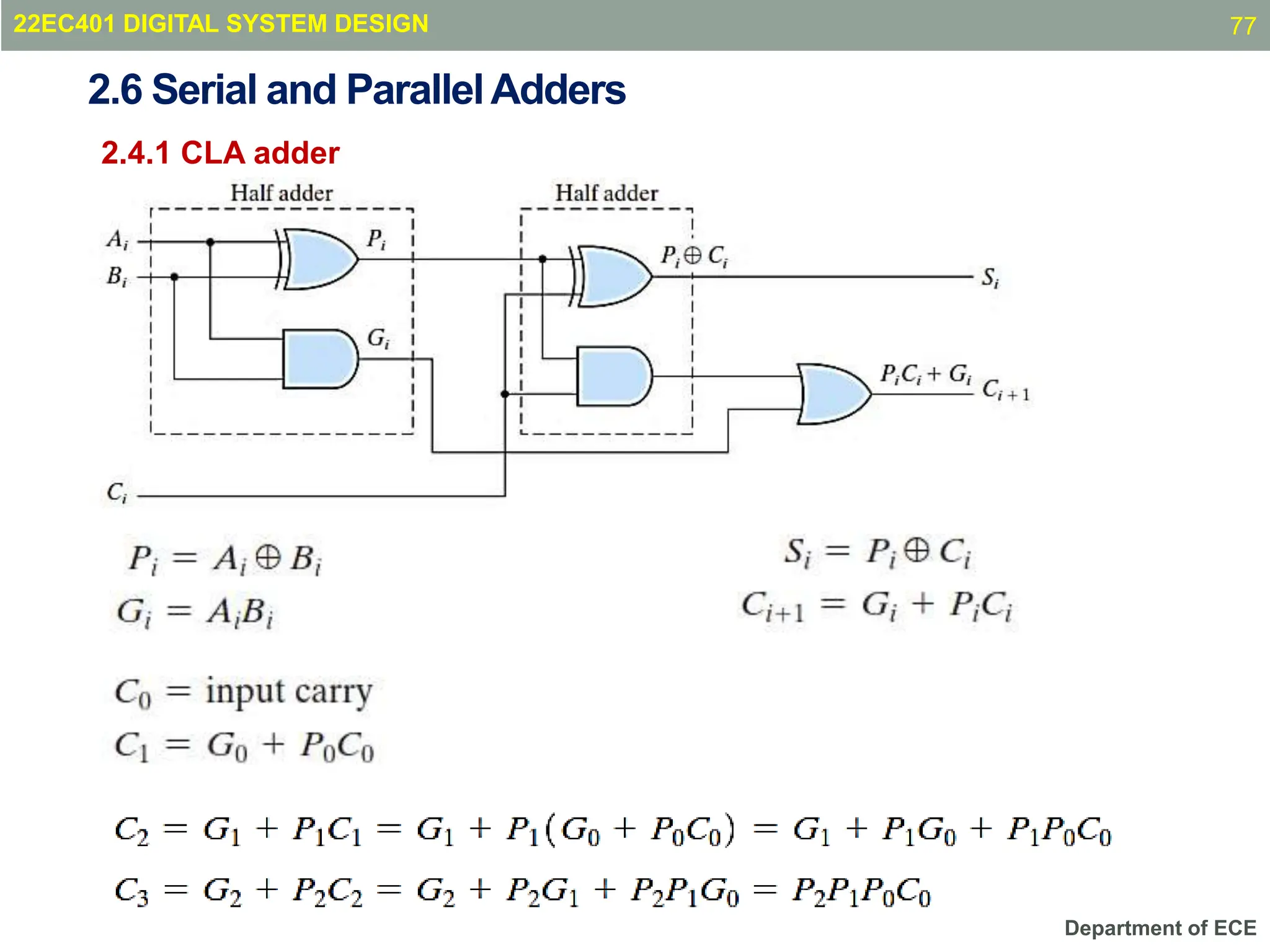

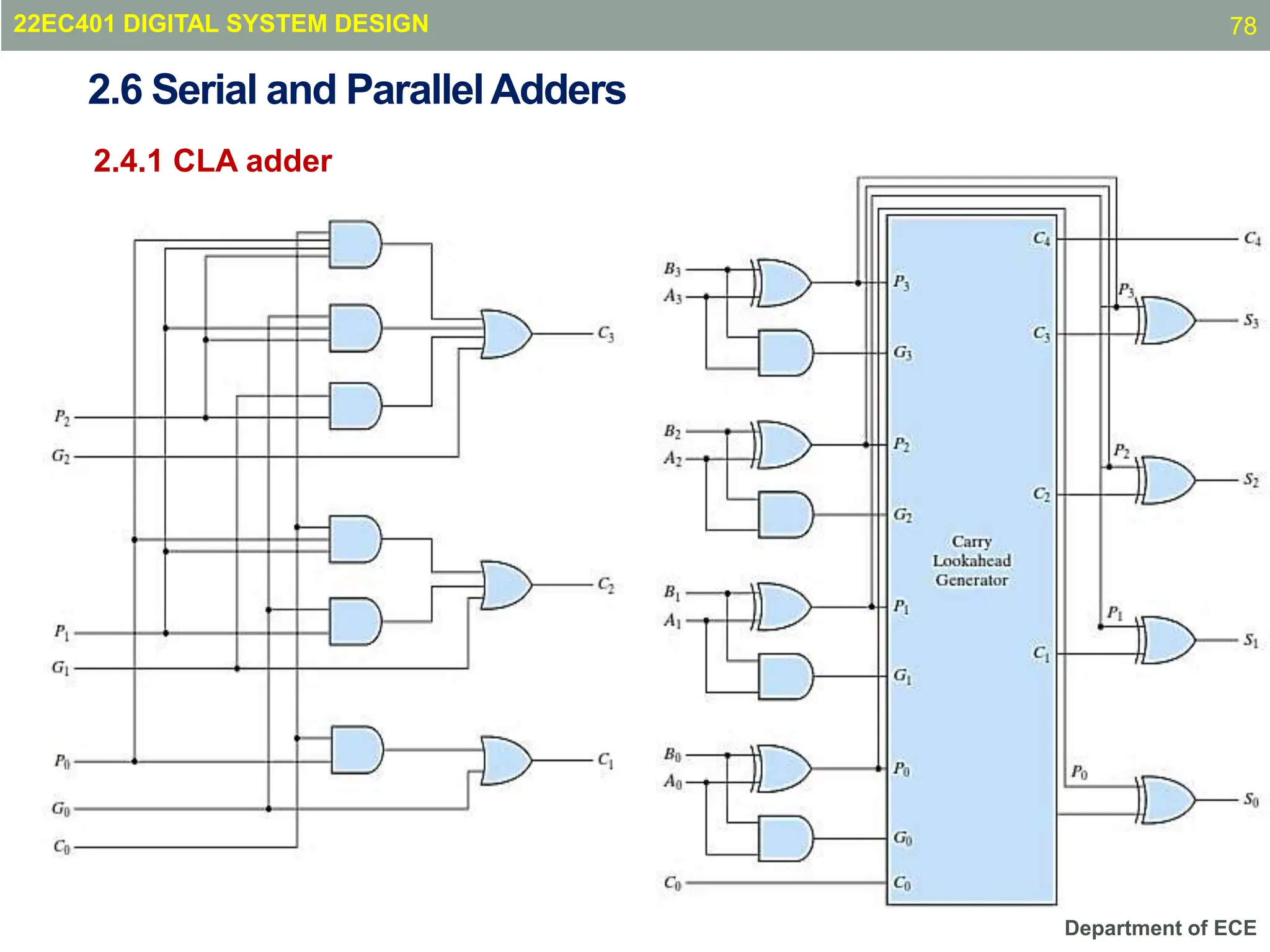

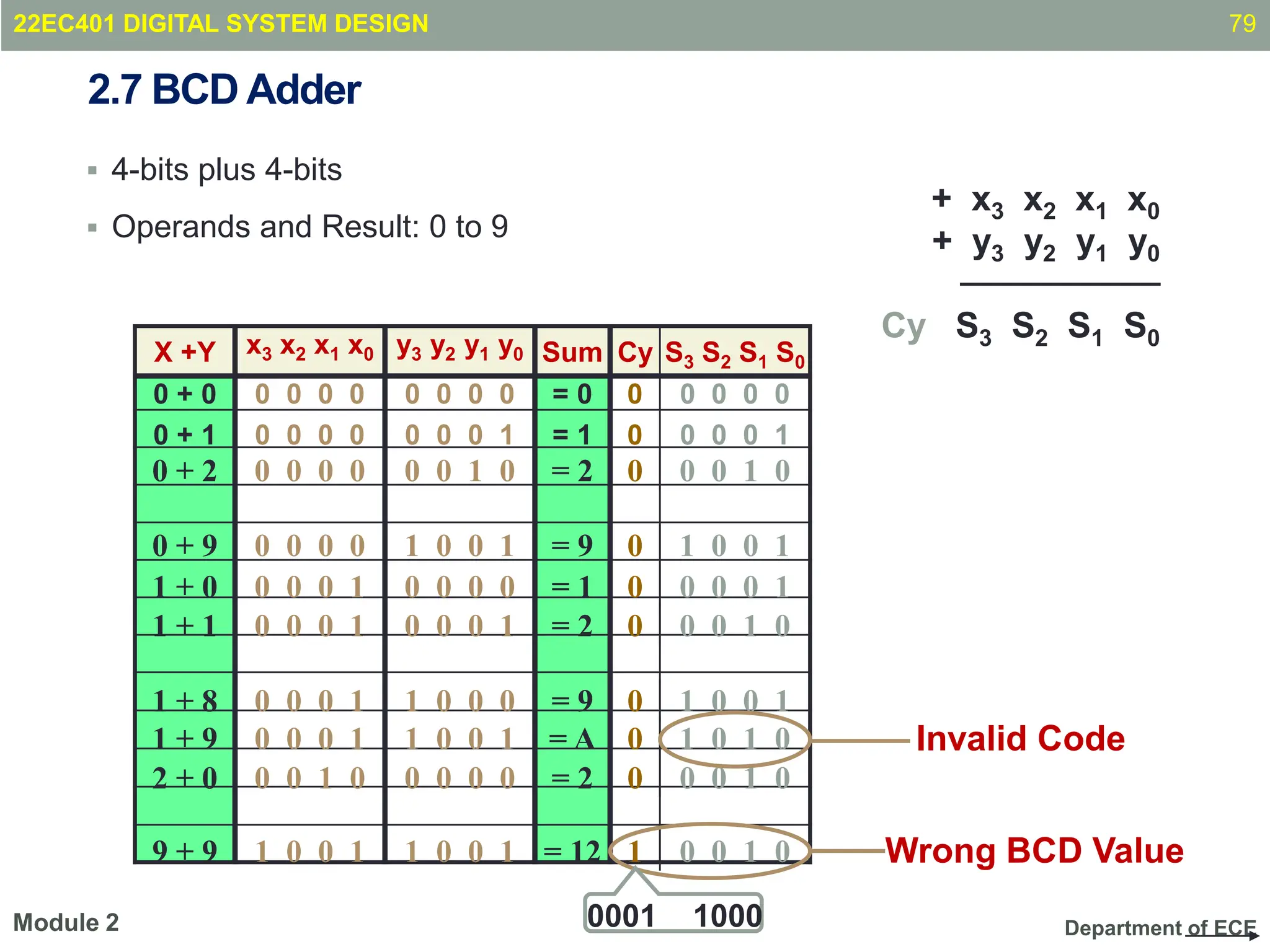

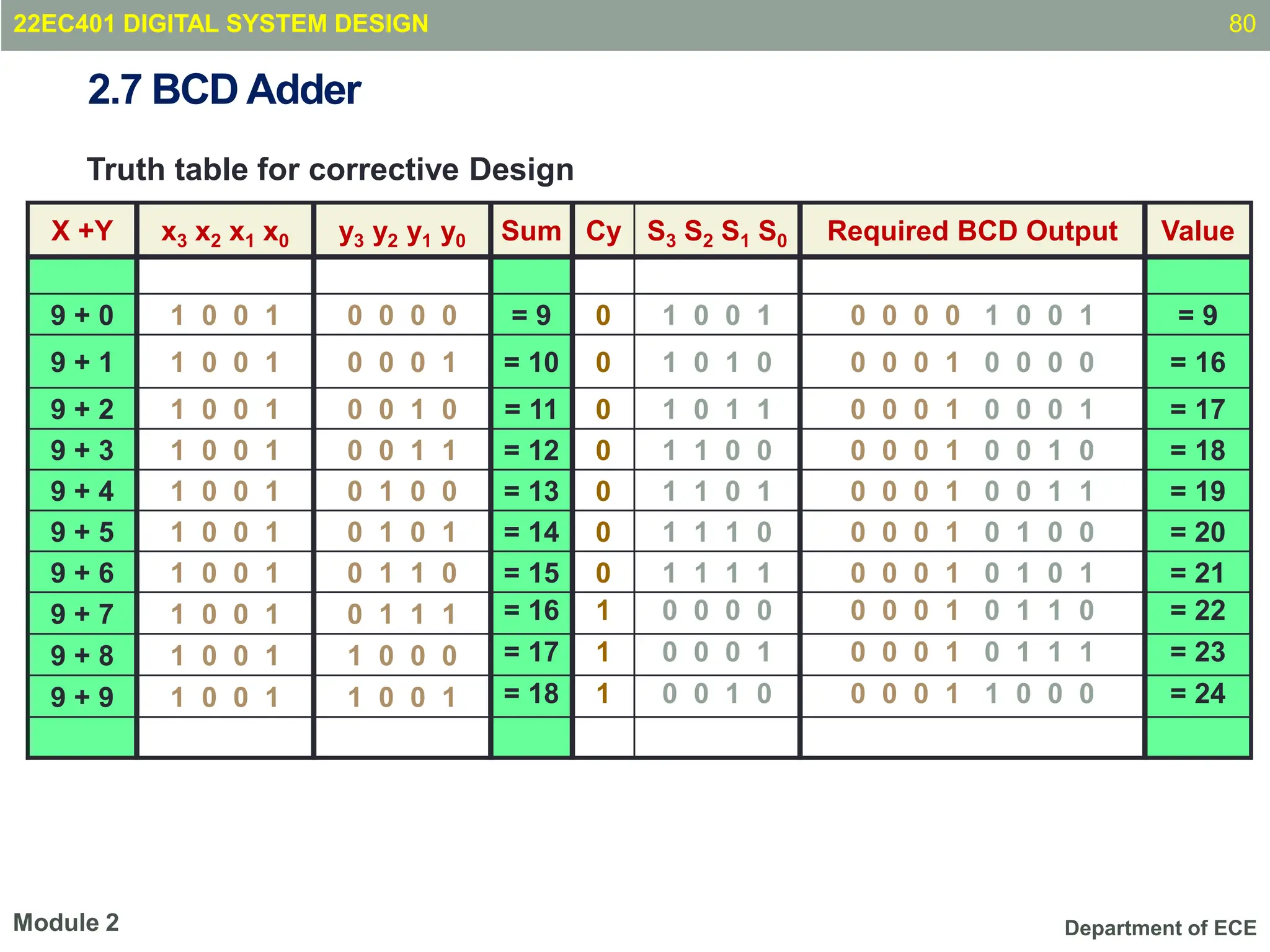

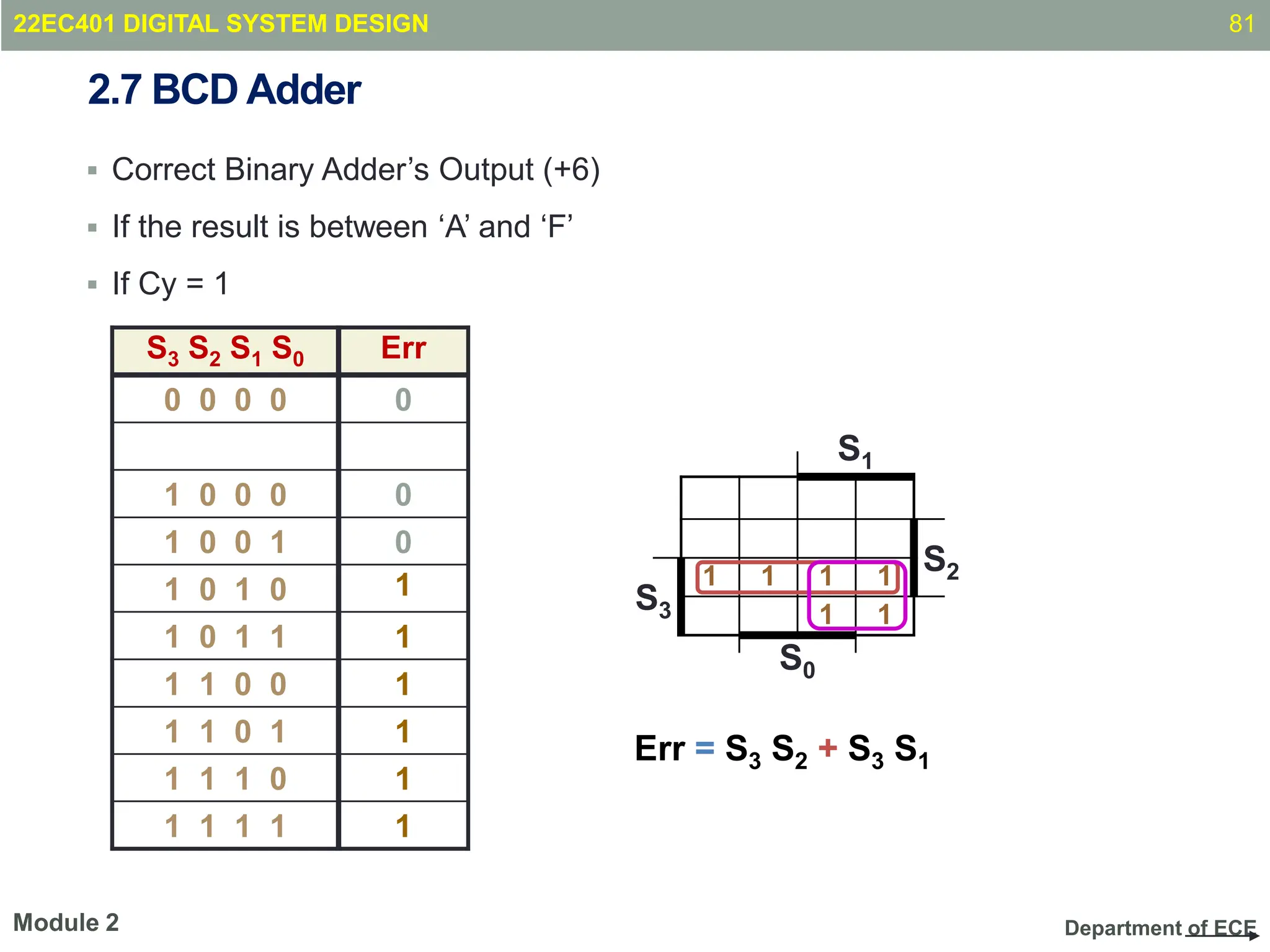

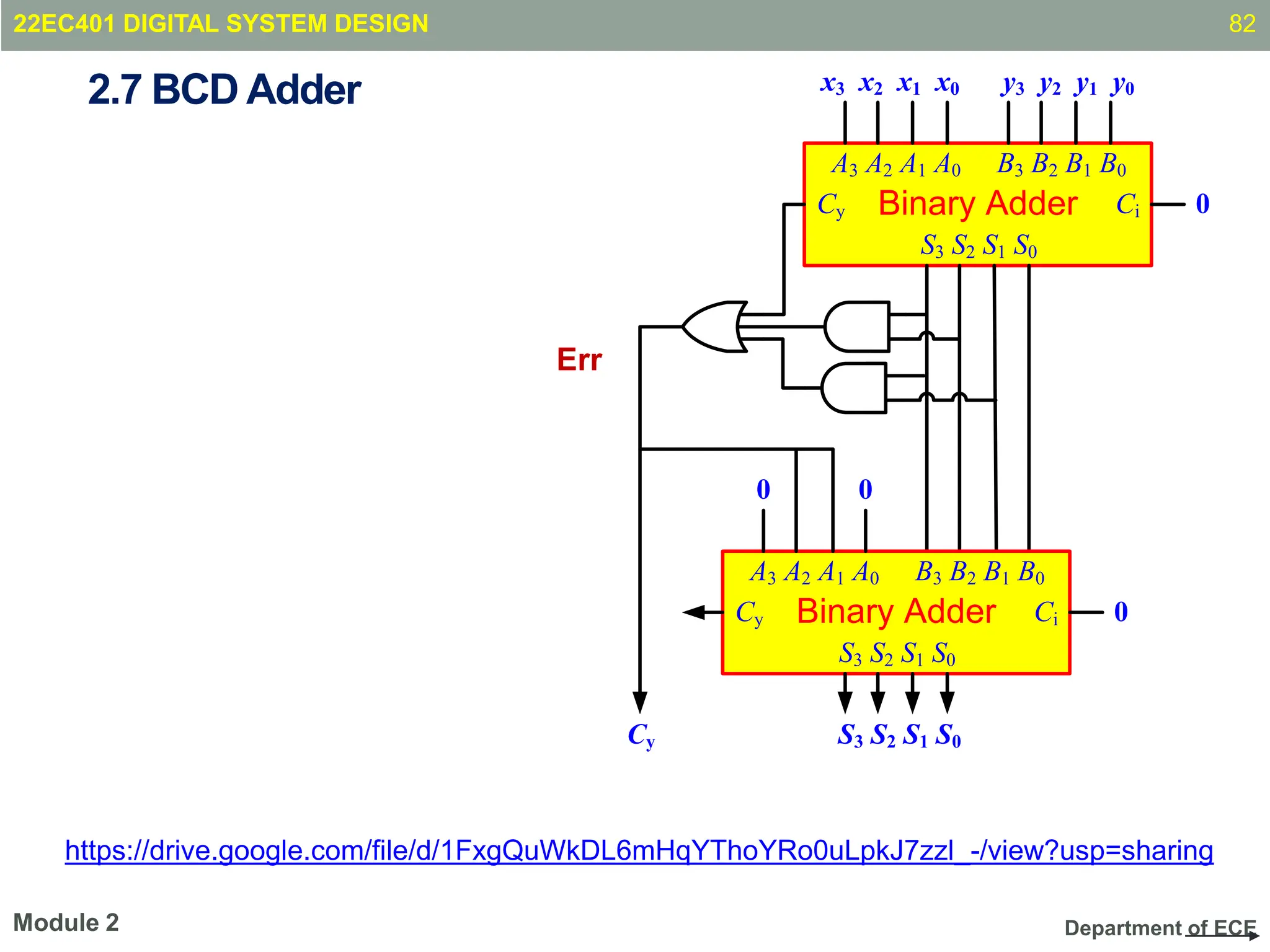

The document outlines the syllabus for the Digital System Design course (22EC401) at the Department of ECE for the academic year 2023-2024, focusing on logic simplification, logic families, and MSI combinational logic circuits. Key topics include Boolean algebra, Karnaugh maps, logic families, magnitude comparators, and multiplexers, detailing their functionality and applications. The document emphasizes the importance of understanding these concepts for effective circuit design and integration.