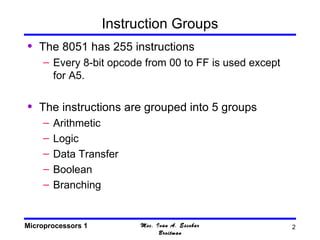

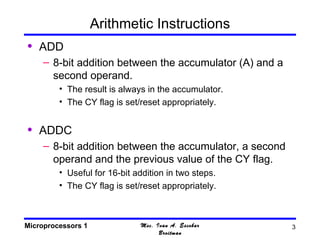

The document describes the instruction set of the 8051 microprocessor. It is divided into 5 groups: arithmetic, logical, data transfer, boolean, and branching instructions. The arithmetic instructions include ADD, ADDC, DA for decimal adjust, and MUL/DIV for multiplication and division. Logical instructions include ANL, ORL, XRL. Data transfer instructions move data between registers and memory like MOV, PUSH, POP. Boolean instructions manipulate individual bits. Branching instructions include unconditional jumps, calls, returns, and conditional jumps.