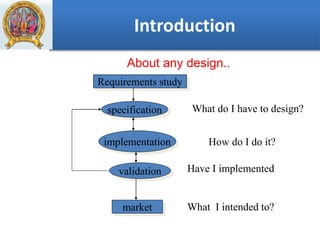

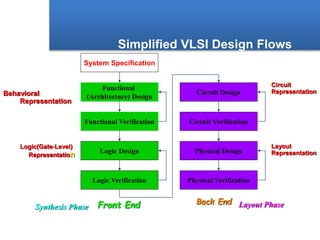

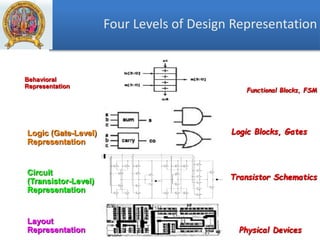

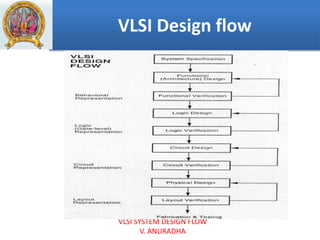

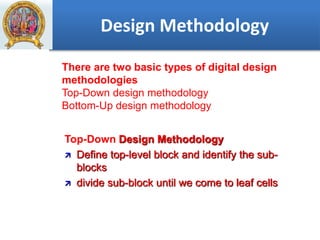

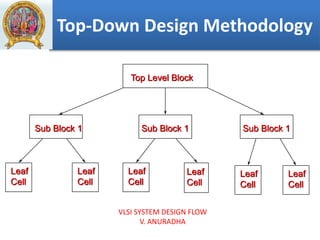

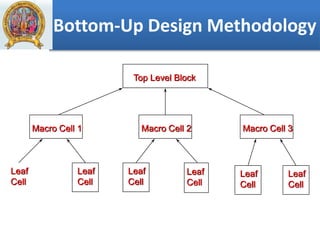

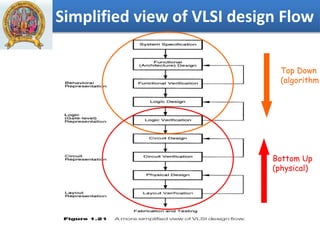

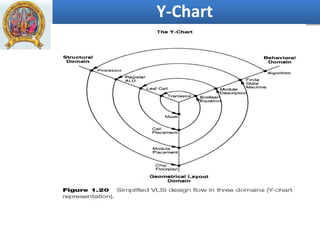

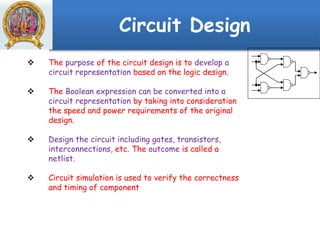

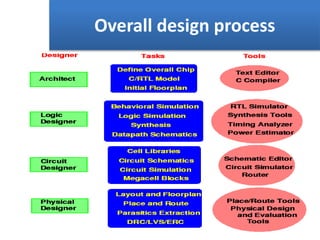

VLSI refers to microchips containing hundreds of thousands of transistors used for computer processing. The VLSI design process begins with specifying the system and breaks it down into functional blocks and logic gates. It involves multiple phases of design representation from behavioral to layout. A top-down or bottom-up methodology is used, with both combined in modern design. The goal is to take a system specification through functional, logic, circuit, and physical design stages to produce a packaged chip.