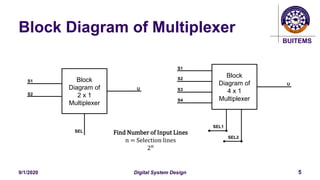

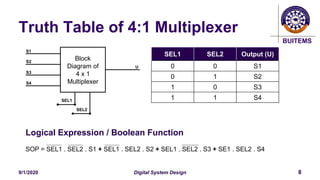

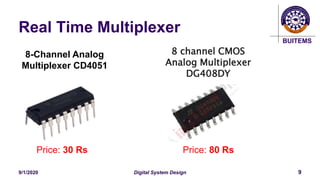

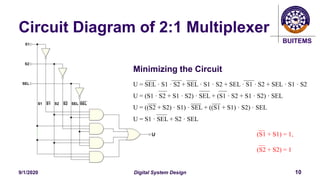

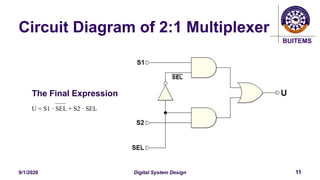

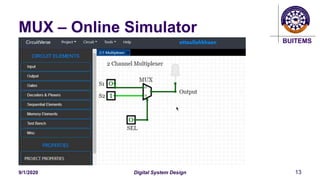

The document provides an overview of multiplexers, specifically the 2x1 and 4x1 types, explaining their function as devices that select one input from multiple sources for output. It includes details on block diagrams, truth tables, timing diagrams, and real-time applications of multiplexers. Additionally, it offers examples and circuit diagrams for implementation, along with pricing for specific multiplexer models.