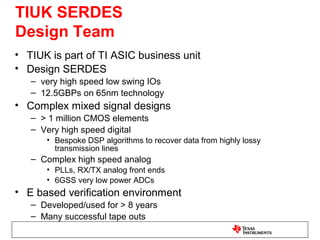

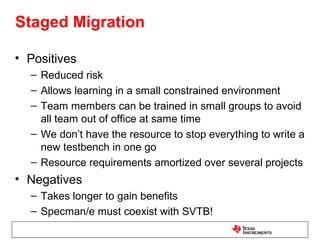

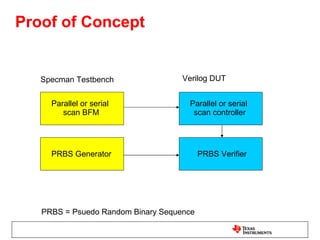

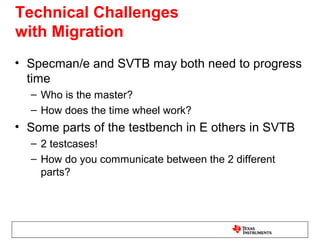

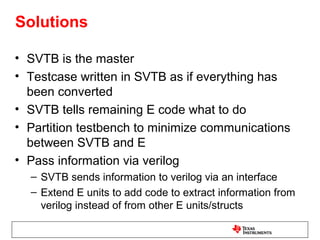

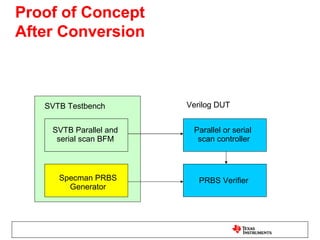

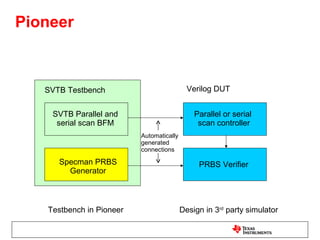

This document describes a case study of a staged migration from e to SystemVerilog at a company designing SERDES chips. It discusses advantages like reduced risk and training staff in small groups. Technical challenges addressed include coordinating simulation timelines and communicating between testbench parts in different languages. Solutions involved making SVTB the master, writing testcases as if fully converted, and using Verilog to pass info between languages. A proof of concept showed the converted approach. Supporting multiple simulators involved using a tool that connects a Pioneer-based SVTB to DUTs in other simulators to avoid lowest common denominator issues.