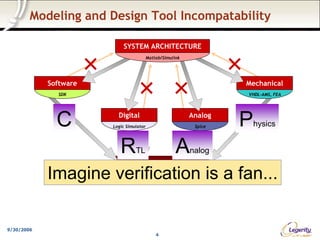

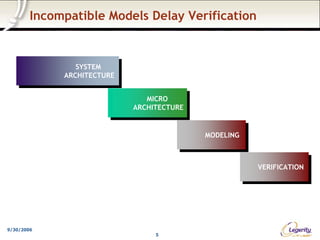

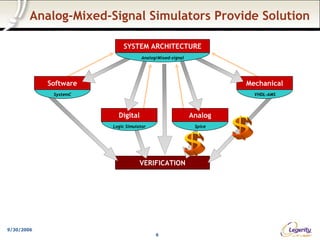

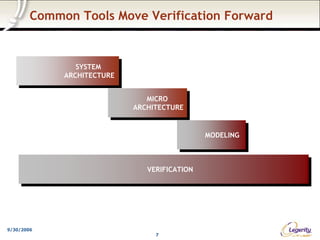

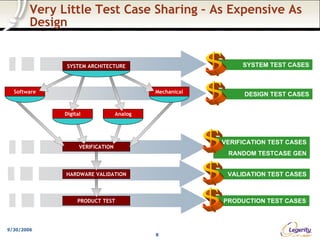

This document discusses challenges with collaboration and reuse in mixed-signal design verification. It notes that using incompatible tools for modeling at different design levels delays verification. It suggests that using analog/mixed-signal simulators with common modeling languages and virtual labs with standardized devices and behaviors could improve collaboration, reuse of test cases, and speed up the verification process.