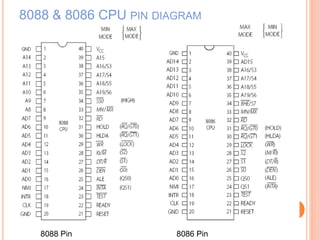

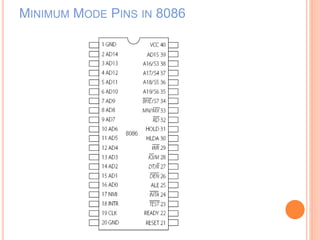

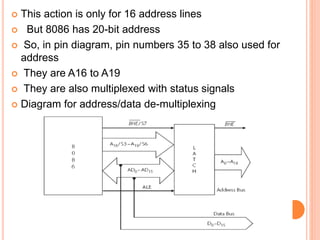

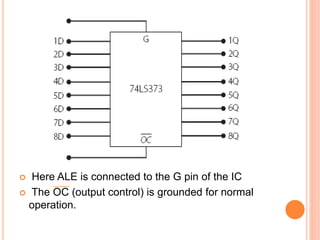

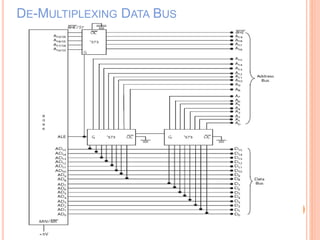

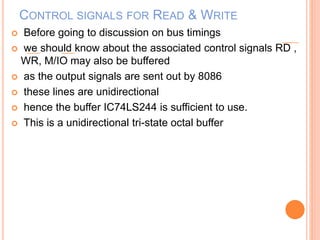

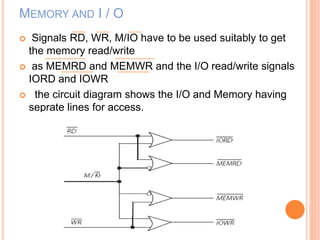

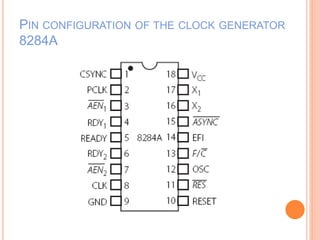

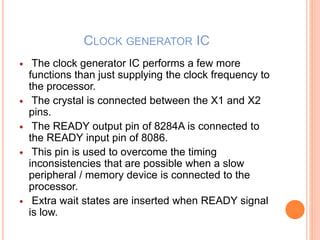

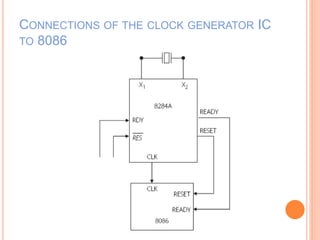

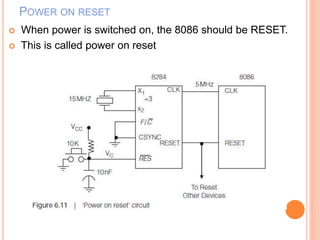

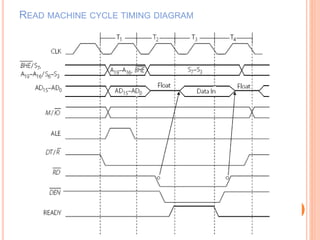

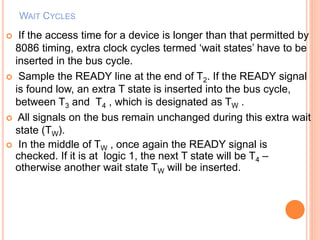

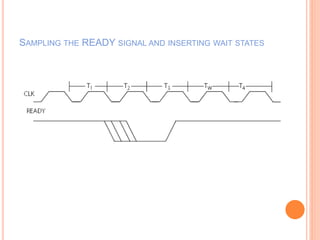

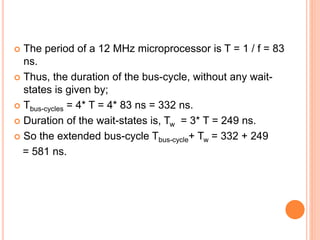

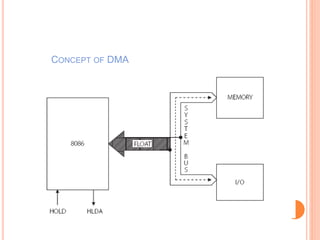

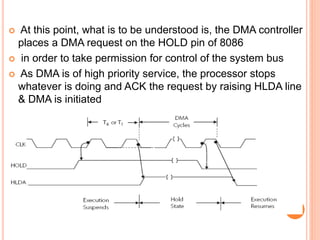

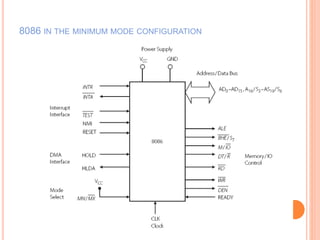

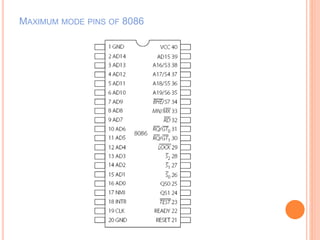

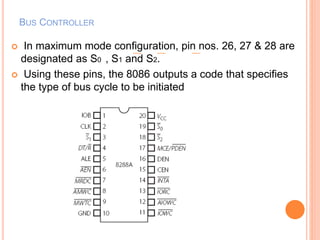

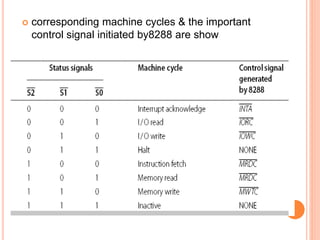

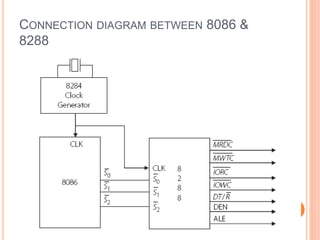

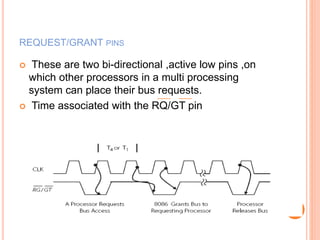

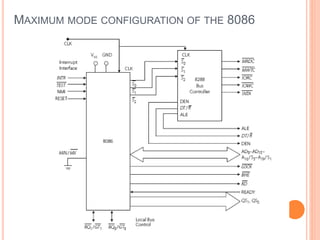

This document discusses the hardware structure and pin configurations of the Intel 8086 and 8088 microprocessors. It describes the differences between the 8086 and 8088, including their data bus widths, instruction queues, and specific pin functions. The pin diagrams and functions of pins in both minimum and maximum modes are explained. Key concepts covered include address/data demultiplexing, bus cycles, control signals, clock generation, and interrupt handling. Wait states, direct memory access, and the roles of the bus controller IC and request/grant pins in maximum mode configurations are also summarized.