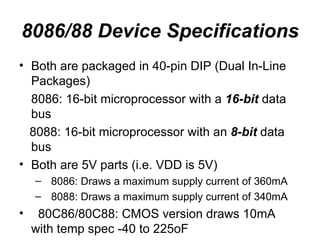

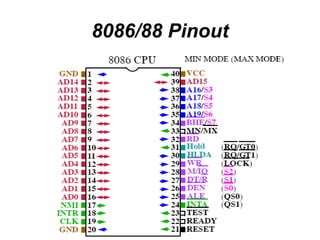

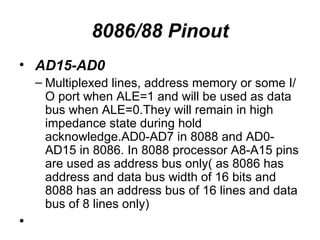

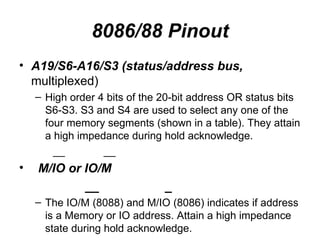

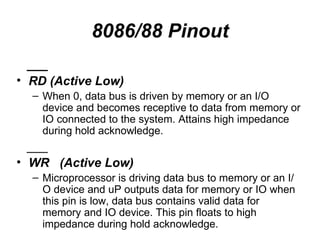

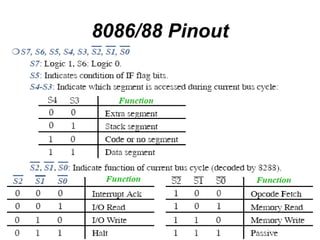

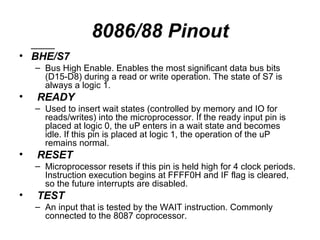

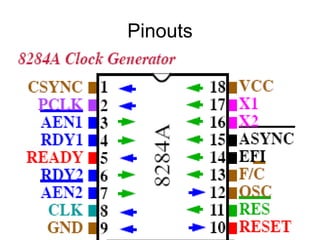

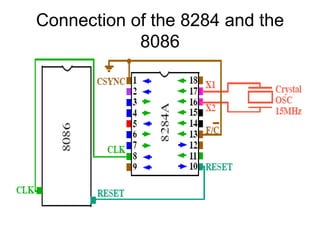

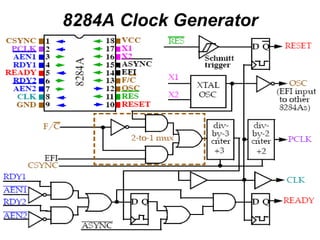

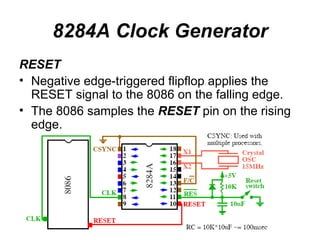

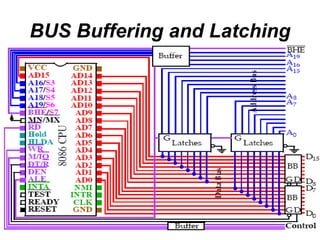

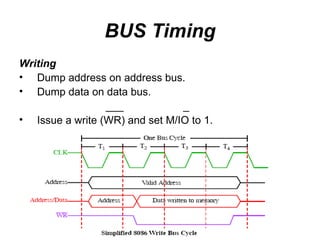

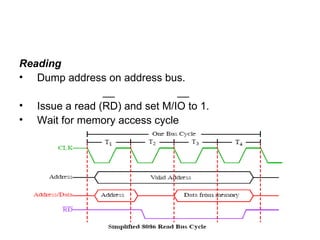

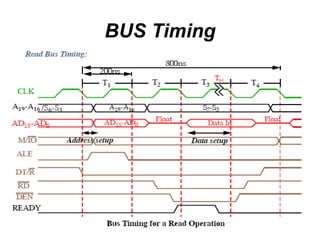

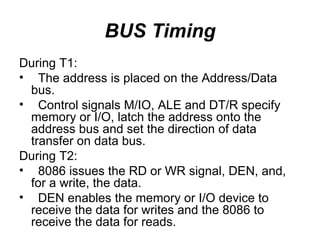

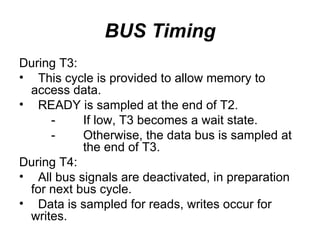

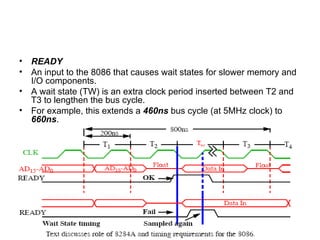

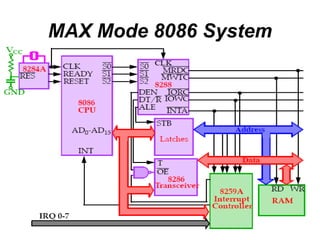

The document discusses specifications and pinouts of the 8086 and 8088 microprocessors. It describes that both are 16-bit processors packaged in 40-pin DIP packages, with the 8086 having a 16-bit data bus and the 8088 having an 8-bit data bus. It also discusses the 8284A clock generator chip used with these processors, providing clock signals, reset synchronization and ready synchronization. The document outlines the bus timing of the processors over four clock cycles and how the ready pin inserts wait states for slower memory and I/O components.

![Microprocessor Systems EE351 8086 Chipset Badar-ul-Islam Department of Electrical Engineering NFC-IEFR [email_address]](https://image.slidesharecdn.com/lect-5-100309082234-phpapp02/75/Lect-5-1-2048.jpg)