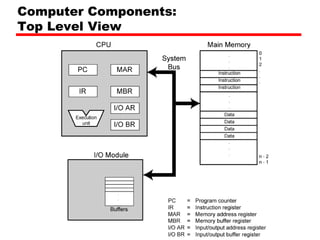

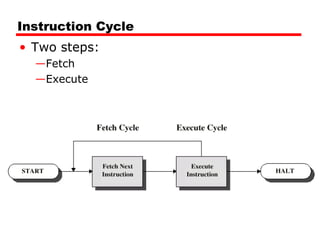

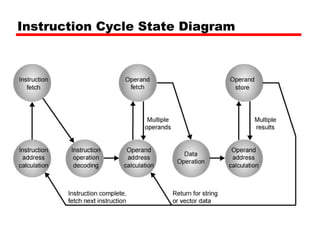

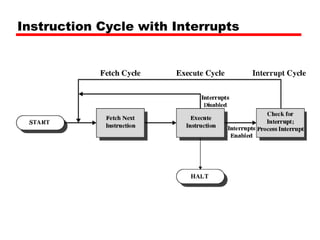

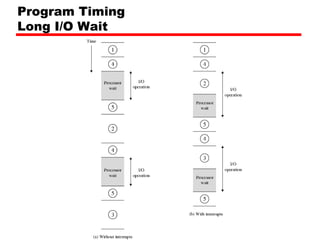

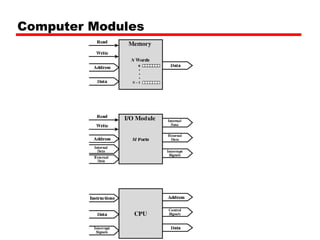

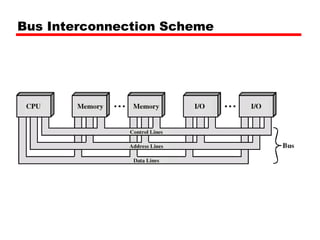

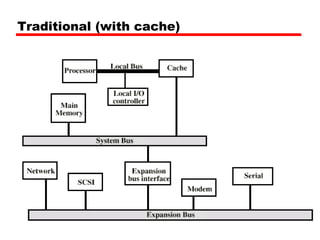

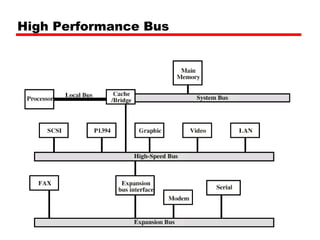

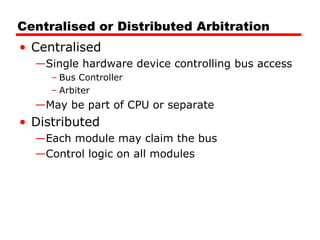

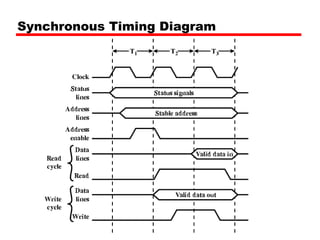

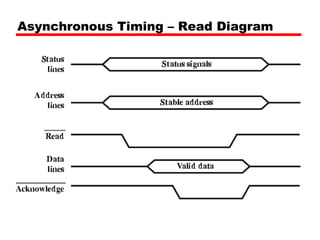

The document discusses the basic components and operation of computers. It describes how a central processing unit (CPU) works with memory and input/output devices using control signals and buses to execute instructions. The CPU fetches and executes instructions in cycles, and can be interrupted by external events using interrupt signals. Buses connect the different components and allow for communication between the CPU, memory, and input/output devices.