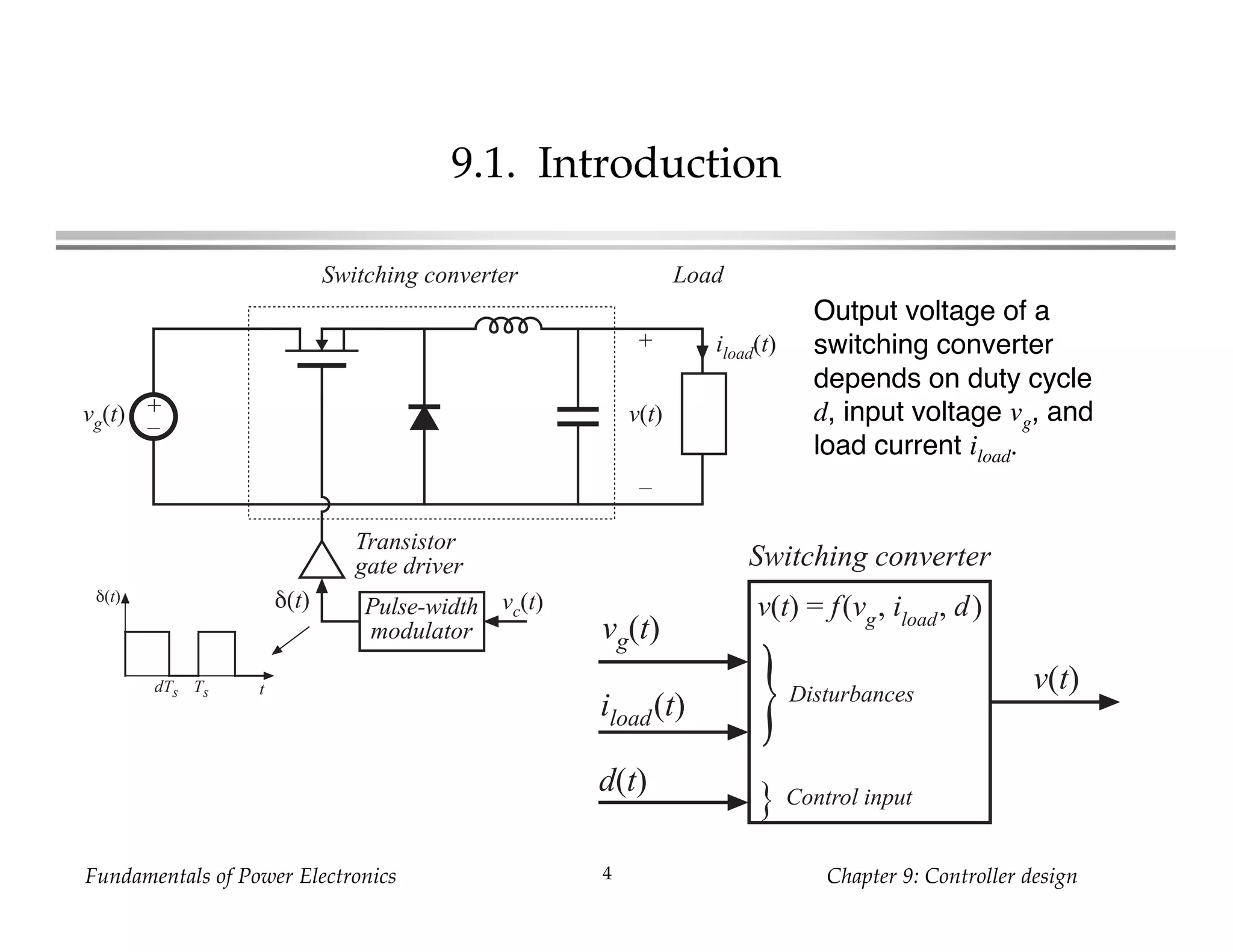

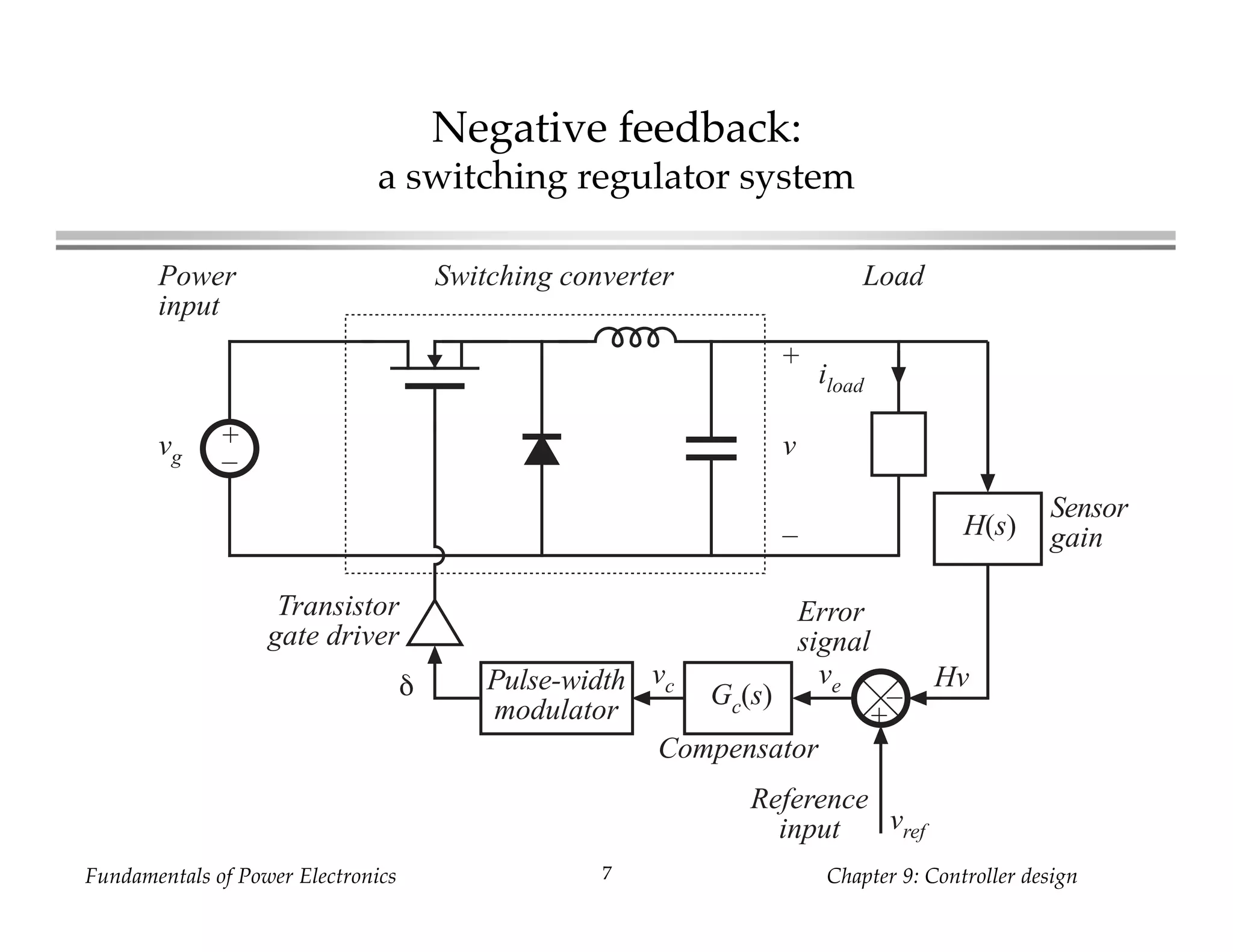

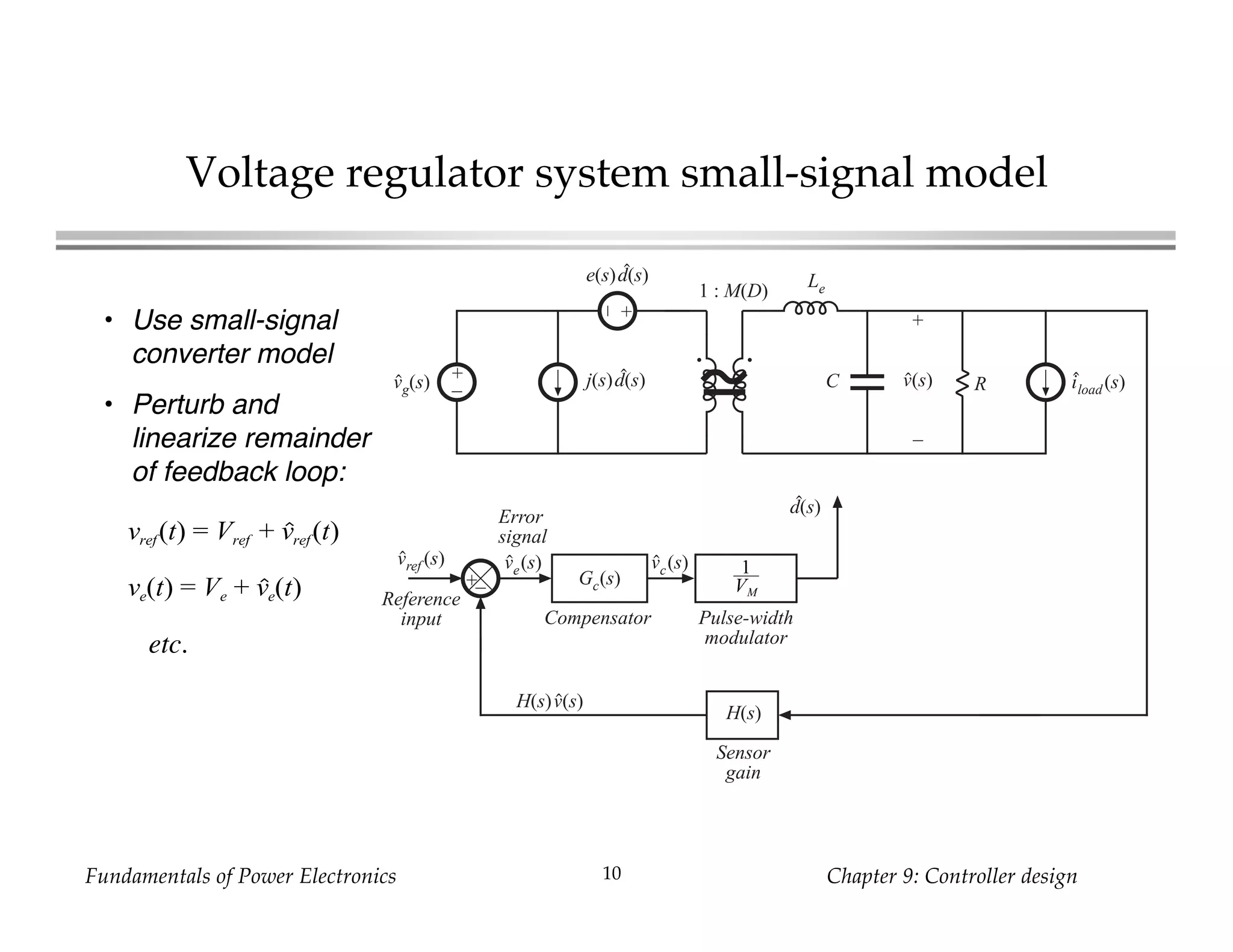

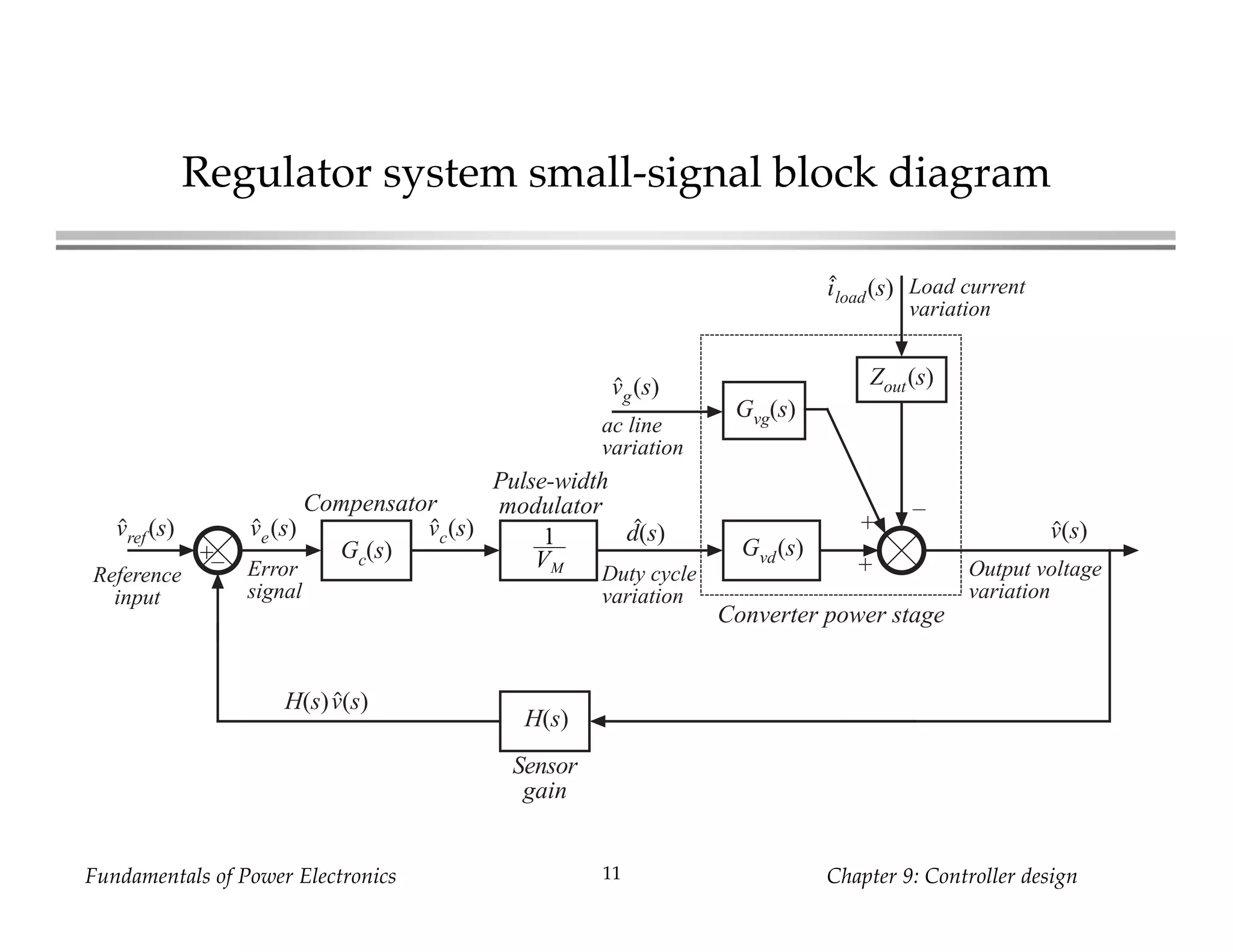

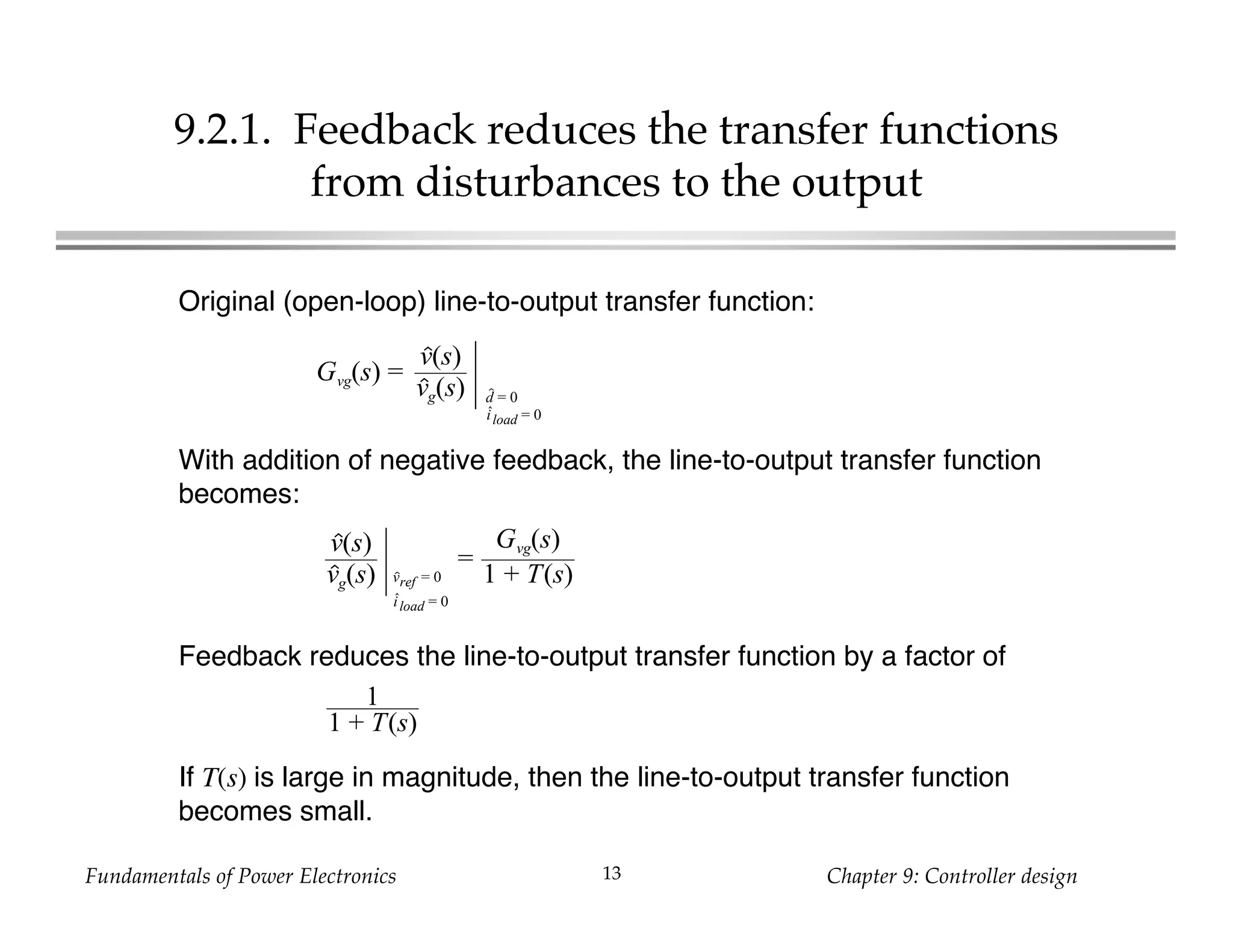

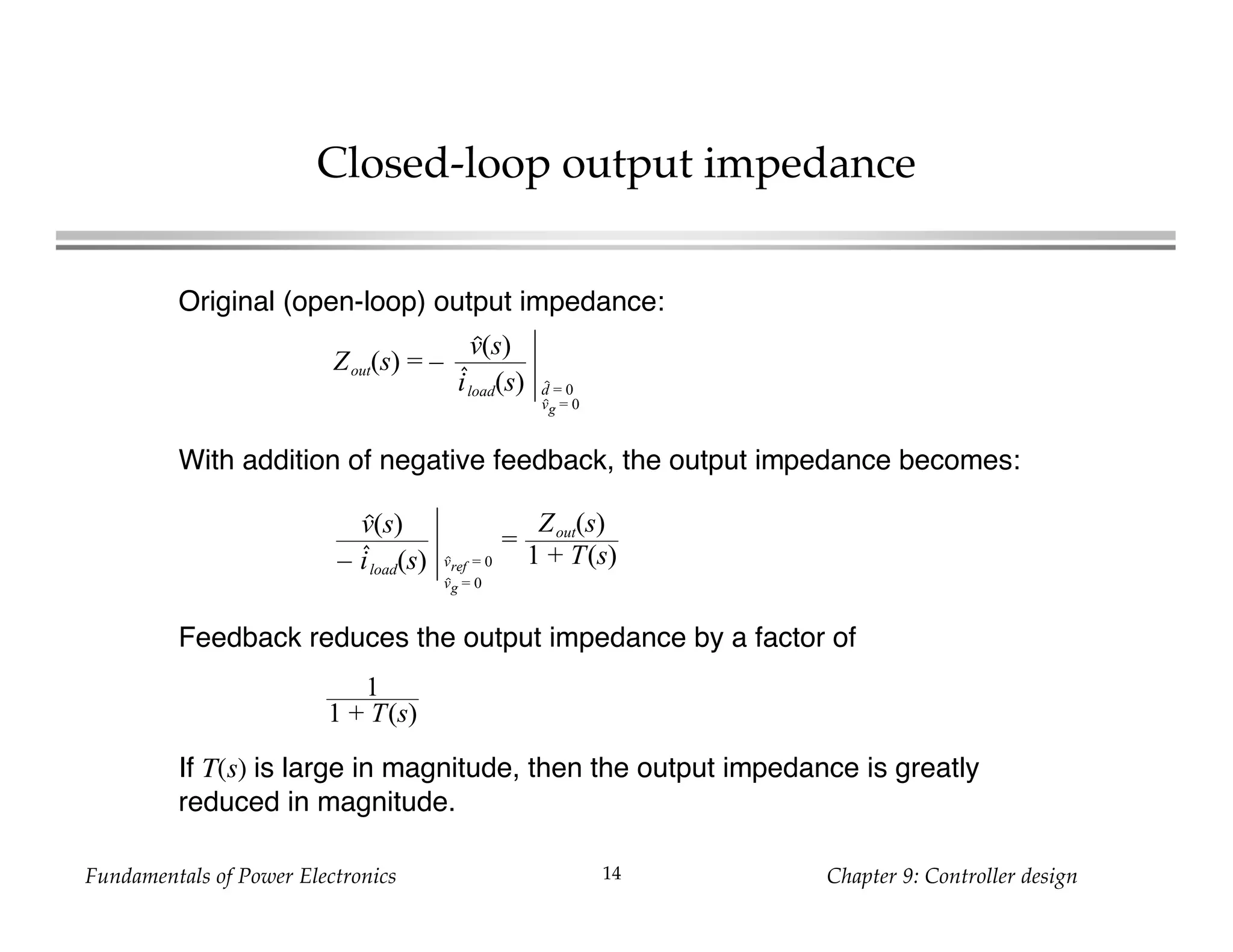

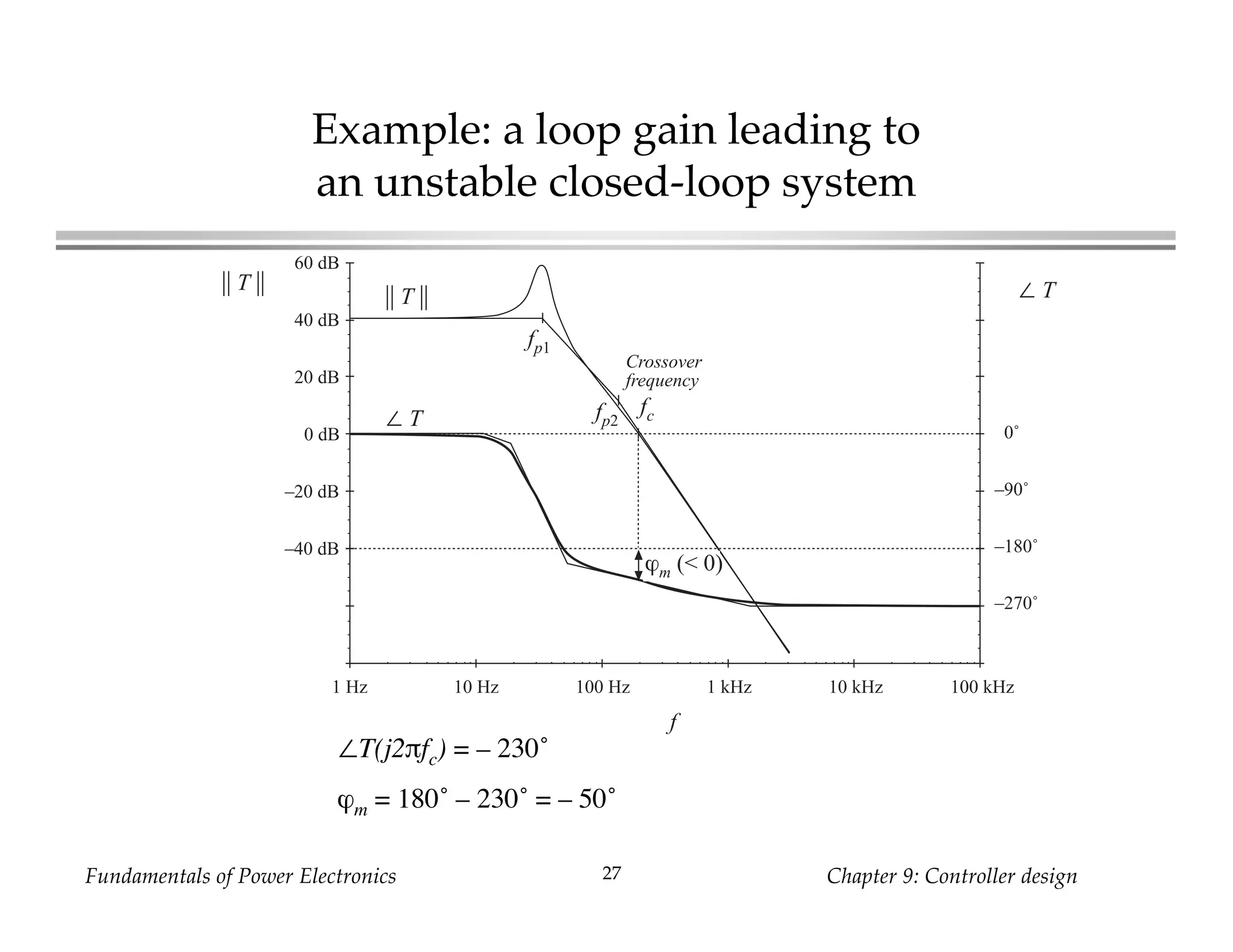

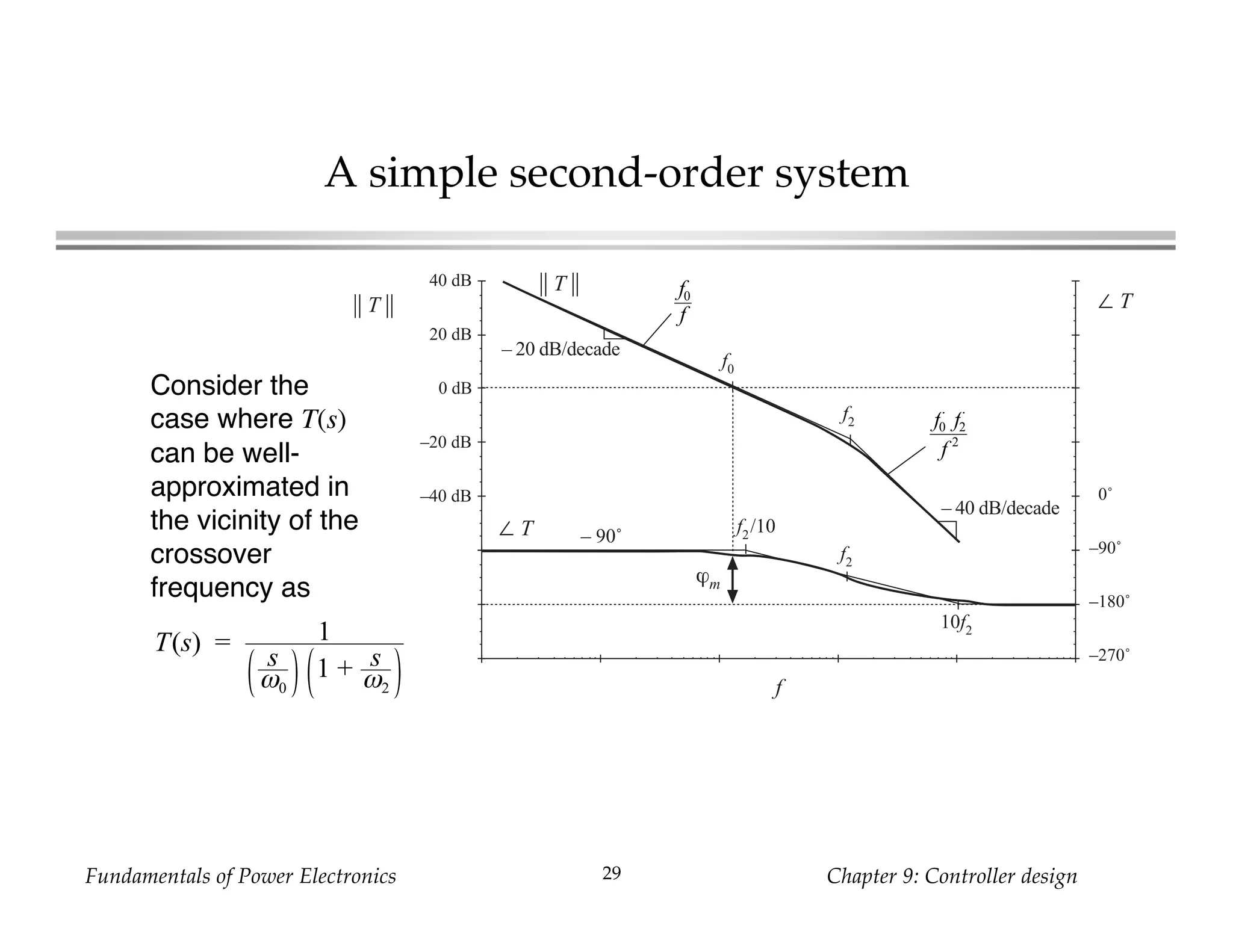

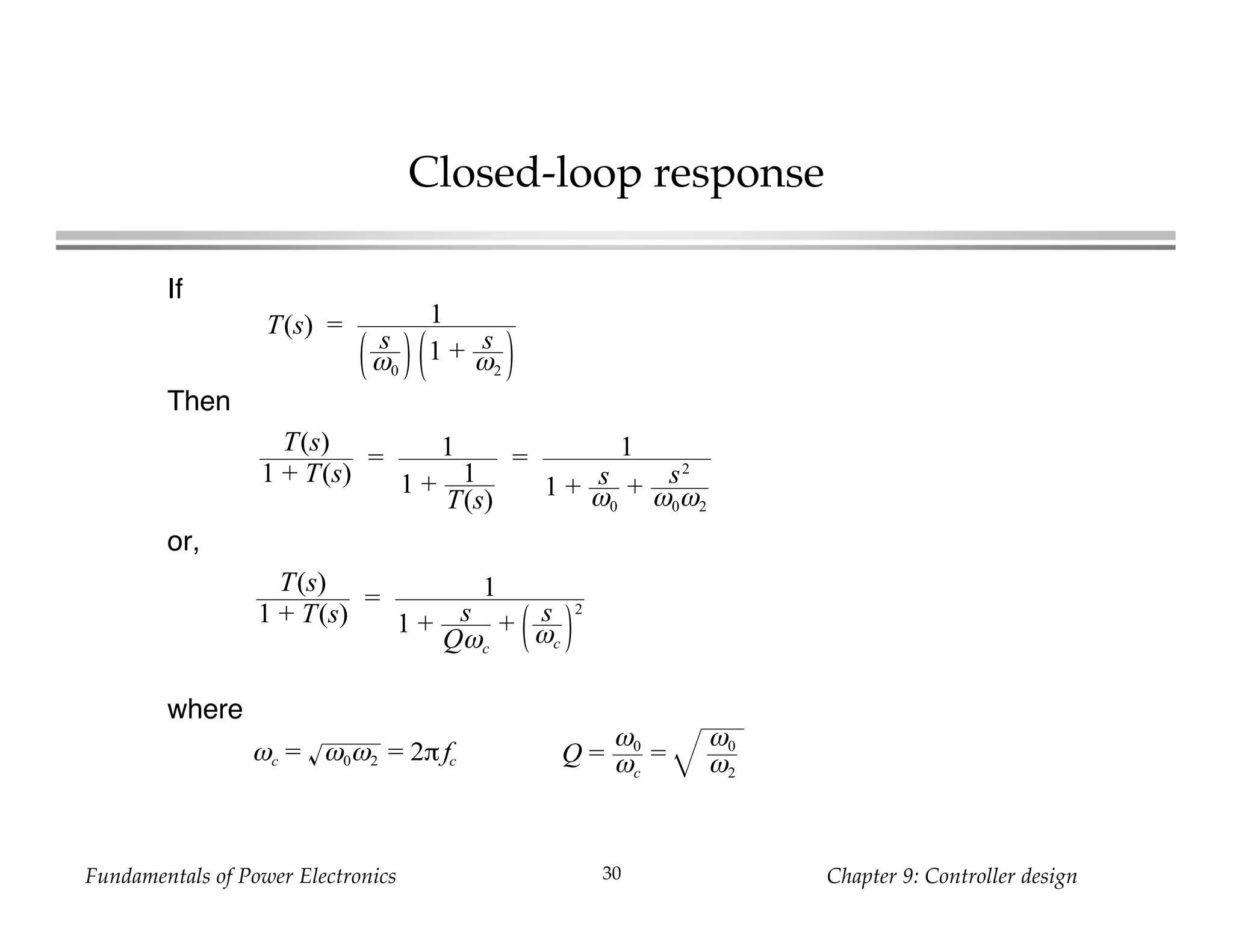

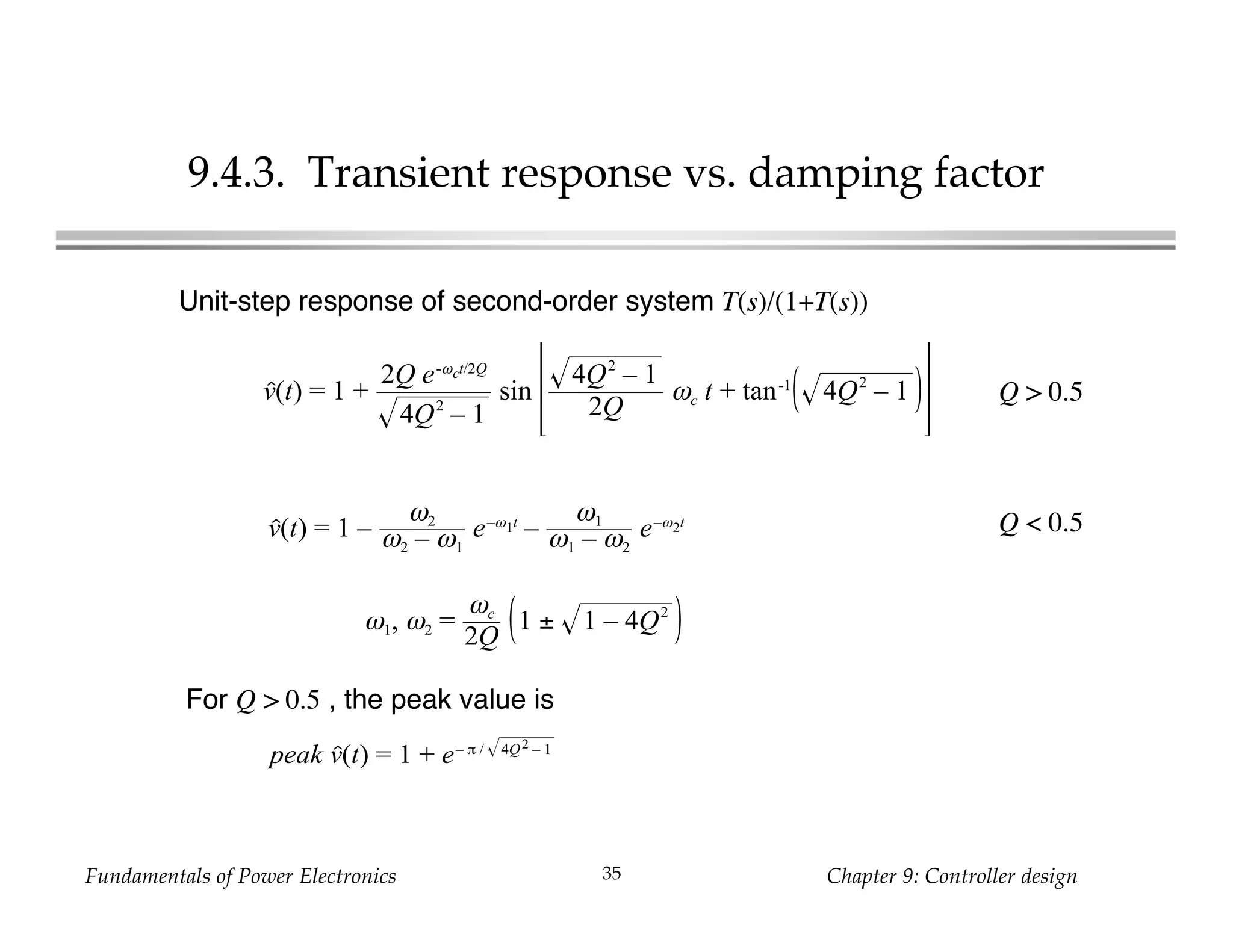

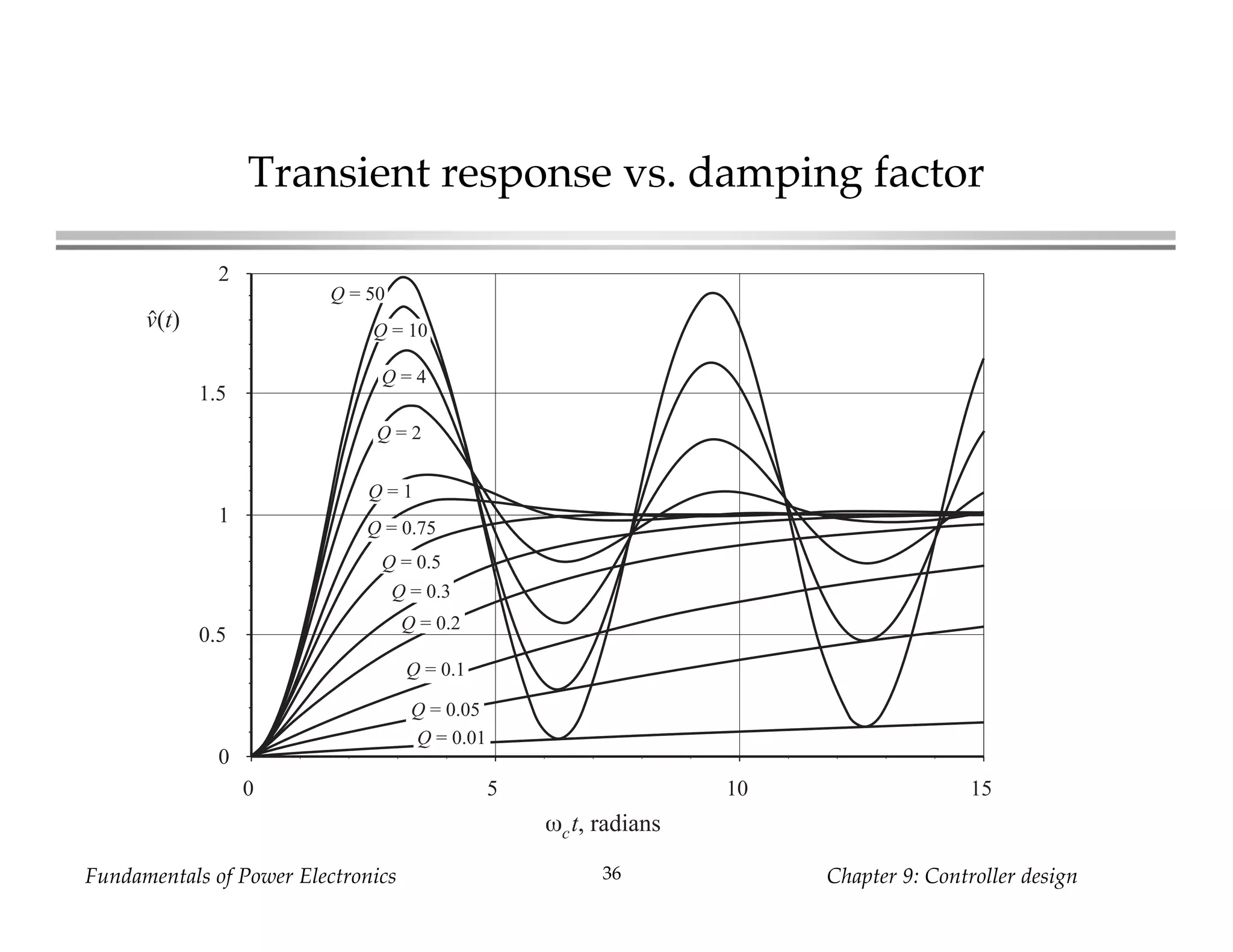

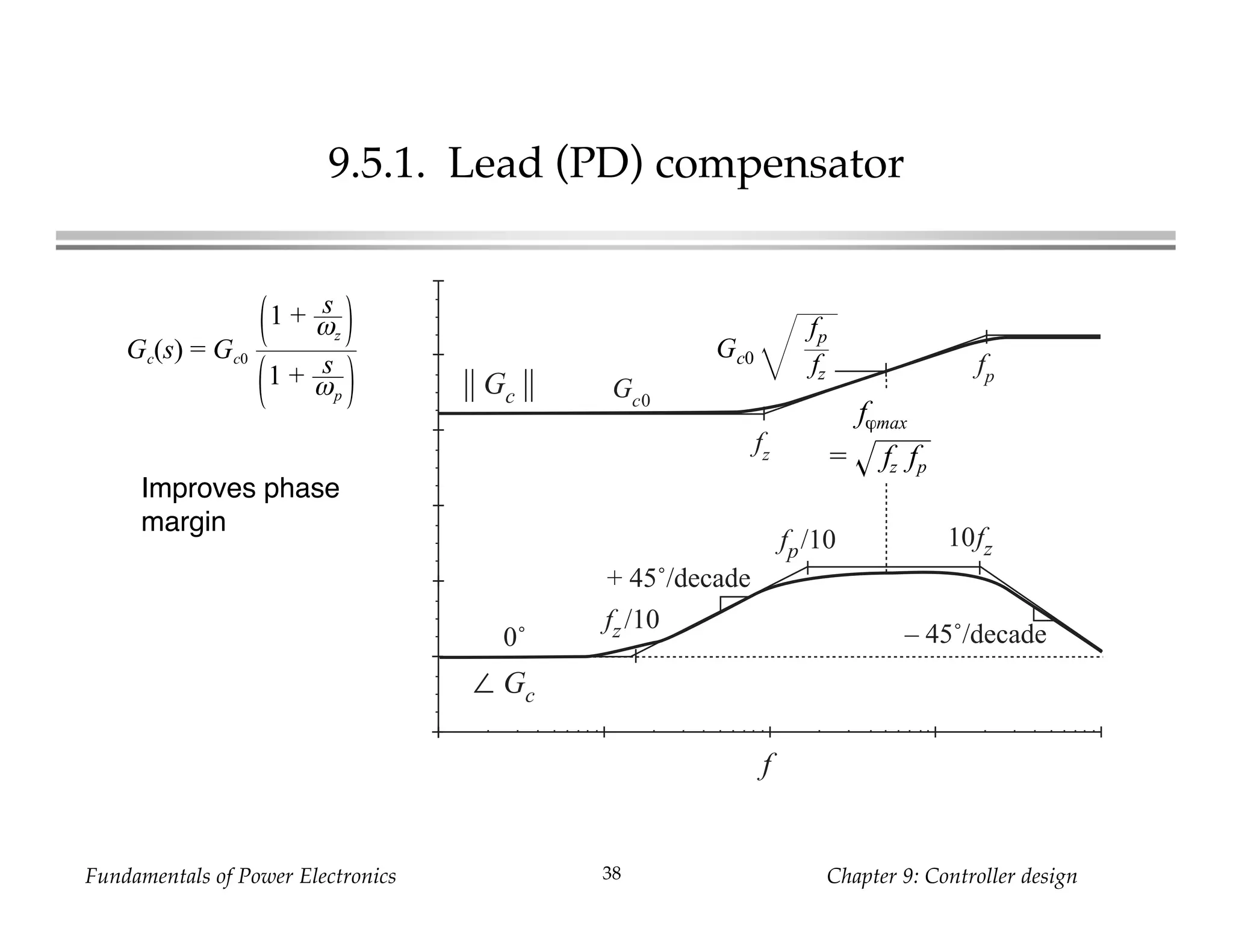

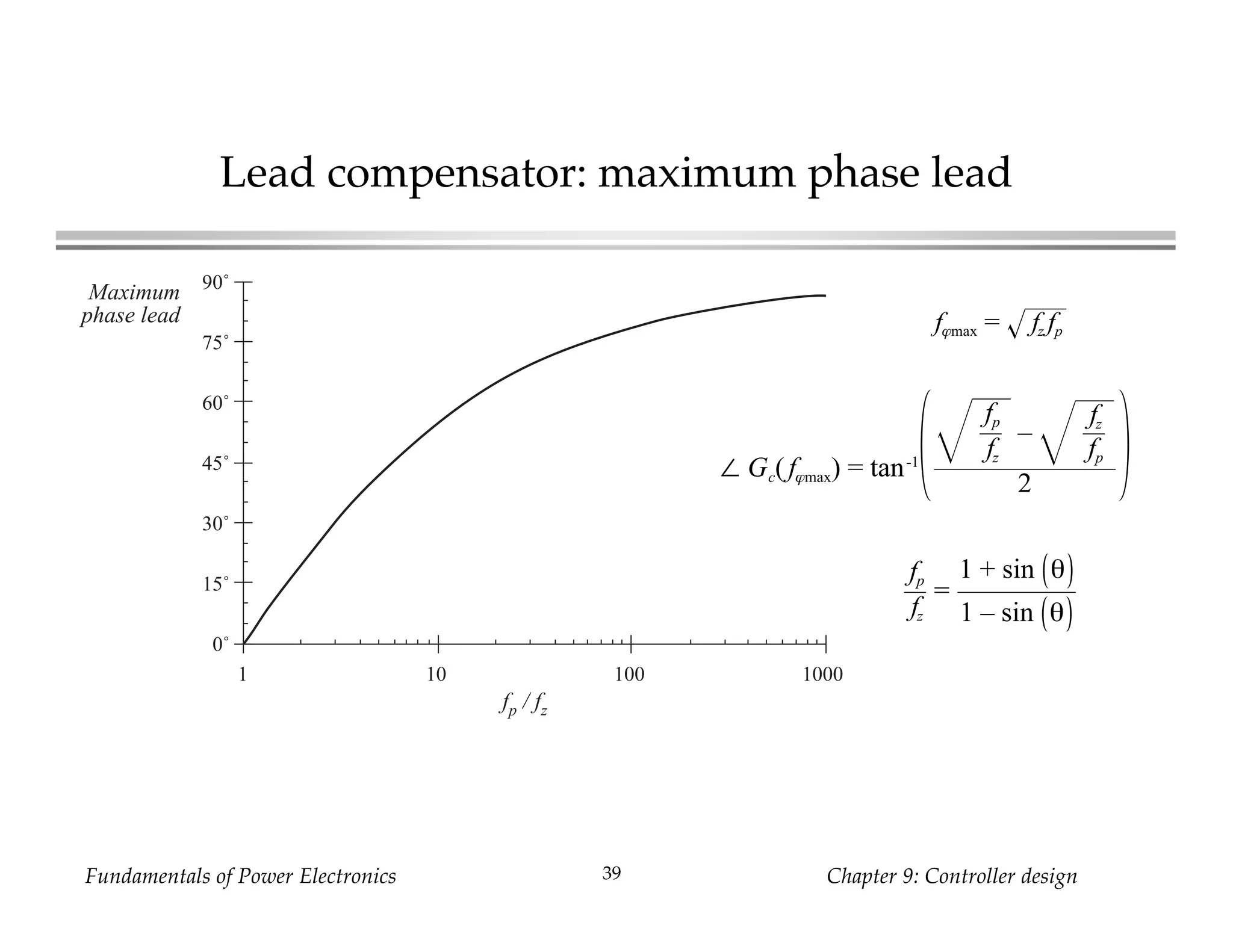

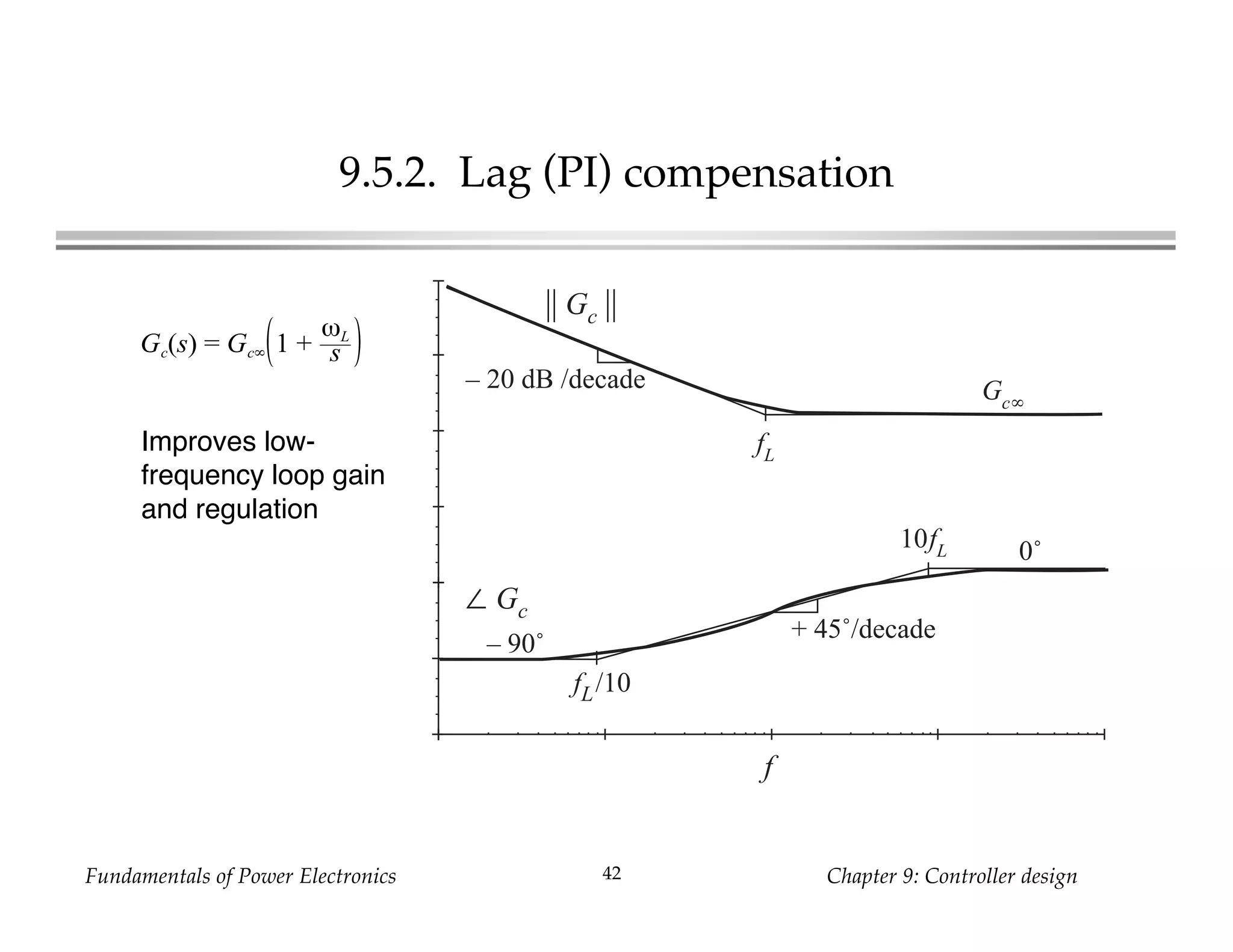

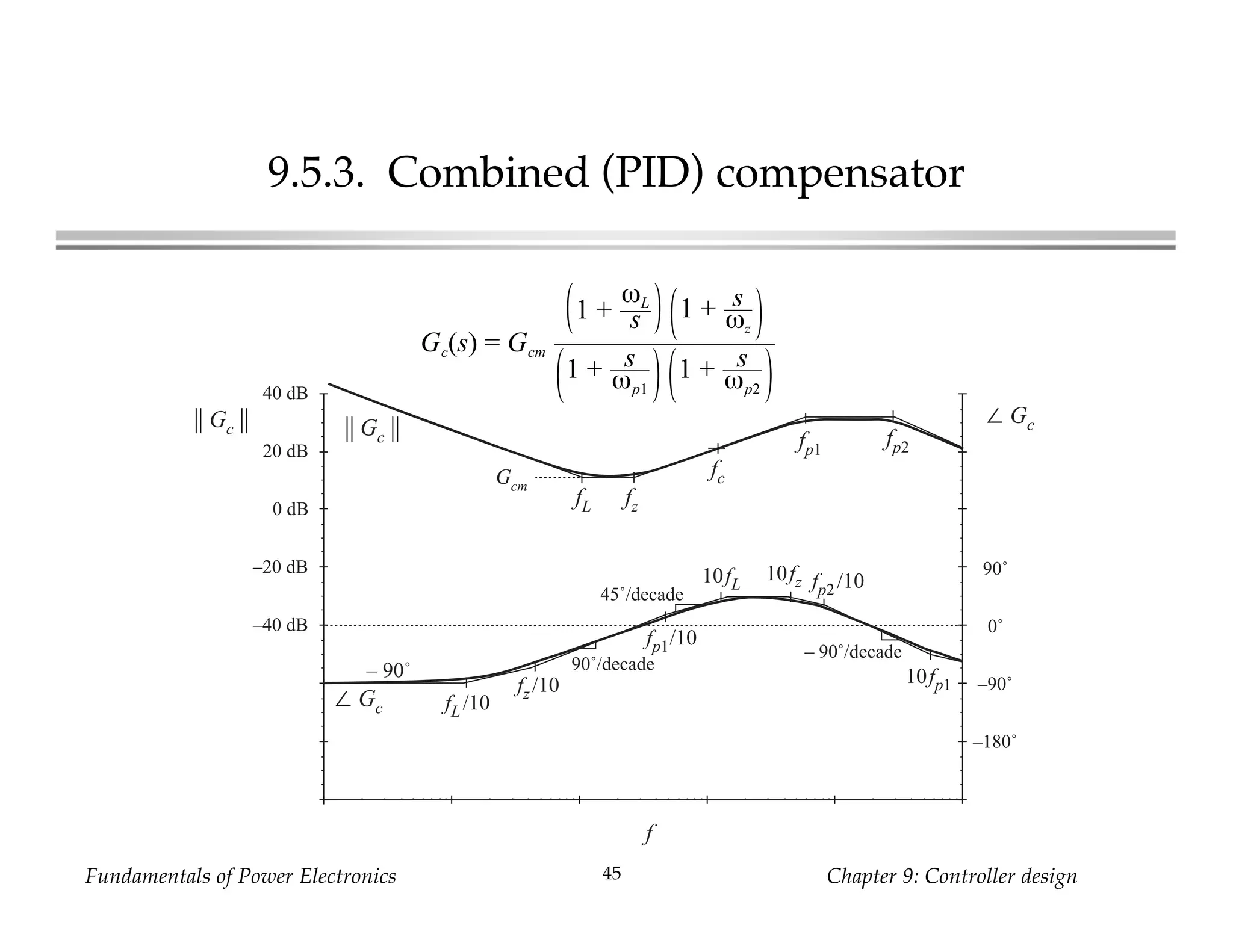

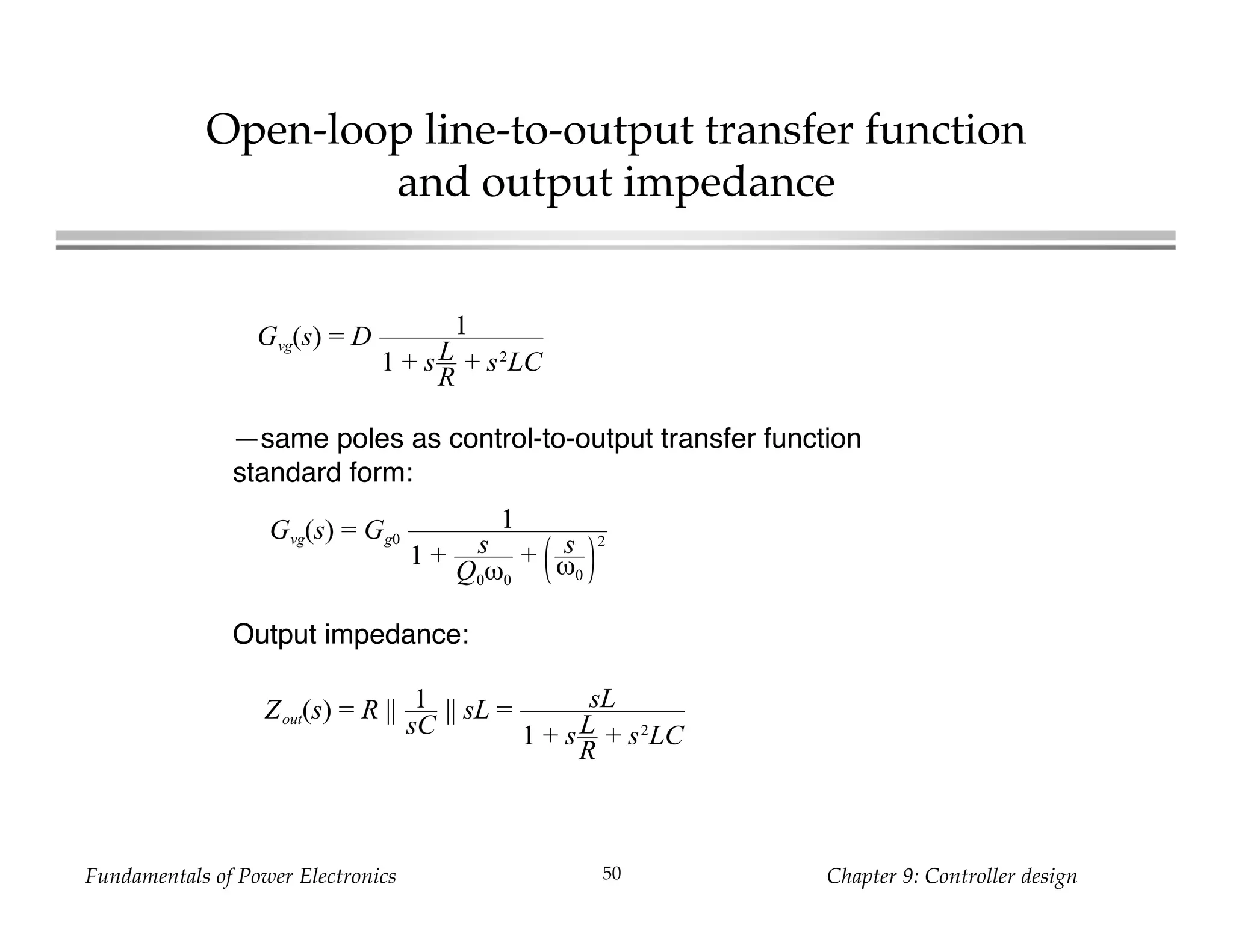

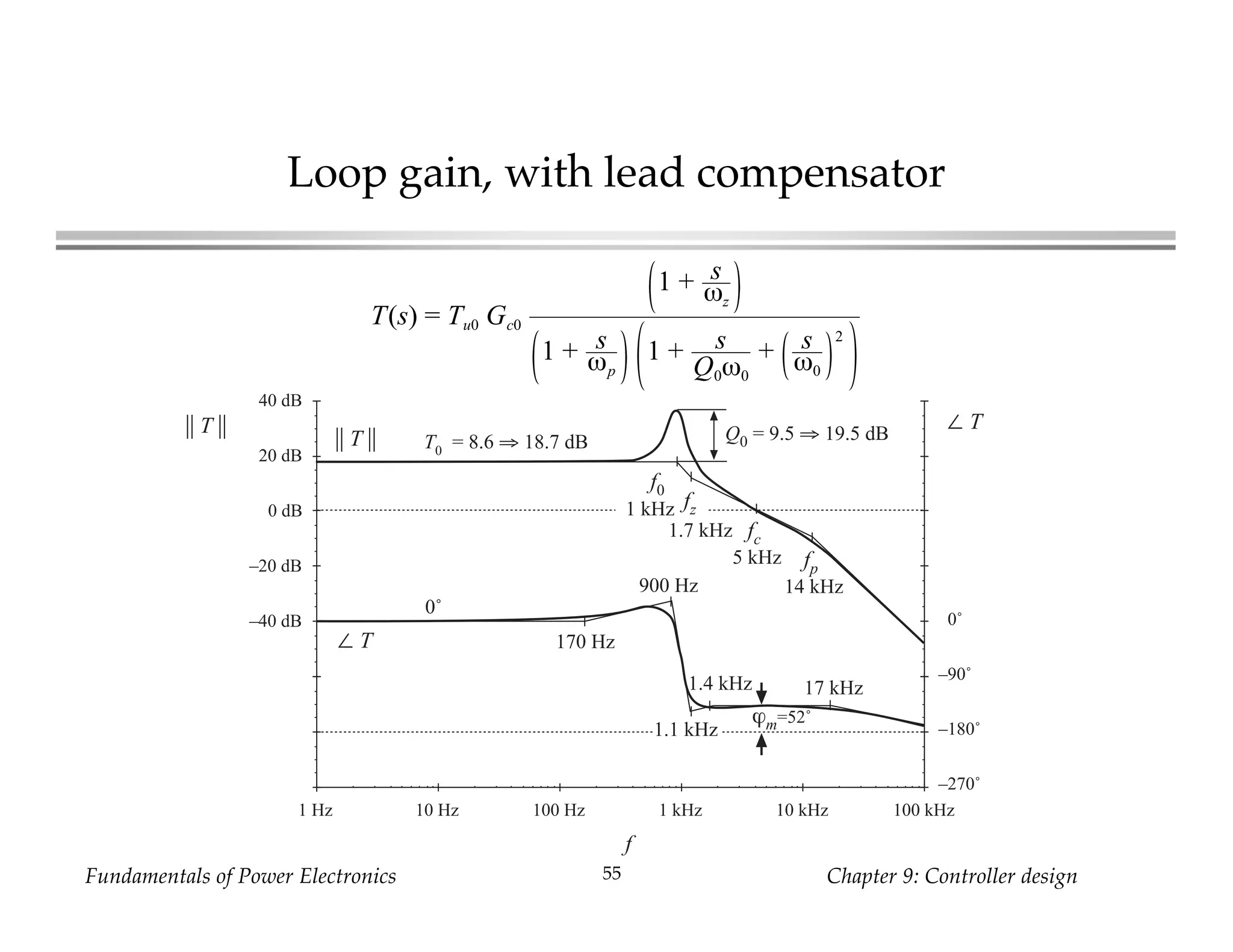

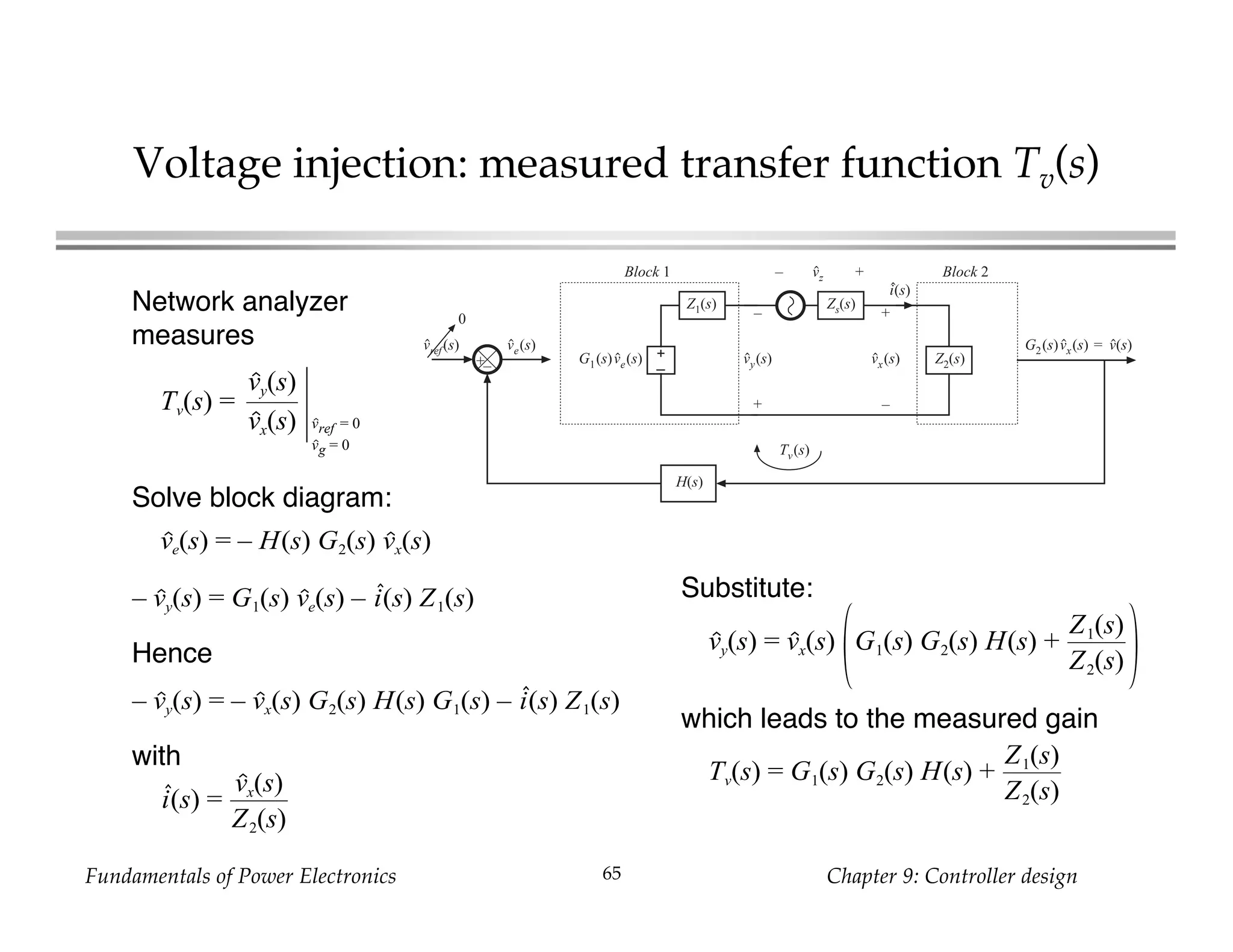

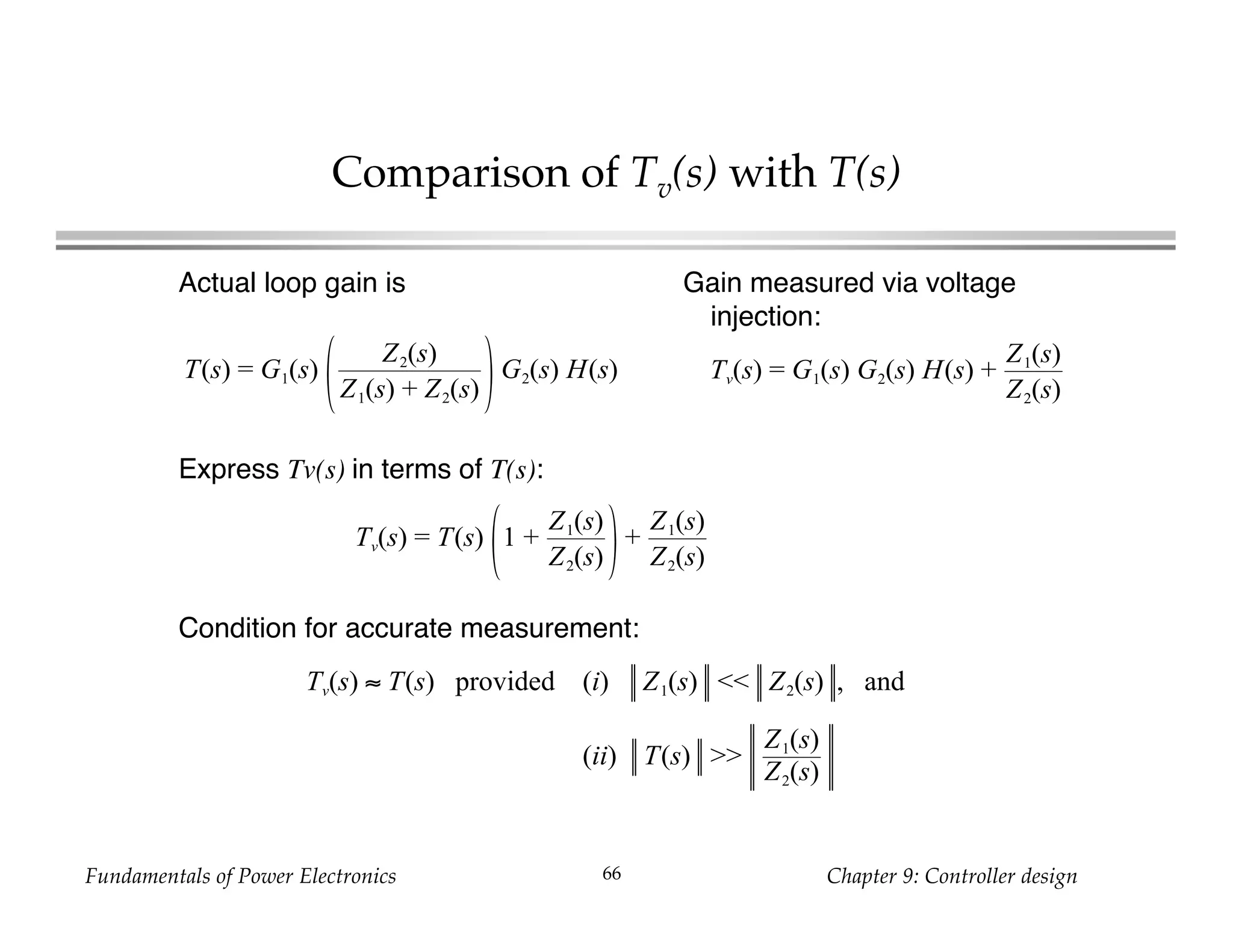

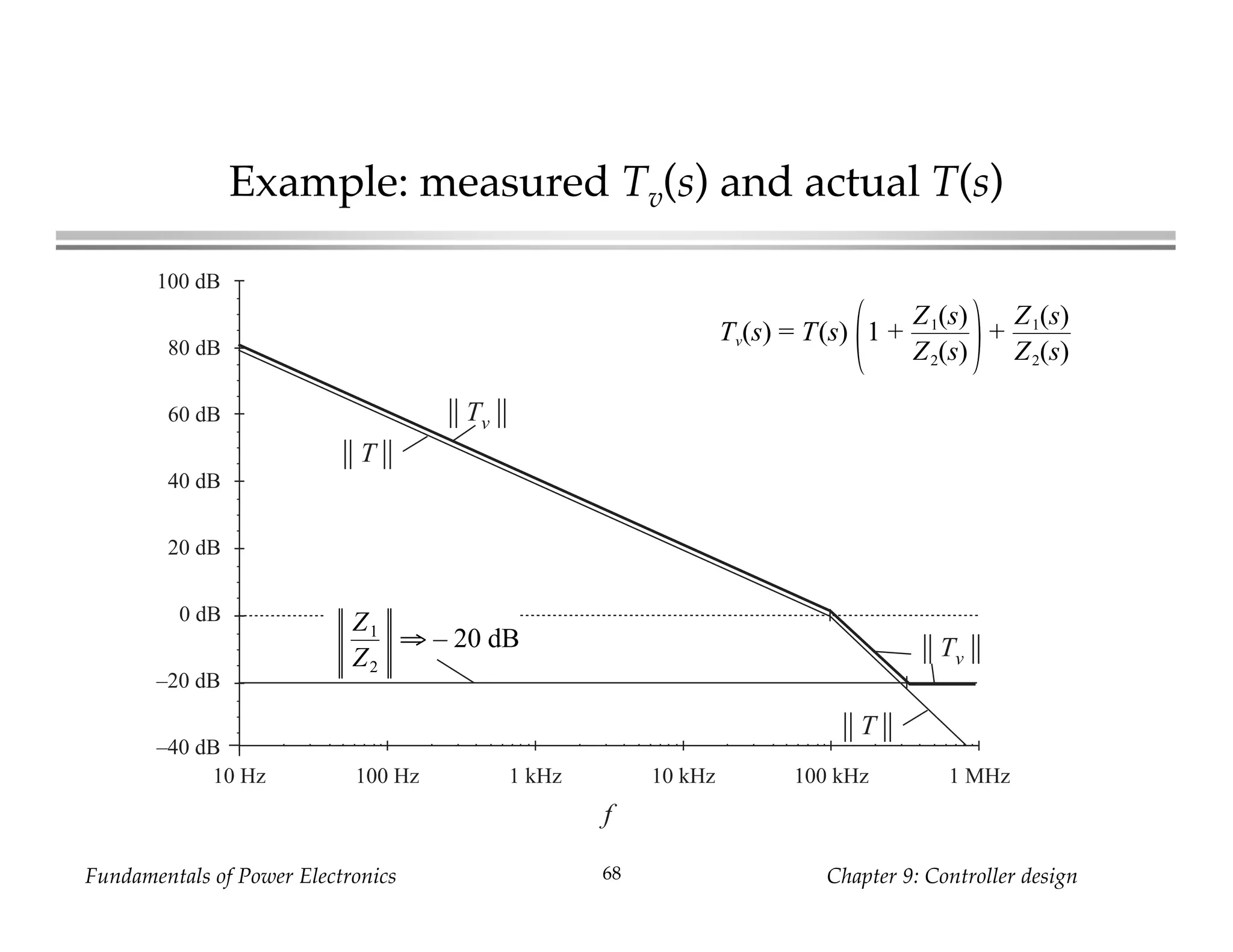

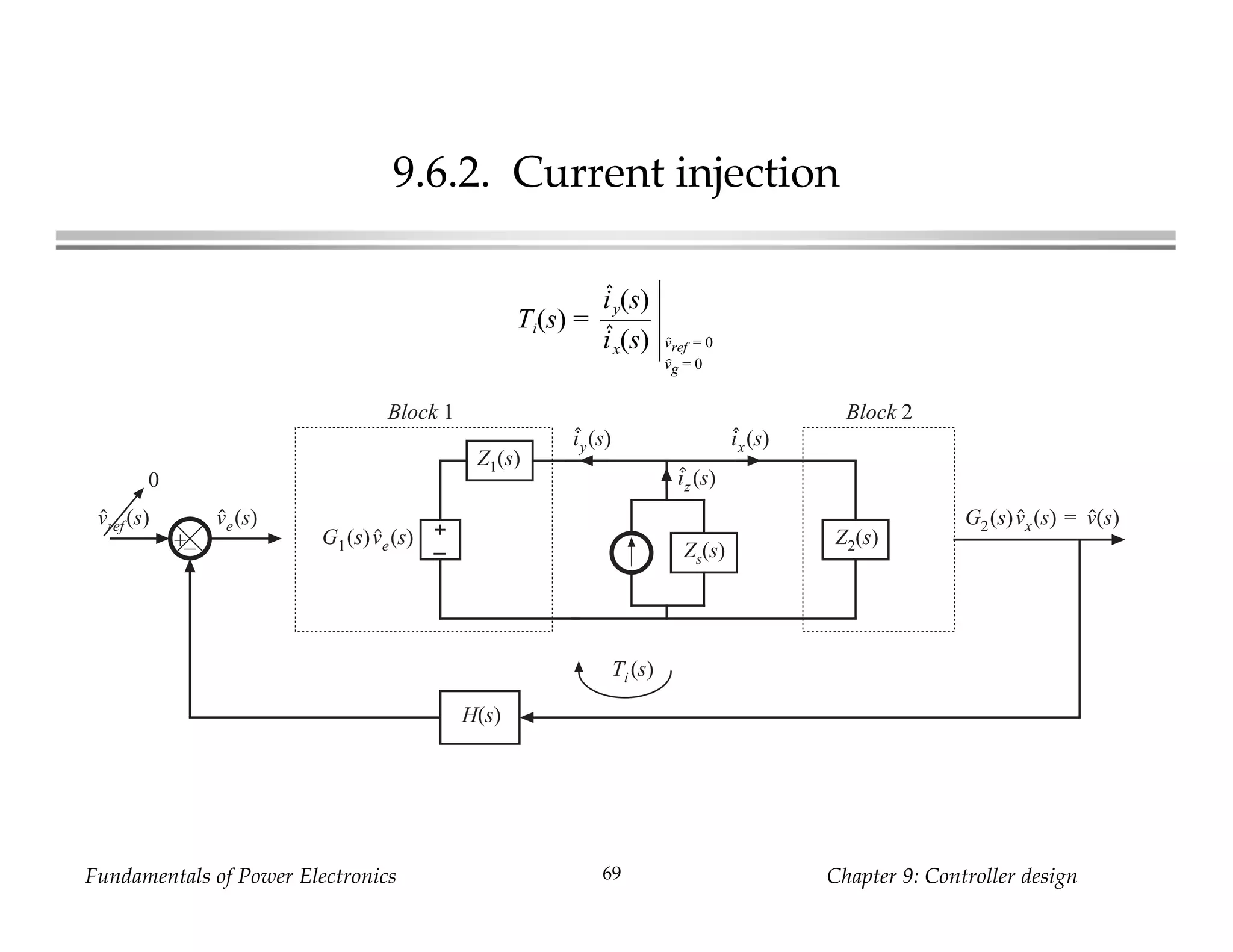

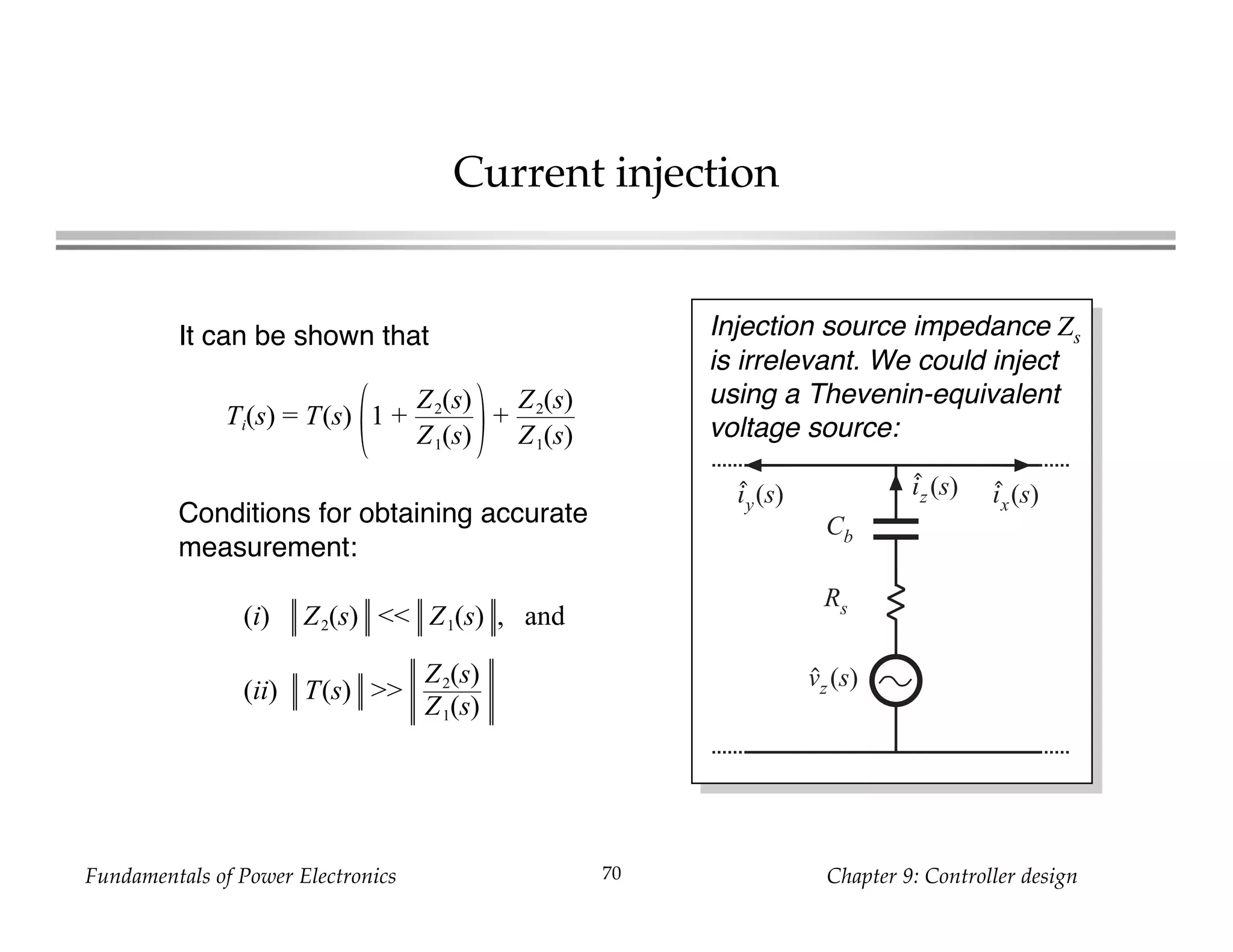

This chapter discusses controller design for power electronics. It begins by introducing negative feedback loops and their effects of reducing disturbances and making the output insensitive to variations in the forward path. Key terms like open-loop, closed-loop, loop gain, and transfer functions are defined. Stability is then analyzed using the phase margin test, which evaluates the phase of the loop gain at the crossover frequency to determine if the closed-loop system contains any right half-plane poles. The chapter covers designing compensators to shape the loop gain for stability and performance. It concludes with measuring loop gains using injection techniques.