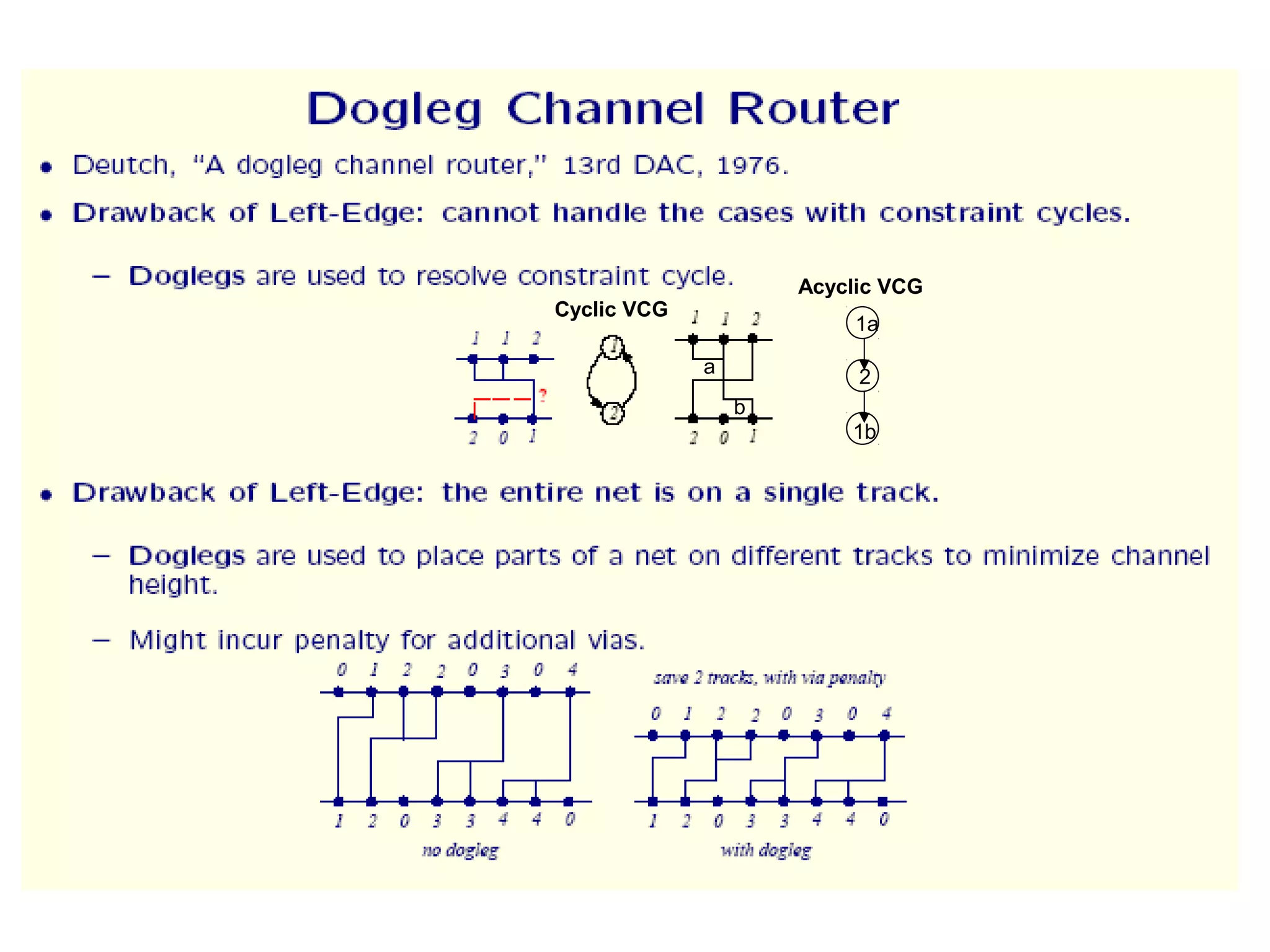

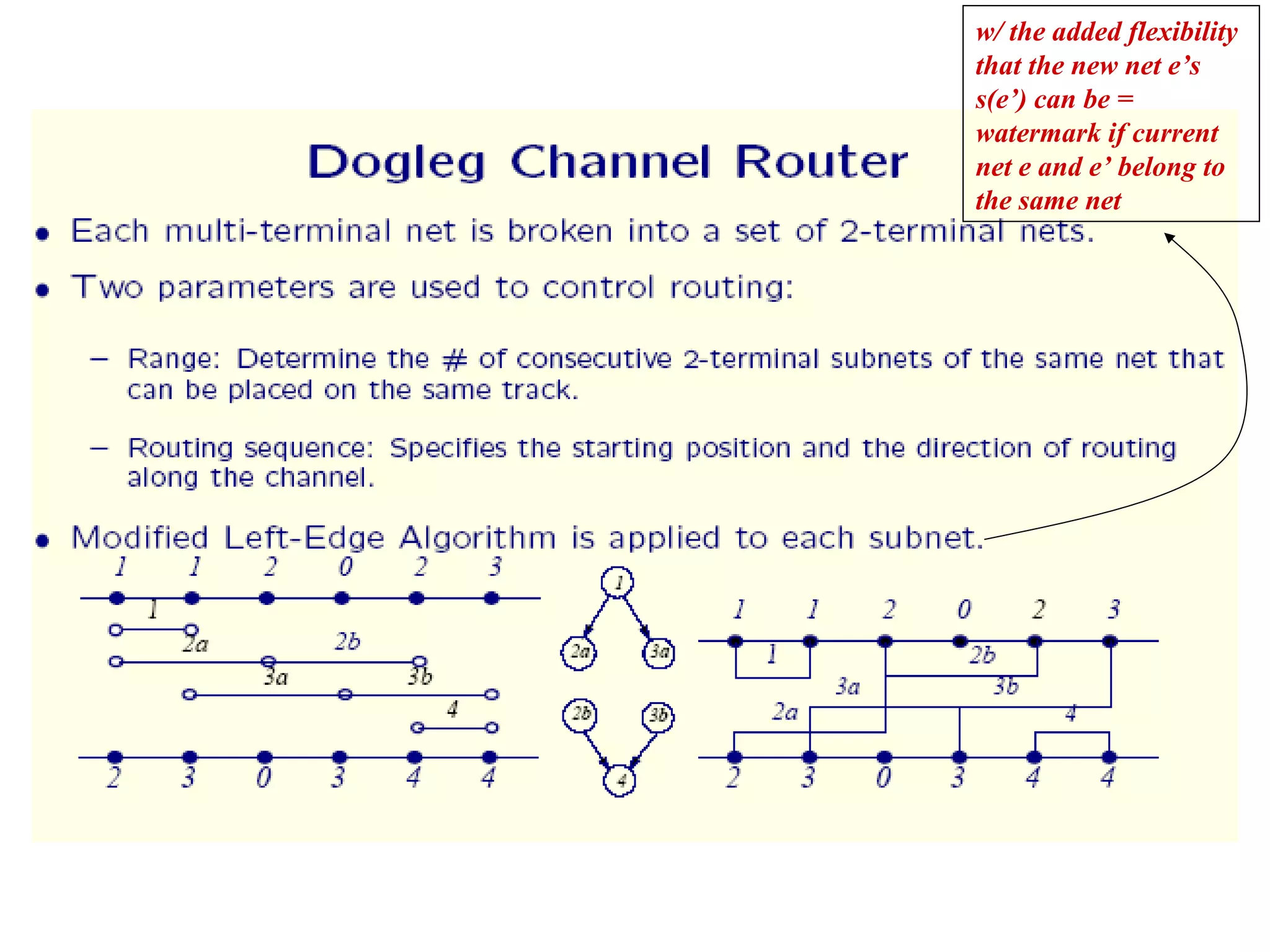

The document provides an overview of global and detailed routing in VLSI design. It discusses how global routing determines routing regions and channels while minimizing congestion and meeting timing constraints. Detailed routing then determines the exact routes and layers for each net within the given channels. Different routing algorithms are categorized, including graph search, hierarchical, and maze routing approaches. Concepts like grids, edge capacities, and Steiner trees are also summarized.

![References and Copyright

(cont.)

• Slides used: (Modified by Shantanu Dutt when necessary)

– [©Sarrafzadeh] © Majid Sarrafzadeh, 2001;

Department of Computer Science, UCLA

– [©Sherwani] © Naveed A. Sherwani, 1992

(companion slides to [She99])

– [©Keutzer] © Kurt Keutzer, Dept. of EECS,

UC-Berekeley

http://www-cad.eecs.berkeley.edu/~niraj/ee244/index.htm

– [©Gupta] © Rajesh Gupta

UC-Irvine

http://www.ics.uci.edu/~rgupta/ics280.html

– [©Kang] © Steve Kang, UIUC http://www.ece.uiuc.edu/ece482/

– [©Bazargan] © Kia Bazargan](https://image.slidesharecdn.com/channelrouting-151102104536-lva1-app6892/75/Channel-routing-2-2048.jpg)

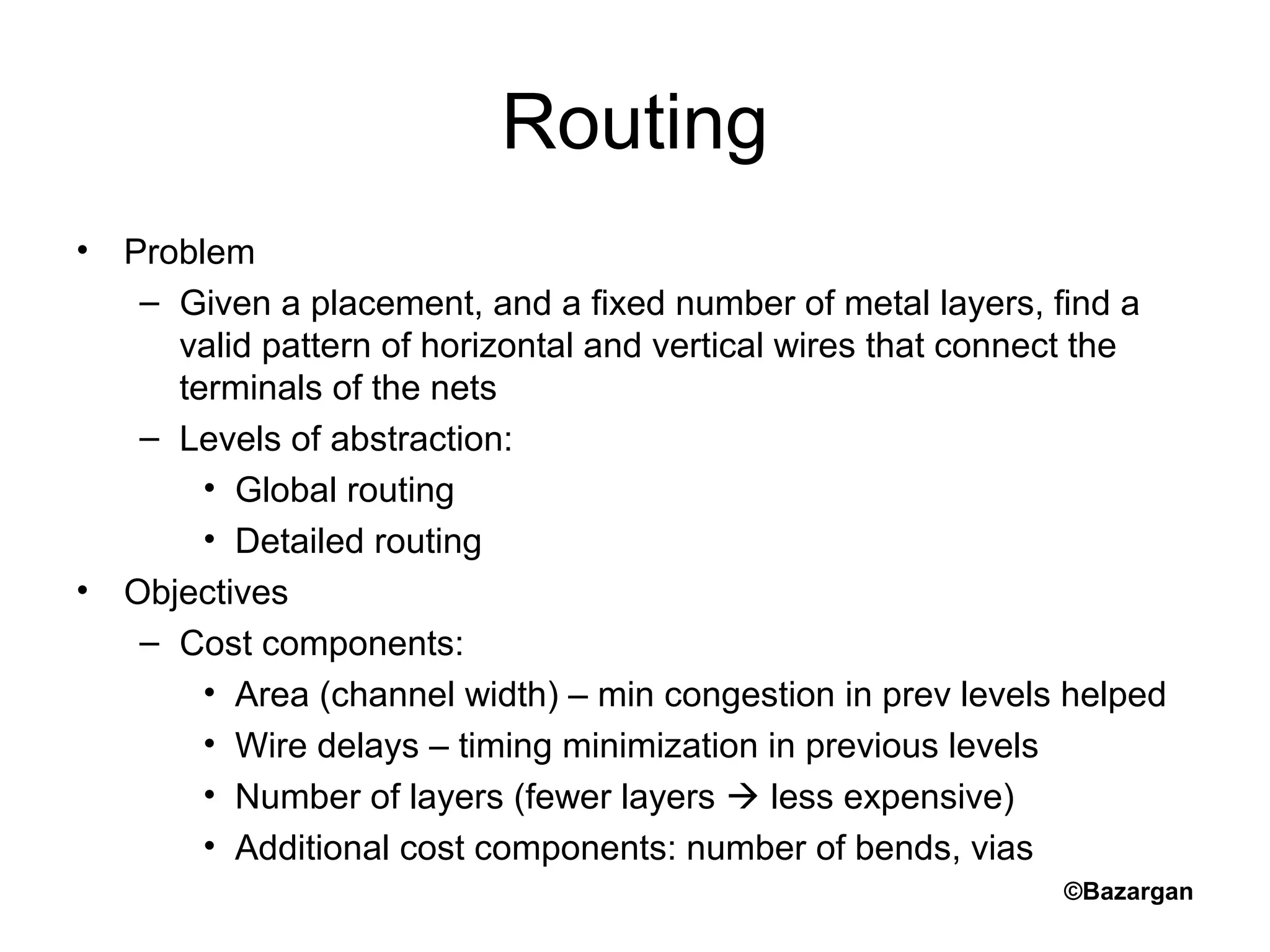

![Global vs. Detailed Routing

• Global routing

– Input: detailed placement, with exact terminal

locations

– Determine “channel” (routing region) for each

net

– Objective: minimize area (congestion), and

timing (approximate)

• Detailed routing

– Input: channels and approximate routing from

the global routing phase

– Determine the exact route and layers for each

net

– Objective: valid routing, minimize area

(congestion), meet timing constraints

– Additional objectives: min via, power

Figs. [©Sherwani]](https://image.slidesharecdn.com/channelrouting-151102104536-lva1-app6892/75/Channel-routing-5-2048.jpg)

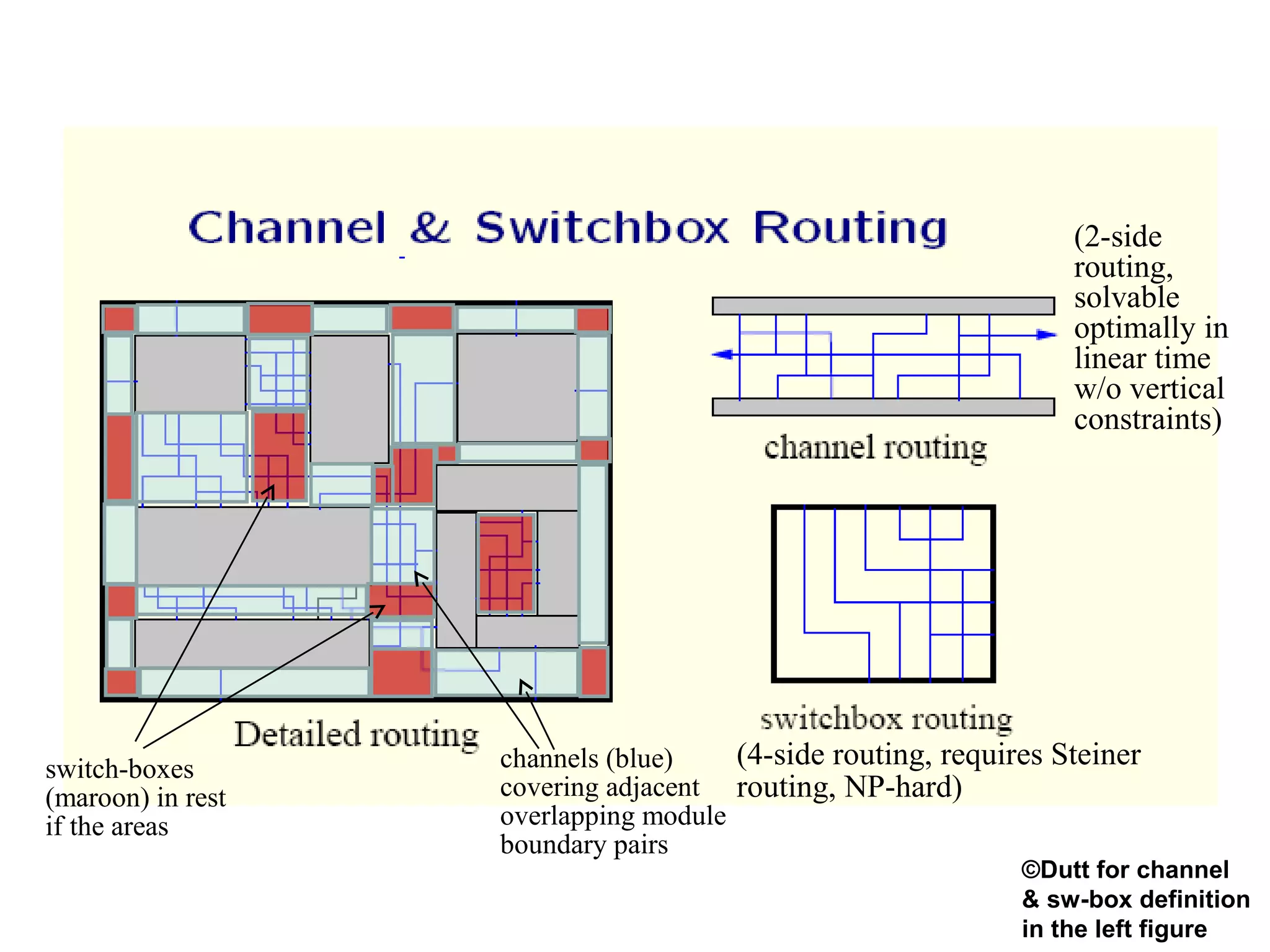

![Taxonomy of VLSI Routers

[©Keutzer]

Graph Search

Steiner

Iterative

Hierarchical Greedy Left-Edge

River

Switchbox

Channel

Maze

Line Probe

Line Expansion

Restricted

General

Purpose

Clock

Specialized

Power/Gnd

Routers

DetailedGlobal

Maze](https://image.slidesharecdn.com/channelrouting-151102104536-lva1-app6892/75/Channel-routing-6-2048.jpg)

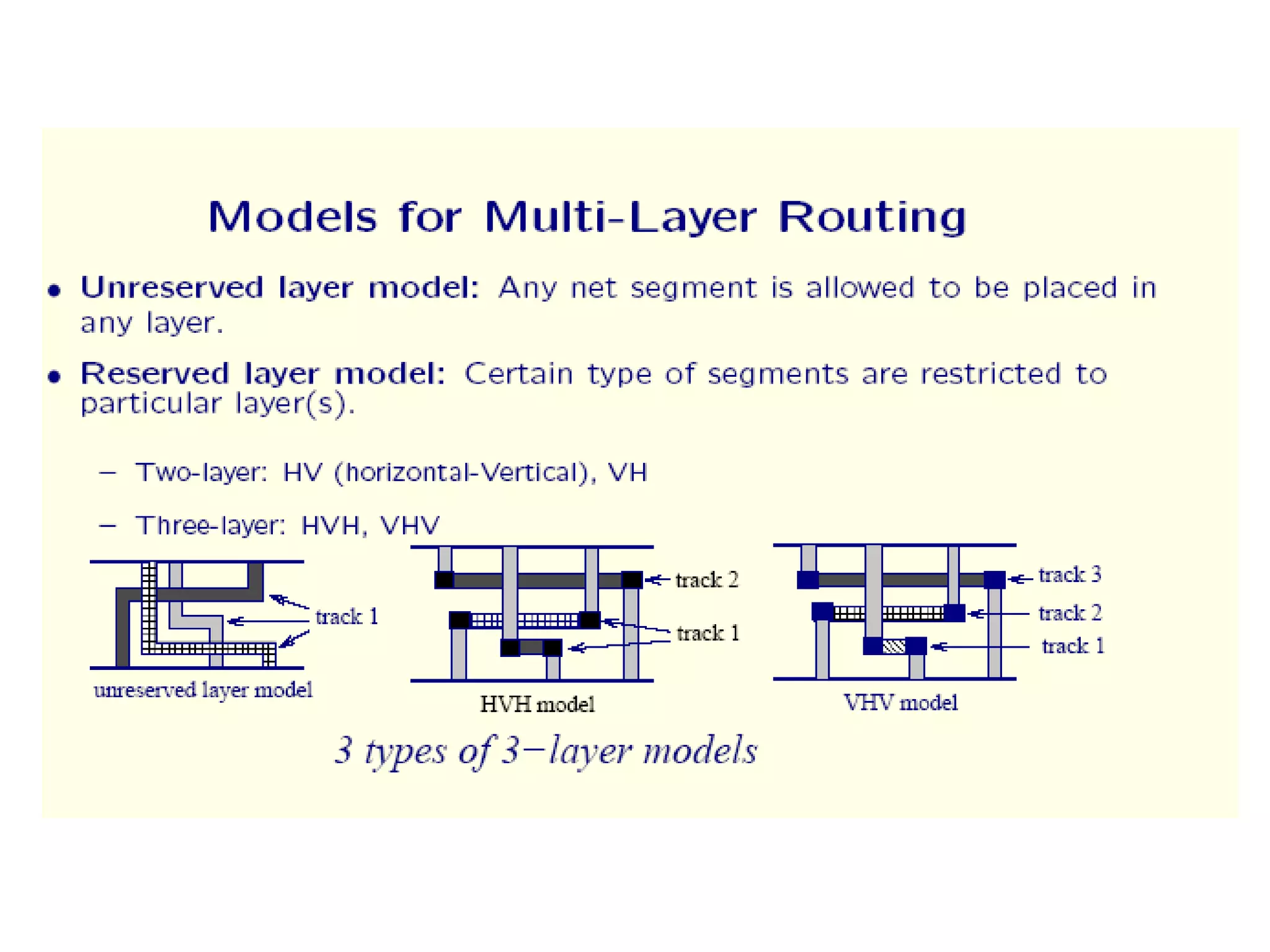

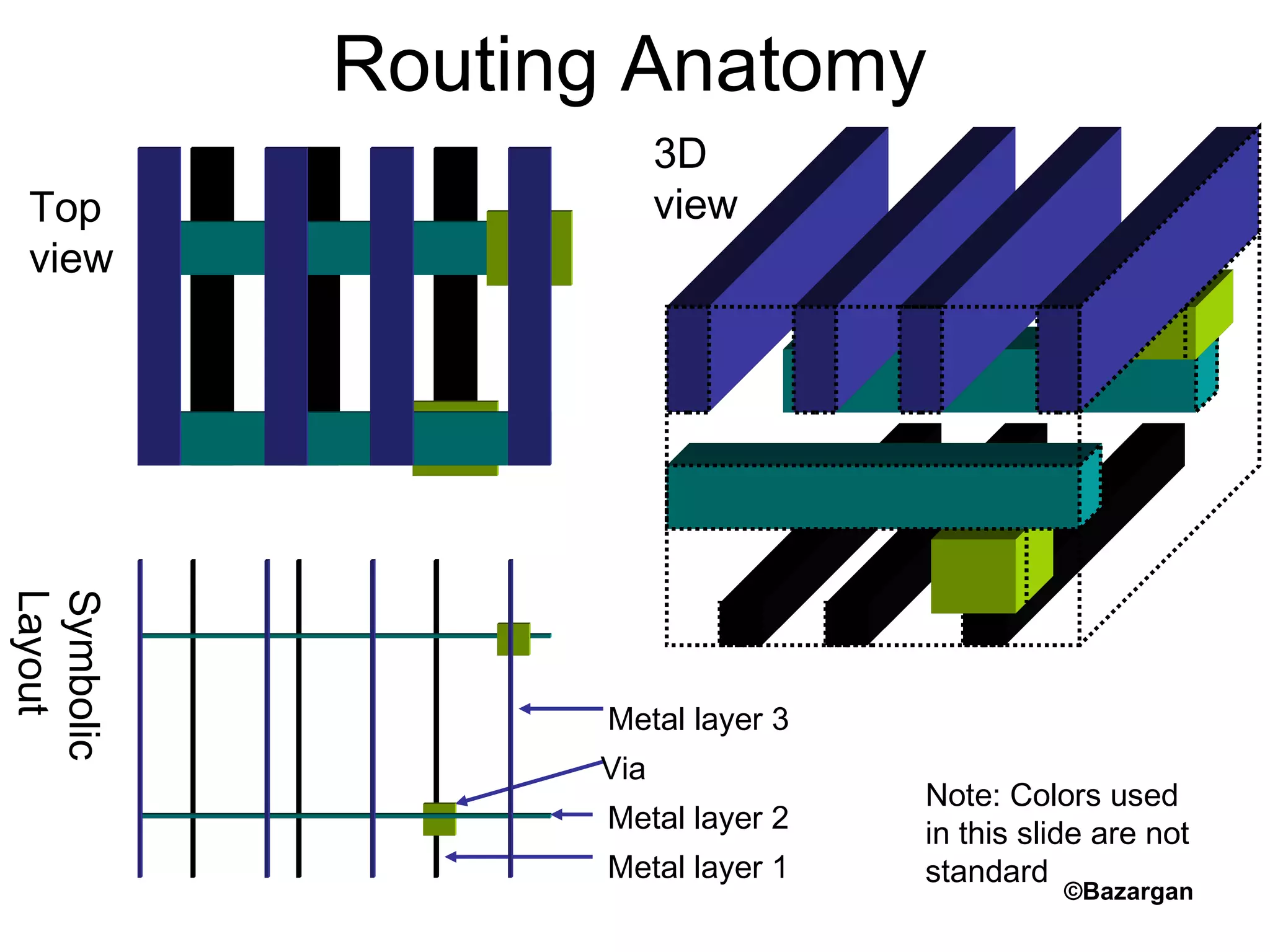

![Global Routing

• Stages

– Routing region definition

– Routing region ordering

– Steiner-tree / area routing

• Grid

– Tiles super-imposed on placement

– Regular or irregular

– Smaller problem to solve,

higher level of abstraction

– Terminals at center of grid tiles

• Edge capacity

– Number of nets that can pass a certain

grid edge (aka congestion)

– On edge Eij,

Capacity(Eij) ≥ Congestion(Eij)

• Steiner routing is generally performed on the

routing graph using edge lengths as cost and

considering edge capacities

M1

M2

M3

[©Sarrafzadeh]](https://image.slidesharecdn.com/channelrouting-151102104536-lva1-app6892/75/Channel-routing-7-2048.jpg)

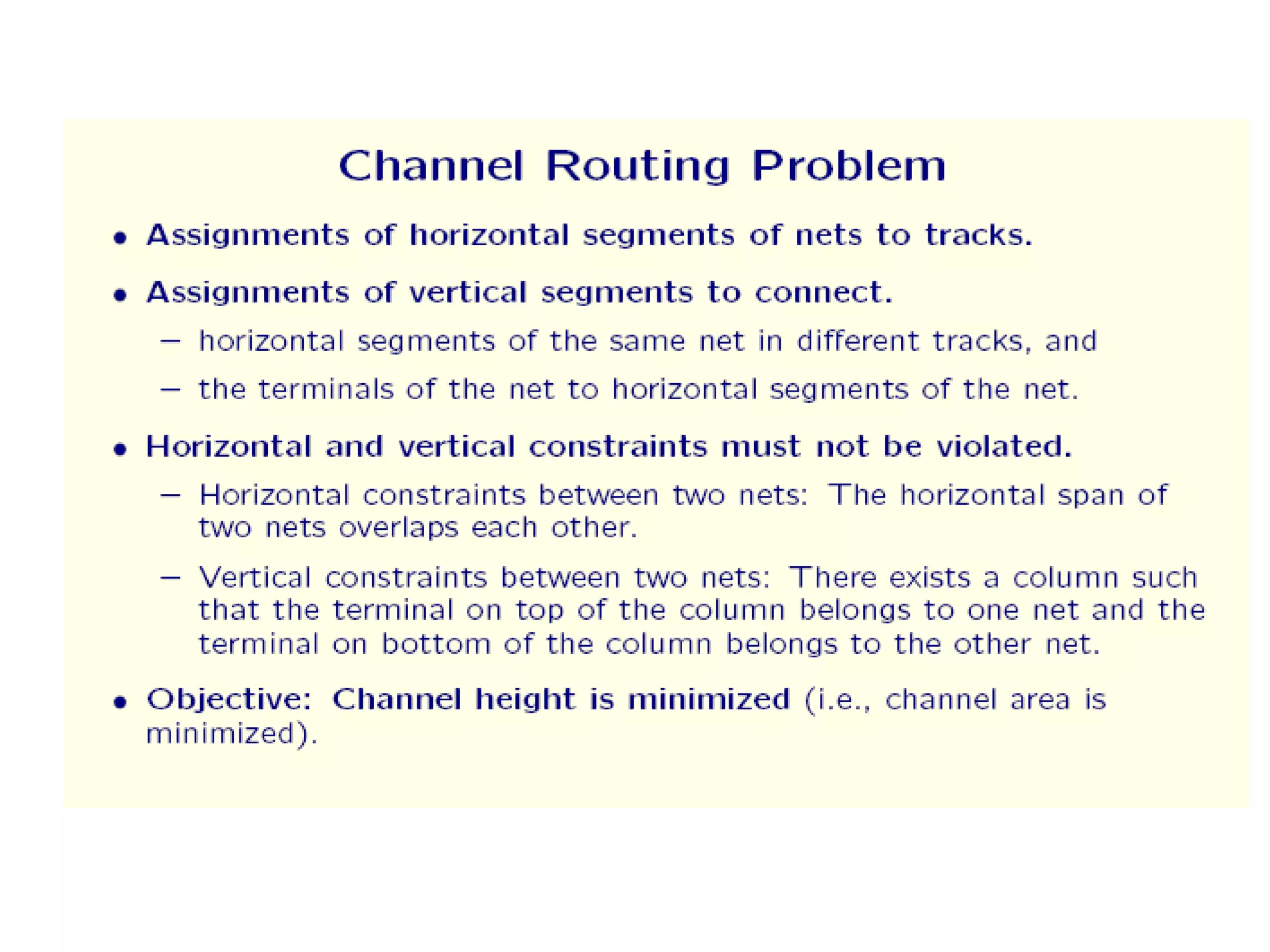

![Grid Graph

• Course or fine-grain

• Vertices: routing regions, edges: route exists?

• Weights on edges

– How costly is to use that edge

– Could vary during the routing (e.g., for congestion)

– Horizontal / vertical might have different weights

[©Sherwani]

t1 t2 t3

t4

t1 t2 t3

t4

1 1 1

1 1 1

2 2 1 1

t1 t3

t4

t2](https://image.slidesharecdn.com/channelrouting-151102104536-lva1-app6892/75/Channel-routing-8-2048.jpg)