Block diagram of 80286

•Download as DOCX, PDF•

0 likes•1,063 views

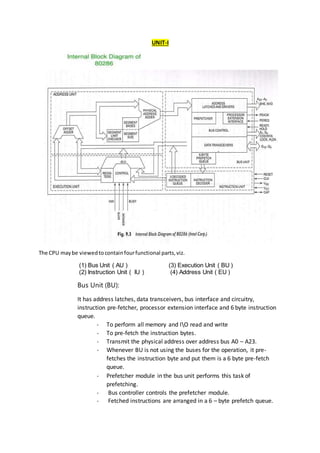

The document discusses the four functional units of the CPU: Bus Unit (BU), Instruction Unit (IU), Execution Unit (EU), and Address Unit (AU). It provides details on each unit: the BU performs memory/I/O reads and writes and prefetches instructions into a 6-byte queue; the IU decodes up to three prefetched instructions and holds them in a queue; the EU includes an ALU, registers, and control unit to execute instructions from the IU queue; the AU computes physical addresses for memory/I/O access. It also summarizes key features of the 80286 microprocessor such as supporting 16MB physical memory, 1GB virtual memory using memory management, and operating in real and protected

Report

Share

Report

Share

Recommended

80286 microprocessor

Features, Register Set, Flag Register, Internal Block Diagram, Interrupts of Intel 80286 microprocessor

8086 microprocessor-architecture

The simplest way to learn the 8086 microprocessor in complete detail!!

PLZ COMMENT!!!!!

& can also download!!!

80486 microprocessor

This presentation gives the basic idea about the Intel 80486 Microprocessor family.

Recommended

80286 microprocessor

Features, Register Set, Flag Register, Internal Block Diagram, Interrupts of Intel 80286 microprocessor

8086 microprocessor-architecture

The simplest way to learn the 8086 microprocessor in complete detail!!

PLZ COMMENT!!!!!

& can also download!!!

80486 microprocessor

This presentation gives the basic idea about the Intel 80486 Microprocessor family.

General register organization (computer organization)

General register organization (computer organization)

viva q&a for mp lab

document about viva questions and answers for MicroProcessor LaB in my site

www.study3-1engg.blogspot.com

Intel 80286

80286 is the first member of the family of advanced microprocessors with memory management and wide protection abilities.This designed for multi-user systems with multitasking applications

INTEL 8086 MICROPROCESSOR

Introduction and much more represented in this presentation.

So see it and give your valuable feedback.

Assembly Language and Structures of Microcomputer | Chap-1

The first chapter of Assembly Language Programming explains the memory, cpu, i/o devices, how instructions are executed. It starts off by discussing bytes, words, organization of memory and how are buses used as communication lines that works as the artery of the computer system. It also dives into explaining how the Execution Unit and Bus Interface Unit simultaneously work to execute instructions in a CPU, taking the example of Intel 8086 microprocessor. Then, the chapter explains are circuit timing works using a simple Voltage against Time graph. It closes with an example of a simple program written in both Assembly Language and in Machine Language.

2nd puc computer science chapter 1 backdrop of computers

this page contains 2nd puc computer science chapter 1 complet notes

More Related Content

What's hot

General register organization (computer organization)

General register organization (computer organization)

viva q&a for mp lab

document about viva questions and answers for MicroProcessor LaB in my site

www.study3-1engg.blogspot.com

Intel 80286

80286 is the first member of the family of advanced microprocessors with memory management and wide protection abilities.This designed for multi-user systems with multitasking applications

INTEL 8086 MICROPROCESSOR

Introduction and much more represented in this presentation.

So see it and give your valuable feedback.

What's hot (20)

General register organization (computer organization)

General register organization (computer organization)

Similar to Block diagram of 80286

Assembly Language and Structures of Microcomputer | Chap-1

The first chapter of Assembly Language Programming explains the memory, cpu, i/o devices, how instructions are executed. It starts off by discussing bytes, words, organization of memory and how are buses used as communication lines that works as the artery of the computer system. It also dives into explaining how the Execution Unit and Bus Interface Unit simultaneously work to execute instructions in a CPU, taking the example of Intel 8086 microprocessor. Then, the chapter explains are circuit timing works using a simple Voltage against Time graph. It closes with an example of a simple program written in both Assembly Language and in Machine Language.

2nd puc computer science chapter 1 backdrop of computers

this page contains 2nd puc computer science chapter 1 complet notes

Module 4 advanced microprocessors

Architecture and Comparison of various Processors

80186,80286,80386,80486, Pentium

Case Study on Advanced Multiprocessors

Microprocessor 80286

A microprocessor is a type of integrated circuit or chip and is the heart of every computer. Ever since the 1980s, advertisements for personal computers have made a big deal about the microprocessors inside the box, even though every computer relies on dozens of other integrated circuits to work properly. But when it was first invented, engineers thought that the microprocessor would be an entire computer on a chip.

8086 microprocessor

A introduction to 8086 microprocessor

Your Crash course in your Pocket! Microprocessors: 8085, 8086, 80386, Pentium… Microcontrollers: 8051, ARM… Computer Organisation & Architecture

what is 8086 microprocessor, and its features

But we couldn’t pass up celebrating the 8086's anniversary in style. Time for a little DIY action to turn it into a work of art!

On this channel you can get education and knowledge for general issues and topics

8086 architecture and pin description

This presentation contains explanation about 8086 architecture and Pin details

Microprocessors - 80386DX

Indroduction,Memory types,Architecture,Register Organization,Microprocessor 80386DX.

Introduction to Processor

This lecture slide explains the processor unit used in the computer system.

Module 1 8086

Register Organization of 8086, Architecture, Signal Description of 8086, Physical Memory

Organization, General Bus Operation, I/O Addressing Capability, Special Processor Activities,

Minimum Mode 8086 System and Timings, Maximum Mode 8086 System and Timings.

Addressing Modes of 8086.

Similar to Block diagram of 80286 (20)

Assembly Language and Structures of Microcomputer | Chap-1

Assembly Language and Structures of Microcomputer | Chap-1

2nd puc computer science chapter 1 backdrop of computers

2nd puc computer science chapter 1 backdrop of computers

Recently uploaded

special B.ed 2nd year old paper_20240531.pdf

Instagram:-

https://instagram.com/special_education_needs_01?igshid=YmMyMTA2M2Y=

WhatsApp:-

https://chat.whatsapp.com/JVakNIYlSV94x7bwunO3Dc

YouTube:-

https://youtube.com/@special_education_needs

Teligram :- https://t.me/special_education_needs

Slide Shere :-

https://www.slideshare.net/shabnambano20?utm_campaign=profiletracking&utm_medium=sssite&utm_source=ssslideview

BÀI TẬP BỔ TRỢ TIẾNG ANH GLOBAL SUCCESS LỚP 3 - CẢ NĂM (CÓ FILE NGHE VÀ ĐÁP Á...

BÀI TẬP BỔ TRỢ TIẾNG ANH GLOBAL SUCCESS LỚP 3 - CẢ NĂM (CÓ FILE NGHE VÀ ĐÁP Á...Nguyen Thanh Tu Collection

https://app.box.com/s/hqnndn05v4q5a4k4jd597rkdbda0fniiA Strategic Approach: GenAI in Education

Artificial Intelligence (AI) technologies such as Generative AI, Image Generators and Large Language Models have had a dramatic impact on teaching, learning and assessment over the past 18 months. The most immediate threat AI posed was to Academic Integrity with Higher Education Institutes (HEIs) focusing their efforts on combating the use of GenAI in assessment. Guidelines were developed for staff and students, policies put in place too. Innovative educators have forged paths in the use of Generative AI for teaching, learning and assessments leading to pockets of transformation springing up across HEIs, often with little or no top-down guidance, support or direction.

This Gasta posits a strategic approach to integrating AI into HEIs to prepare staff, students and the curriculum for an evolving world and workplace. We will highlight the advantages of working with these technologies beyond the realm of teaching, learning and assessment by considering prompt engineering skills, industry impact, curriculum changes, and the need for staff upskilling. In contrast, not engaging strategically with Generative AI poses risks, including falling behind peers, missed opportunities and failing to ensure our graduates remain employable. The rapid evolution of AI technologies necessitates a proactive and strategic approach if we are to remain relevant.

678020731-Sumas-y-Restas-Para-Colorear.pdf

KKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKKK

Model Attribute Check Company Auto Property

In Odoo, the multi-company feature allows you to manage multiple companies within a single Odoo database instance. Each company can have its own configurations while still sharing common resources such as products, customers, and suppliers.

TESDA TM1 REVIEWER FOR NATIONAL ASSESSMENT WRITTEN AND ORAL QUESTIONS WITH A...

TESDA TM1 REVIEWER FOR NATIONAL ASSESSMENT WRITTEN AND ORAL QUESTIONS WITH ANSWERS.

The approach at University of Liverpool.pptx

How libraries can support authors with open access requirements for UKRI funded books

Wednesday 22 May 2024, 14:00-15:00.

Welcome to TechSoup New Member Orientation and Q&A (May 2024).pdf

In this webinar you will learn how your organization can access TechSoup's wide variety of product discount and donation programs. From hardware to software, we'll give you a tour of the tools available to help your nonprofit with productivity, collaboration, financial management, donor tracking, security, and more.

June 3, 2024 Anti-Semitism Letter Sent to MIT President Kornbluth and MIT Cor...

Letter from the Congress of the United States regarding Anti-Semitism sent June 3rd to MIT President Sally Kornbluth, MIT Corp Chair, Mark Gorenberg

Dear Dr. Kornbluth and Mr. Gorenberg,

The US House of Representatives is deeply concerned by ongoing and pervasive acts of antisemitic

harassment and intimidation at the Massachusetts Institute of Technology (MIT). Failing to act decisively to ensure a safe learning environment for all students would be a grave dereliction of your responsibilities as President of MIT and Chair of the MIT Corporation.

This Congress will not stand idly by and allow an environment hostile to Jewish students to persist. The House believes that your institution is in violation of Title VI of the Civil Rights Act, and the inability or

unwillingness to rectify this violation through action requires accountability.

Postsecondary education is a unique opportunity for students to learn and have their ideas and beliefs challenged. However, universities receiving hundreds of millions of federal funds annually have denied

students that opportunity and have been hijacked to become venues for the promotion of terrorism, antisemitic harassment and intimidation, unlawful encampments, and in some cases, assaults and riots.

The House of Representatives will not countenance the use of federal funds to indoctrinate students into hateful, antisemitic, anti-American supporters of terrorism. Investigations into campus antisemitism by the Committee on Education and the Workforce and the Committee on Ways and Means have been expanded into a Congress-wide probe across all relevant jurisdictions to address this national crisis. The undersigned Committees will conduct oversight into the use of federal funds at MIT and its learning environment under authorities granted to each Committee.

• The Committee on Education and the Workforce has been investigating your institution since December 7, 2023. The Committee has broad jurisdiction over postsecondary education, including its compliance with Title VI of the Civil Rights Act, campus safety concerns over disruptions to the learning environment, and the awarding of federal student aid under the Higher Education Act.

• The Committee on Oversight and Accountability is investigating the sources of funding and other support flowing to groups espousing pro-Hamas propaganda and engaged in antisemitic harassment and intimidation of students. The Committee on Oversight and Accountability is the principal oversight committee of the US House of Representatives and has broad authority to investigate “any matter” at “any time” under House Rule X.

• The Committee on Ways and Means has been investigating several universities since November 15, 2023, when the Committee held a hearing entitled From Ivory Towers to Dark Corners: Investigating the Nexus Between Antisemitism, Tax-Exempt Universities, and Terror Financing. The Committee followed the hearing with letters to those institutions on January 10, 202

The geography of Taylor Swift - some ideas

Geographical themes connected with Taylor Swift's ERAS tour - coming to the UK in June 2024

Synthetic Fiber Construction in lab .pptx

Synthetic fiber production is a fascinating and complex field that blends chemistry, engineering, and environmental science. By understanding these aspects, students can gain a comprehensive view of synthetic fiber production, its impact on society and the environment, and the potential for future innovations. Synthetic fibers play a crucial role in modern society, impacting various aspects of daily life, industry, and the environment. ynthetic fibers are integral to modern life, offering a range of benefits from cost-effectiveness and versatility to innovative applications and performance characteristics. While they pose environmental challenges, ongoing research and development aim to create more sustainable and eco-friendly alternatives. Understanding the importance of synthetic fibers helps in appreciating their role in the economy, industry, and daily life, while also emphasizing the need for sustainable practices and innovation.

How to Make a Field invisible in Odoo 17

It is possible to hide or invisible some fields in odoo. Commonly using “invisible” attribute in the field definition to invisible the fields. This slide will show how to make a field invisible in odoo 17.

Chapter 3 - Islamic Banking Products and Services.pptx

Chapter 3 - Islamic Banking Products and Services.pptxMohd Adib Abd Muin, Senior Lecturer at Universiti Utara Malaysia

This slide is prepared for master's students (MIFB & MIBS) UUM. May it be useful to all.Digital Tools and AI for Teaching Learning and Research

This Presentation in details discusses on Digital Tools and AI for Teaching Learning and Research

Instructions for Submissions thorugh G- Classroom.pptx

This presentation provides a briefing on how to upload submissions and documents in Google Classroom. It was prepared as part of an orientation for new Sainik School in-service teacher trainees. As a training officer, my goal is to ensure that you are comfortable and proficient with this essential tool for managing assignments and fostering student engagement.

Acetabularia Information For Class 9 .docx

Acetabularia acetabulum is a single-celled green alga that in its vegetative state is morphologically differentiated into a basal rhizoid and an axially elongated stalk, which bears whorls of branching hairs. The single diploid nucleus resides in the rhizoid.

Recently uploaded (20)

BÀI TẬP BỔ TRỢ TIẾNG ANH GLOBAL SUCCESS LỚP 3 - CẢ NĂM (CÓ FILE NGHE VÀ ĐÁP Á...

BÀI TẬP BỔ TRỢ TIẾNG ANH GLOBAL SUCCESS LỚP 3 - CẢ NĂM (CÓ FILE NGHE VÀ ĐÁP Á...

TESDA TM1 REVIEWER FOR NATIONAL ASSESSMENT WRITTEN AND ORAL QUESTIONS WITH A...

TESDA TM1 REVIEWER FOR NATIONAL ASSESSMENT WRITTEN AND ORAL QUESTIONS WITH A...

Welcome to TechSoup New Member Orientation and Q&A (May 2024).pdf

Welcome to TechSoup New Member Orientation and Q&A (May 2024).pdf

June 3, 2024 Anti-Semitism Letter Sent to MIT President Kornbluth and MIT Cor...

June 3, 2024 Anti-Semitism Letter Sent to MIT President Kornbluth and MIT Cor...

Chapter 3 - Islamic Banking Products and Services.pptx

Chapter 3 - Islamic Banking Products and Services.pptx

Digital Tools and AI for Teaching Learning and Research

Digital Tools and AI for Teaching Learning and Research

Instructions for Submissions thorugh G- Classroom.pptx

Instructions for Submissions thorugh G- Classroom.pptx

Block diagram of 80286

- 1. UNIT-I The CPU maybe viewedtocontainfourfunctional parts,viz. (1) Bus Unit ( AU ) (3) Execution Unit ( BU ) (2) Instruction Unit ( IU ) (4) Address Unit ( EU ) Bus Unit (BU): It has address latches, data transceivers, bus interface and circuitry, instruction pre-fetcher, processor extension interface and 6 byte instruction queue. - To perform all memory and IO read and write - To pre-fetch the instruction bytes. - Transmit the physical address over address bus A0 – A23. - Whenever BU is not using the buses for the operation, it pre- fetches the instruction byte and put them is a 6 byte pre-fetch queue. - Prefetcher module in the bus unit performs this task of prefetching. - Bus controller controls the prefetcher module. - Fetched instructions are arranged in a 6 – byte prefetch queue.

- 2. Instruction Unit (IU): It has 3 decoded instruction queue and instruction decoder - It fully decodes up to three prefetched instruction and holds them in a queue - So that EU can access them. - It helps the processor to speed up, as pipelining of instruction is done. - Receive arranged instructions from 6 bytes prefetch queue. - Instruction decoder decodes the instruction one by one and are latched onto a decoded instruction queue. Execution Unit (EU): It includes ALU, Register and the Control unit. Register are general purpose, index, pointer, flag register and 16-bit machine status word (MSW). - ALU is the heart of execution unit. - To sequentially execute the instructions received from the instruction unit - Control unit is responsible for executing the instructions received from the decoded instruction queue. - Contains Register Bank. - After execution ALU sends the result either over data bus or back to the register bank. Address Unit ( AU ): - Compute the physical address that will be sent out to the memory or IO by BU. - 80286 operate in two modes. 1. Real address mode 2. Protected address mode - When used in real mode, AU computes the address with segments base and offset like 8086. Segments register are CS, DS, ES, SS hold base address. IP, BP, SI, DI, SP hold offset. - Maximum physical space allowed in this mode is 1MB. - When 80286 operate in protected mode, the address unit acts as MMU. - All 24 address lines used and can access up to 16 MB of physical memory. - Calculate the physical addresses of the instruction and data that the CPU want to access - Address lines derived by this unit may be used to address different peripherals.

- 3. 80286 Basic Features The 80286 microprocessorisanadvancedversionof the 8086 microprocessorthatis designedformulti userandmultitaskingenvironments The 80286 addresses16 M Byte of physical memoryand 1G Bytesof virtual memoryby usingitsmemory-managementsystem The performance of 80286 is five timesfasterthanthe standard8086. The 80286 isbasicallyan8086 that is optimizedtoexecute instructionsinfewerclocking periodsthanthe 8086 Like the 80186, the 80286 doesn’tincorporate internal peripherals;insteaditcontainsa memorymanagementunit(MMU) The 80286 operatesinboththe real and protectedmodes In the real mode,the 80286 addressesa1MByte memoryaddressspace and isvirtually identical to8086 In the protectedmode,the 80286 addressesa16MByte memoryspace. The 80286 containsthe same instructionsexceptfora handful of additional instructionsthat control the memory-managementnit. It is16-bit flagregisterwith12-bitsare used4-bitsunused.