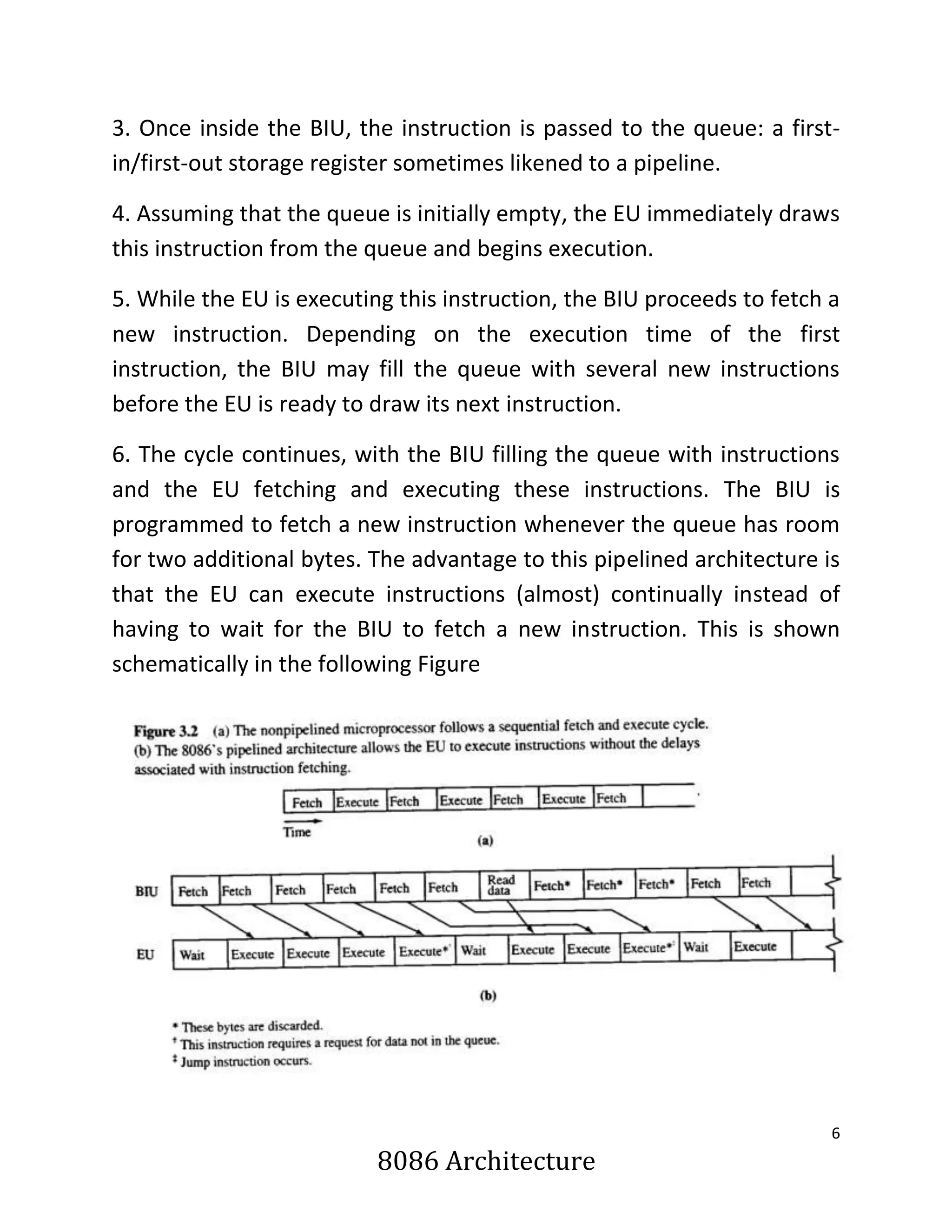

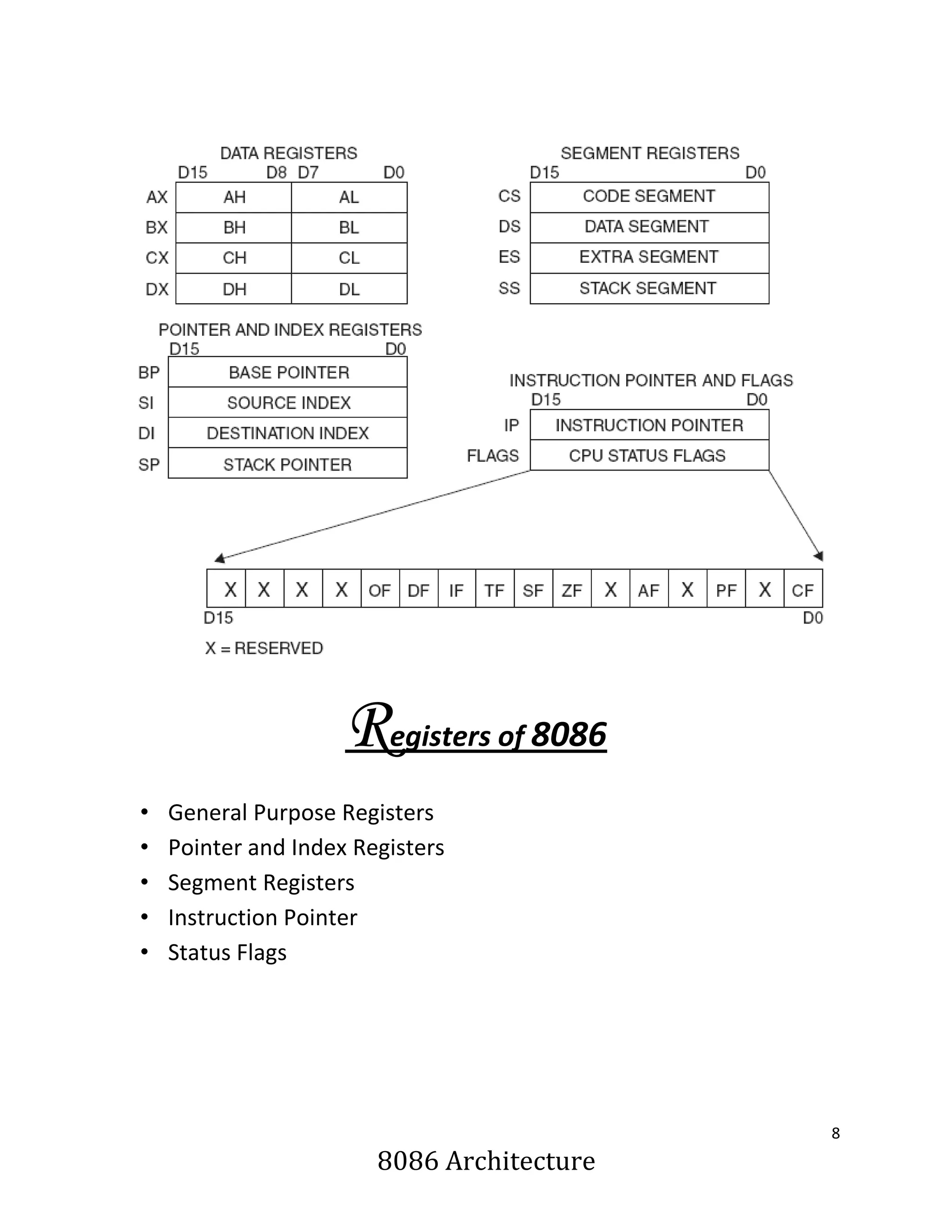

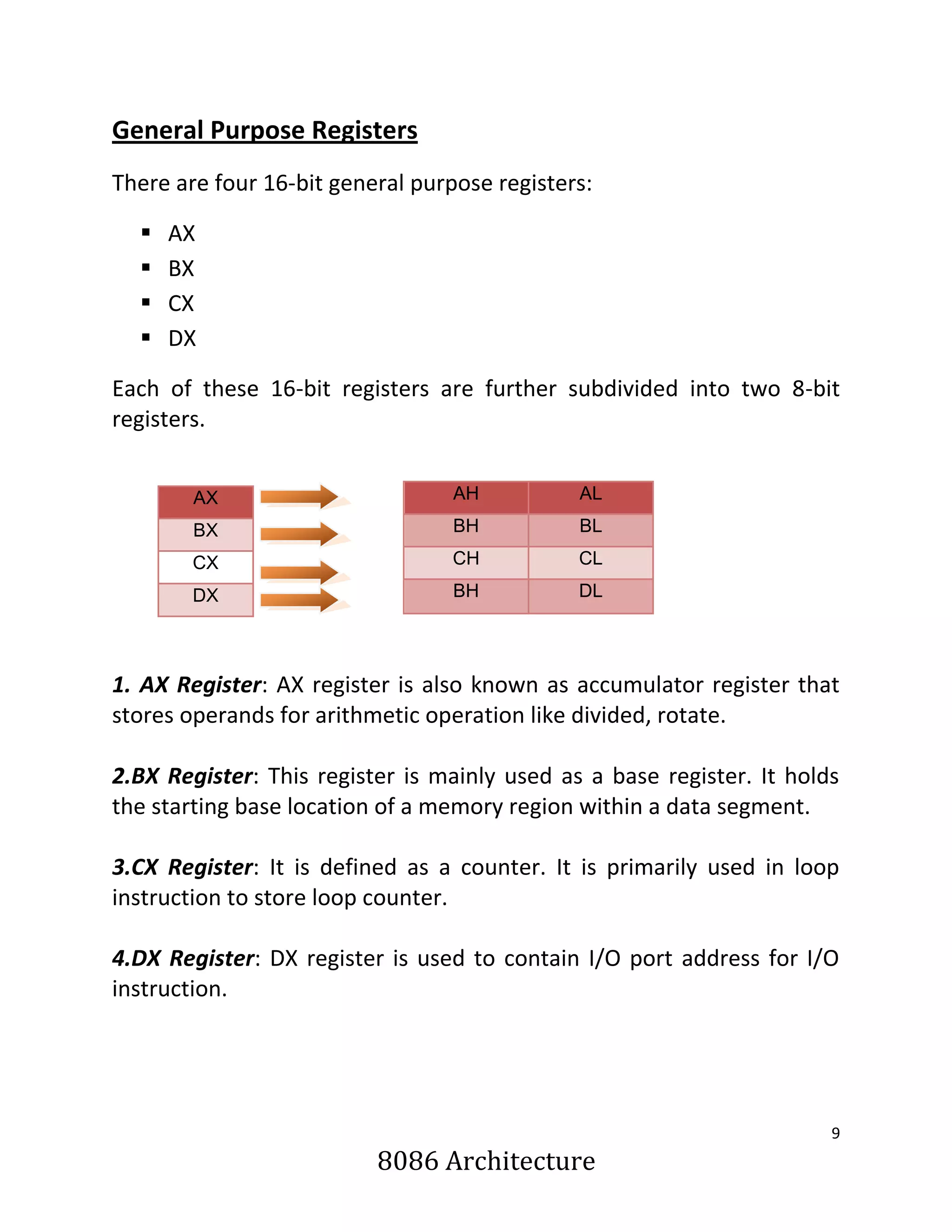

The 8086 is a 16-bit microprocessor chip designed by Intel in the late 1970s. It had a 16-bit internal data bus, 20-bit address bus, and was separated into a Bus Interface Unit and Execution Unit to improve performance via instruction pipelining. The BIU fetched instructions and operands from memory while the EU executed instructions. The 8086 used general purpose registers, pointer/index registers, segment registers, and an instruction pointer to support its programming model. It was a significant advancement that helped drive the personal computing revolution.