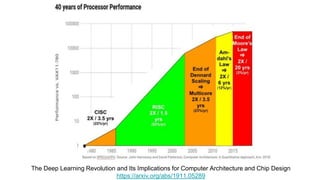

Hardware for deep learning includes CPUs, GPUs, FPGAs, and ASICs. CPUs are general purpose but support deep learning through instructions like AVX-512 and libraries. GPUs like NVIDIA and AMD models are commonly used due to high parallelism and memory bandwidth. FPGAs offer high efficiency but require specialized programming. ASICs like Google's TPU are customized for deep learning and provide high performance but limited flexibility. Emerging hardware aims to improve efficiency and better match neural network computations.

![Typically multi-core even on the desktop market:

● usually from 2 to 10 cores in modern Core i3-i9 Intel CPUs

● up to 18 cores/36 threads in high-end Intel CPUs (i9–

7980XE/9980XE/10980XE) [https://en.wikipedia.org/wiki/List_of_Intel_Core_i9_microprocessors]

● up to 64 cores/128 threads in AMD Ryzen Threadripper

(Ryzen Threadripper 3990X, Ryzen Threadripper Pro 3995WX)

x86: Desktops](https://image.slidesharecdn.com/aihardwarelandscape2021-210205124043/85/AI-Hardware-Landscape-2021-5-320.jpg)

![ASIC: Intel (Nervana) NNP-T [discontinued]

Processor for training. Can build PODs (say 10-rack POD with 480 NNP-T)

● 24 Tensor Processing Cluster (TPC)

● PCIe Gen 4 x16 accelerator card, 300W

● OCP Accelerator Module, 375W

● 119 TOPS bfloat16

● 32 GB HBM2

https://www.intel.ai/nervana-nnp/nnpt/

https://en.wikichip.org/wiki/nervana/microarchitectures/spring_crest](https://image.slidesharecdn.com/aihardwarelandscape2021-210205124043/85/AI-Hardware-Landscape-2021-48-320.jpg)

![ASIC: Intel (Nervana) NNP-I [discontinued]

Processor for inference using mixed precision math, with a special emphasis on low-precision

computations using INT8.

● 12 inference compute engines (ICE) + 2 Intel architecture cores (AVX+VNNI)

● M.2 form factor (1 chip): 12W, up to 50 TOPS.

● PCIe card (2 chips): 75W, up to 170 TOPS.

https://www.intel.ai/nervana-nnp/nnpi

https://en.wikichip.org/wiki/intel/microarchitectures/spring_hill](https://image.slidesharecdn.com/aihardwarelandscape2021-210205124043/85/AI-Hardware-Landscape-2021-49-320.jpg)