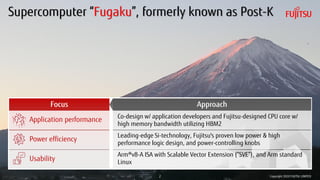

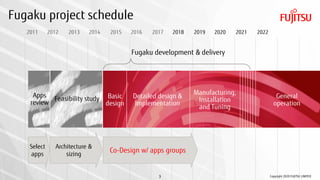

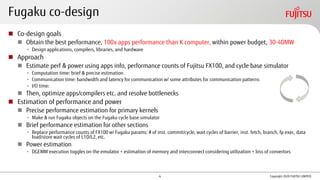

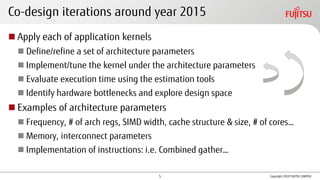

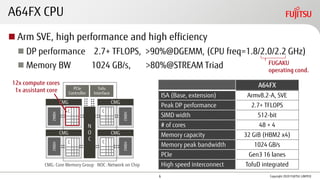

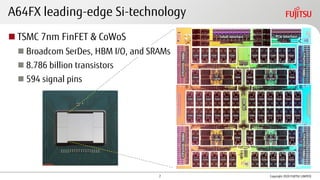

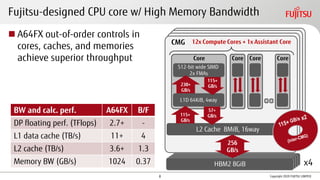

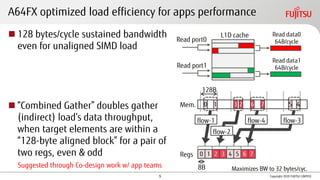

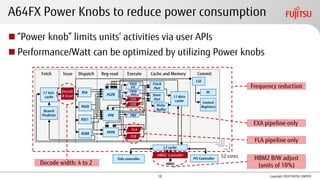

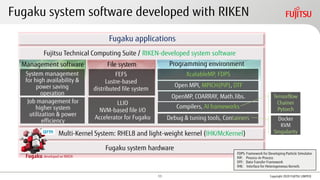

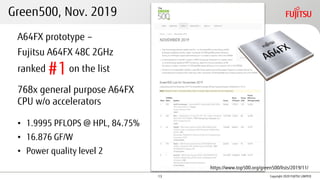

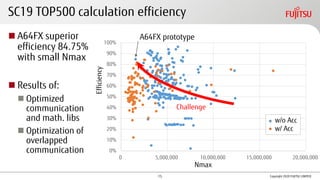

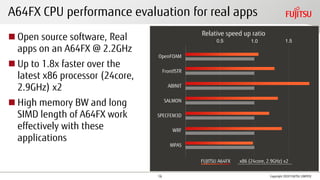

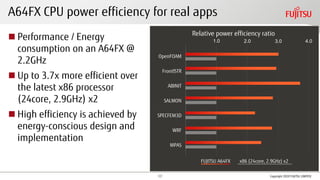

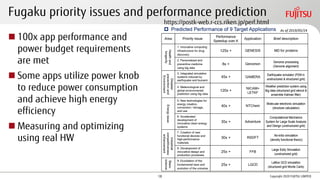

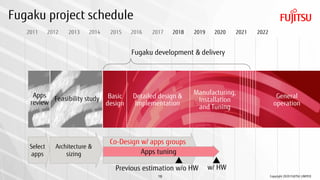

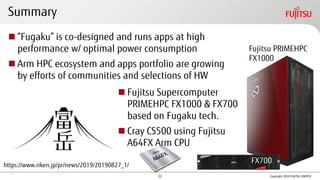

Fugaku is a Japanese supercomputer utilizing Fujitsu's A64FX CPU. It was designed through an iterative co-design process between application developers and Fujitsu to achieve over 100x performance gain compared to the previous K computer within a 30-40MW power budget. The A64FX CPU utilizes 7nm technology and features 48 Arm-based cores with high bandwidth memory to achieve superior floating point and memory bandwidth performance efficiently. Early evaluations show Fugaku meeting performance and power targets and outperforming x86 processors for real applications.