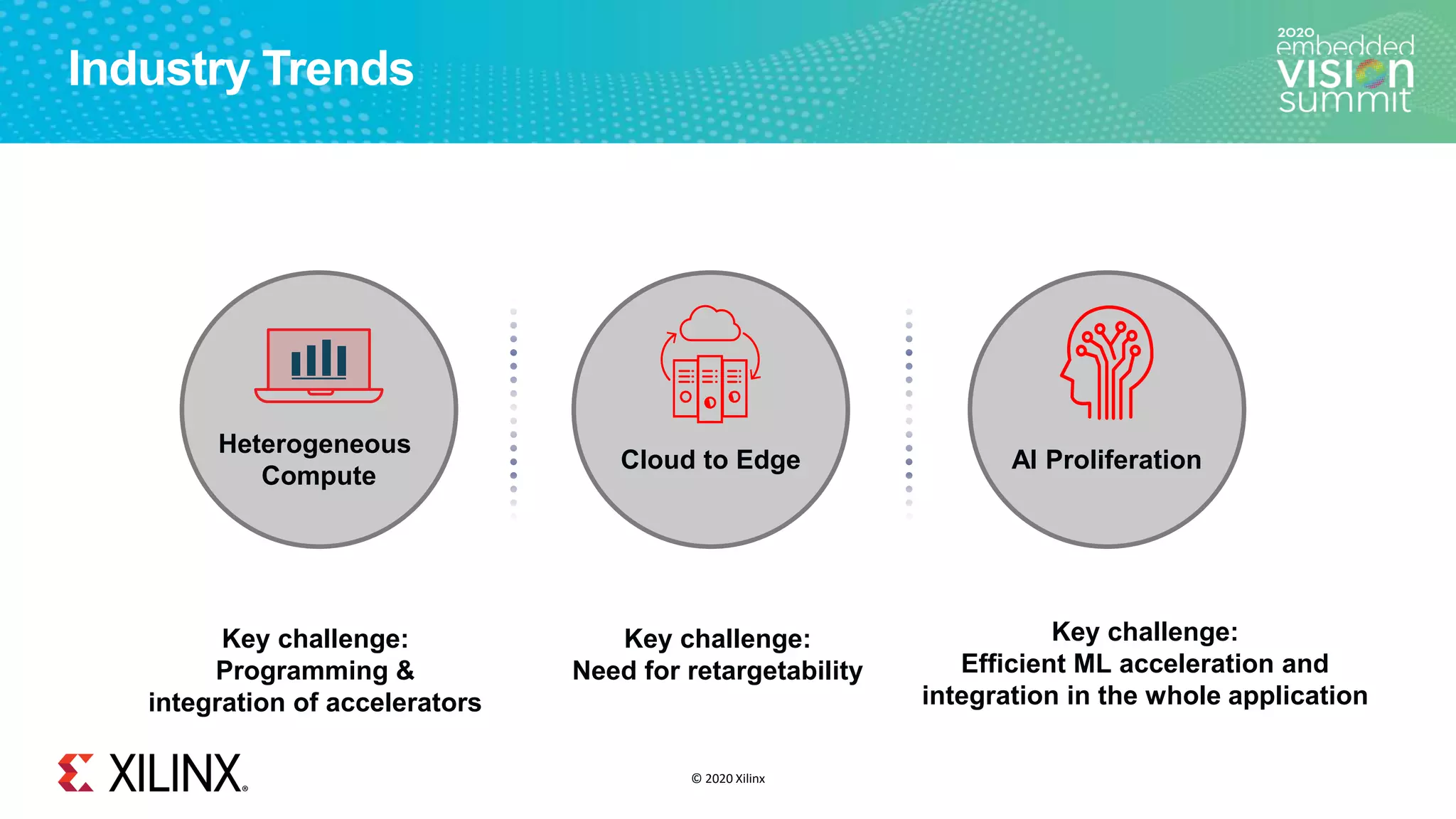

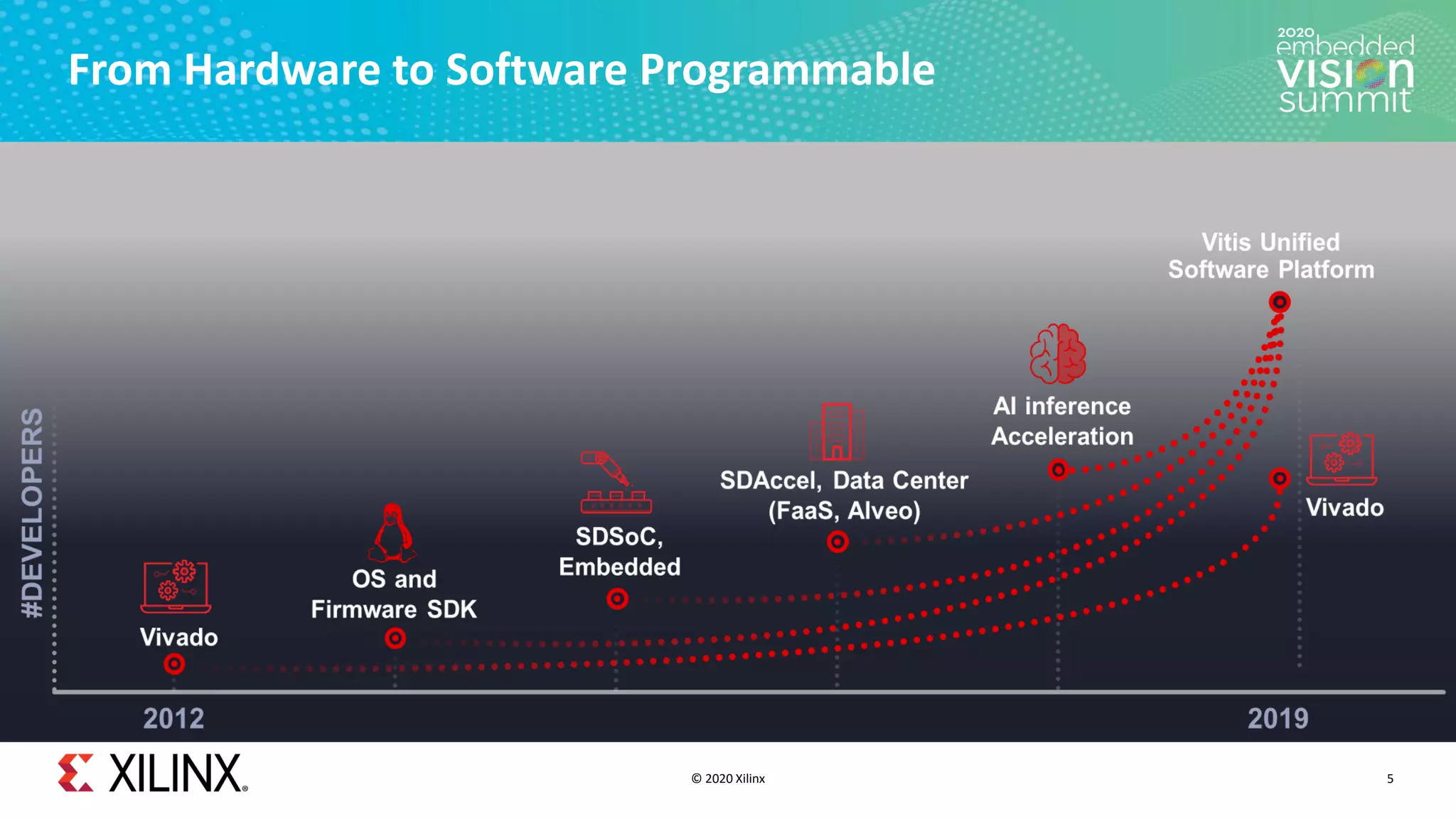

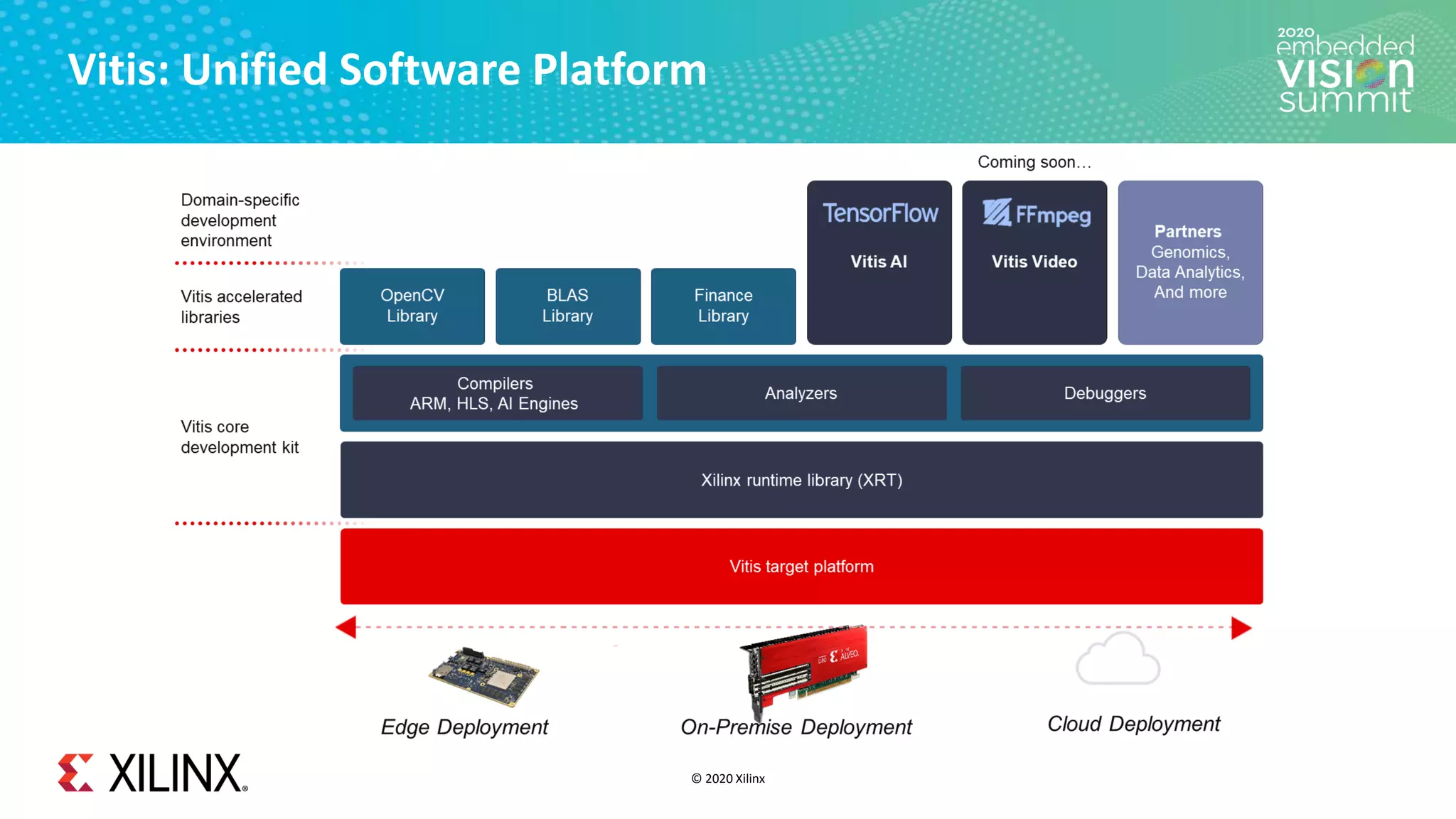

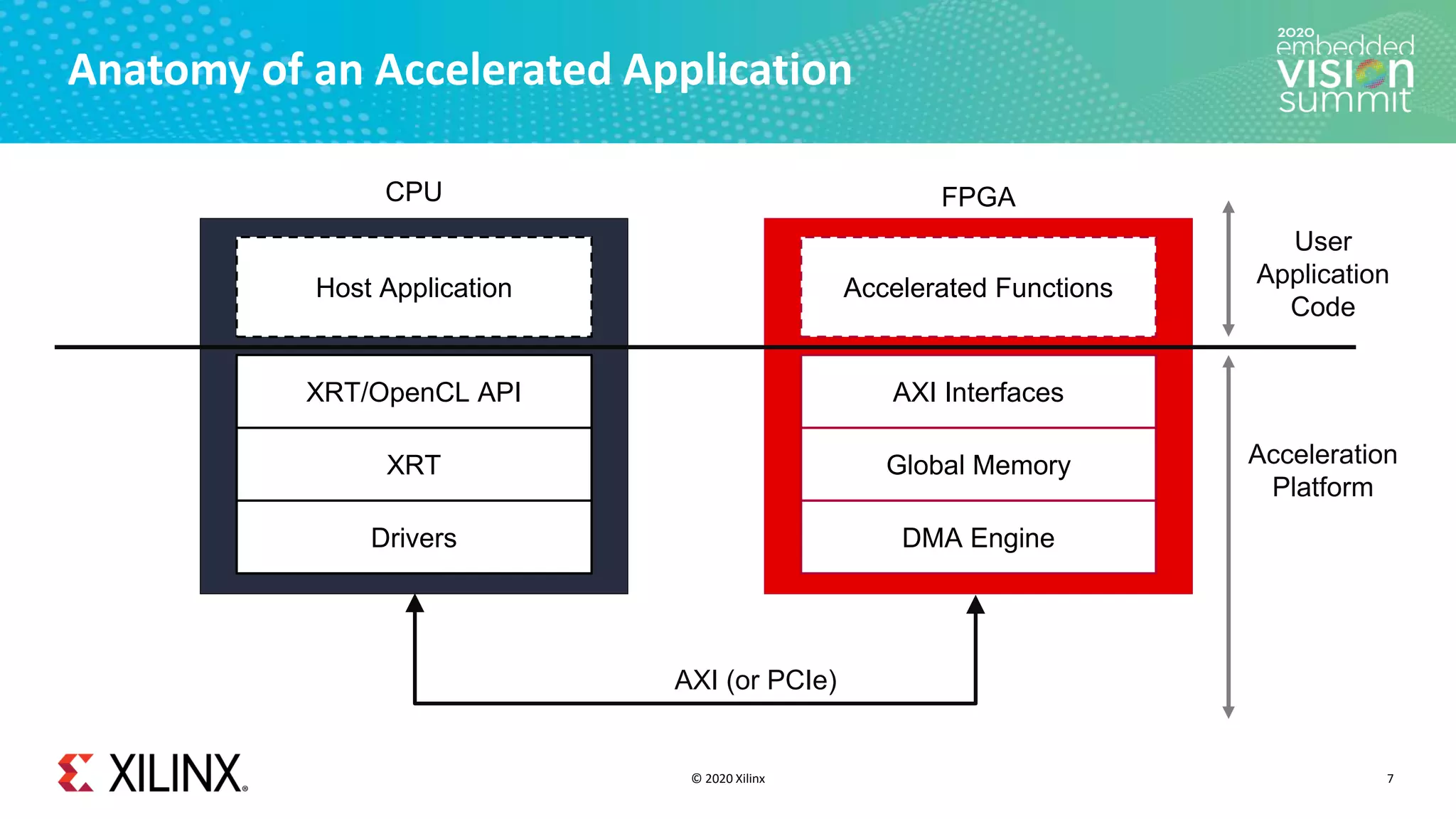

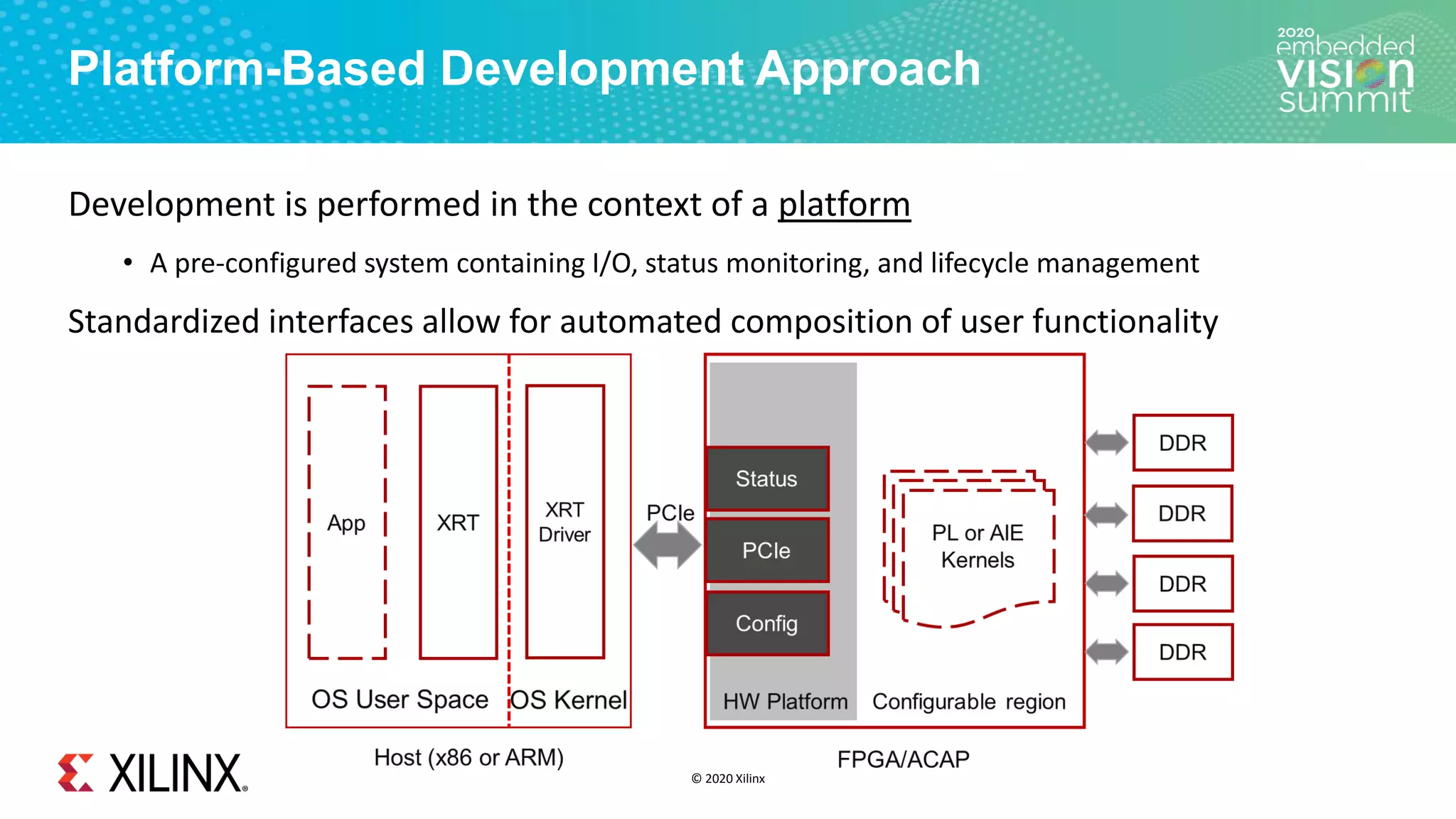

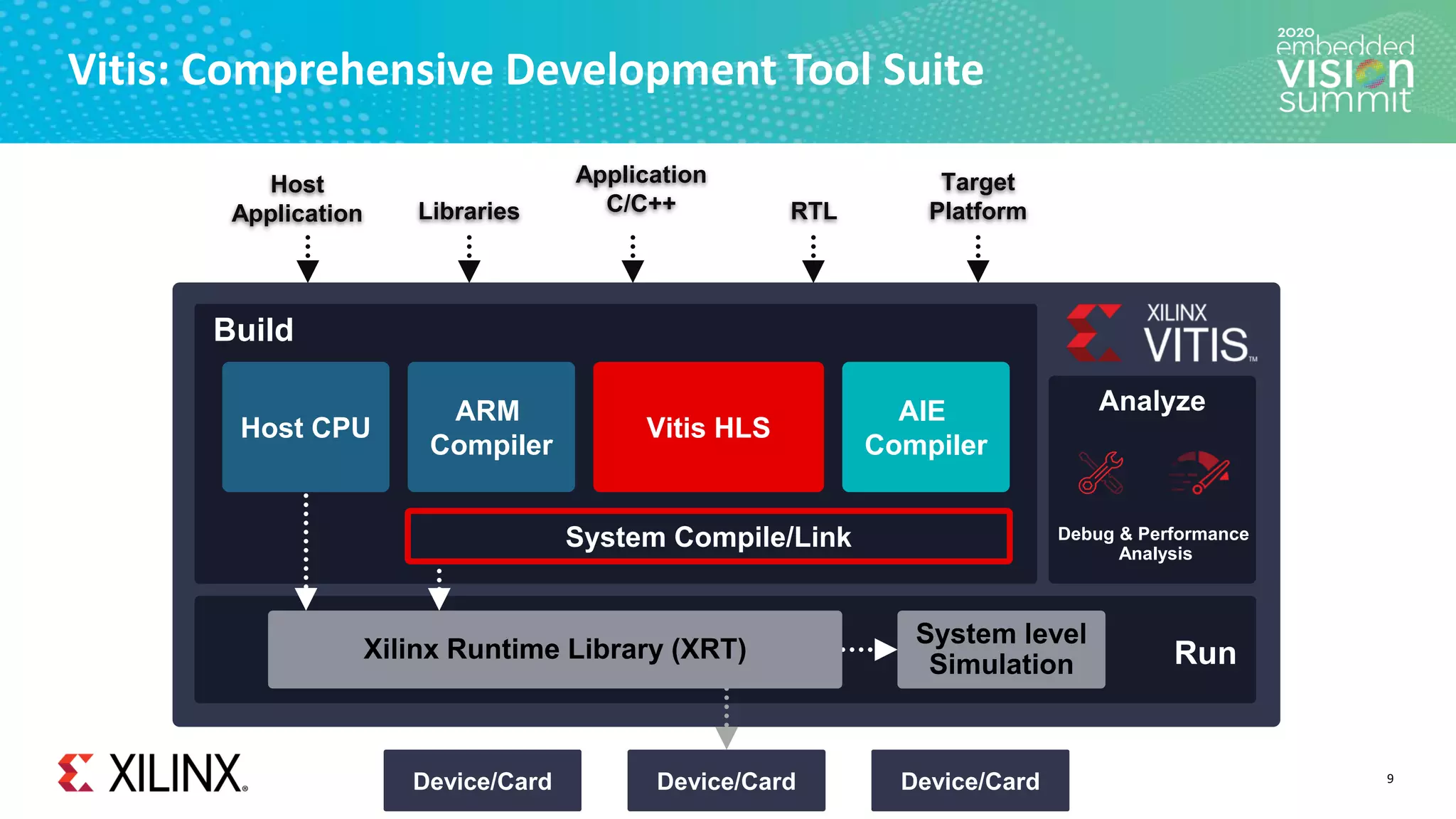

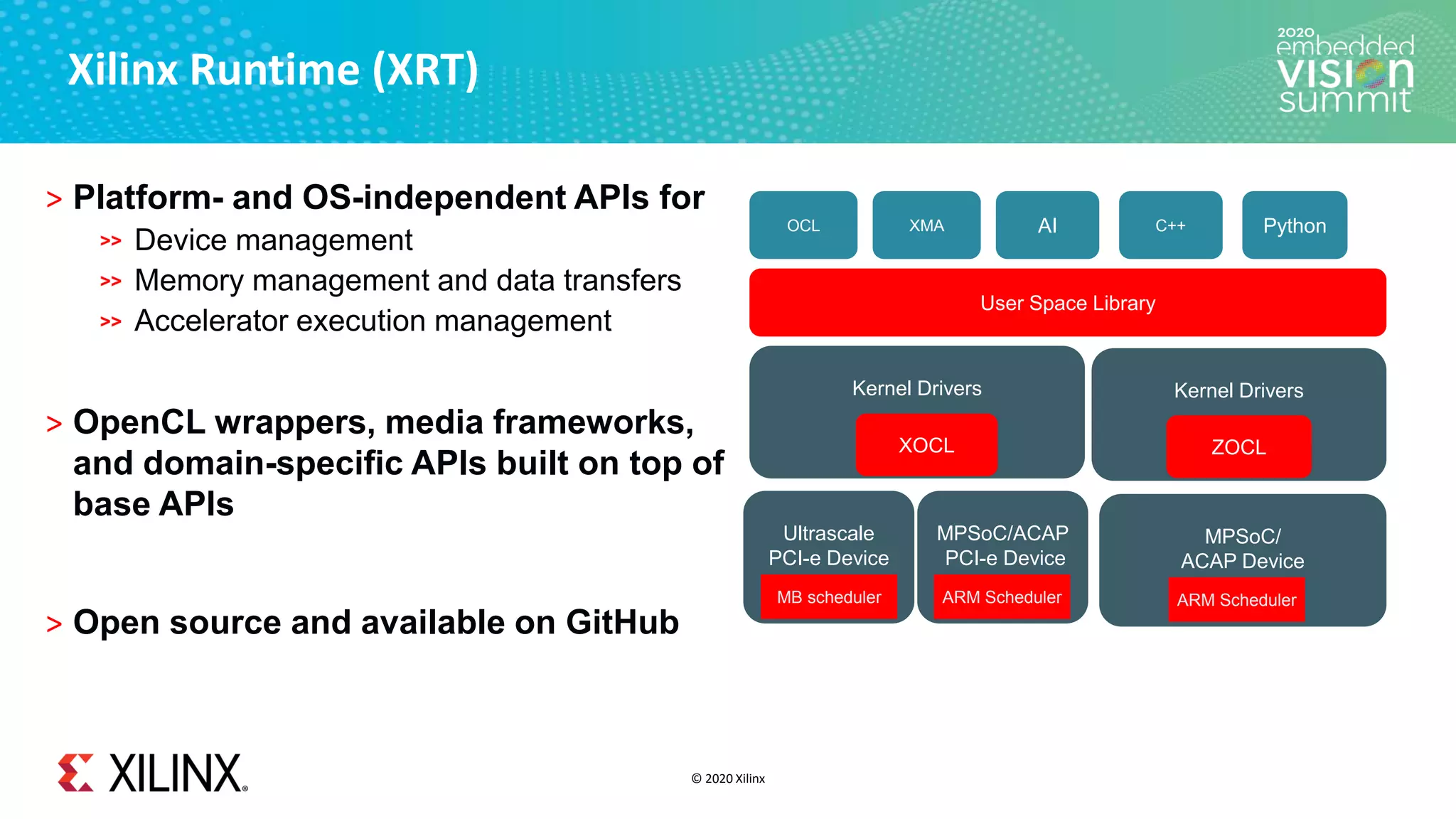

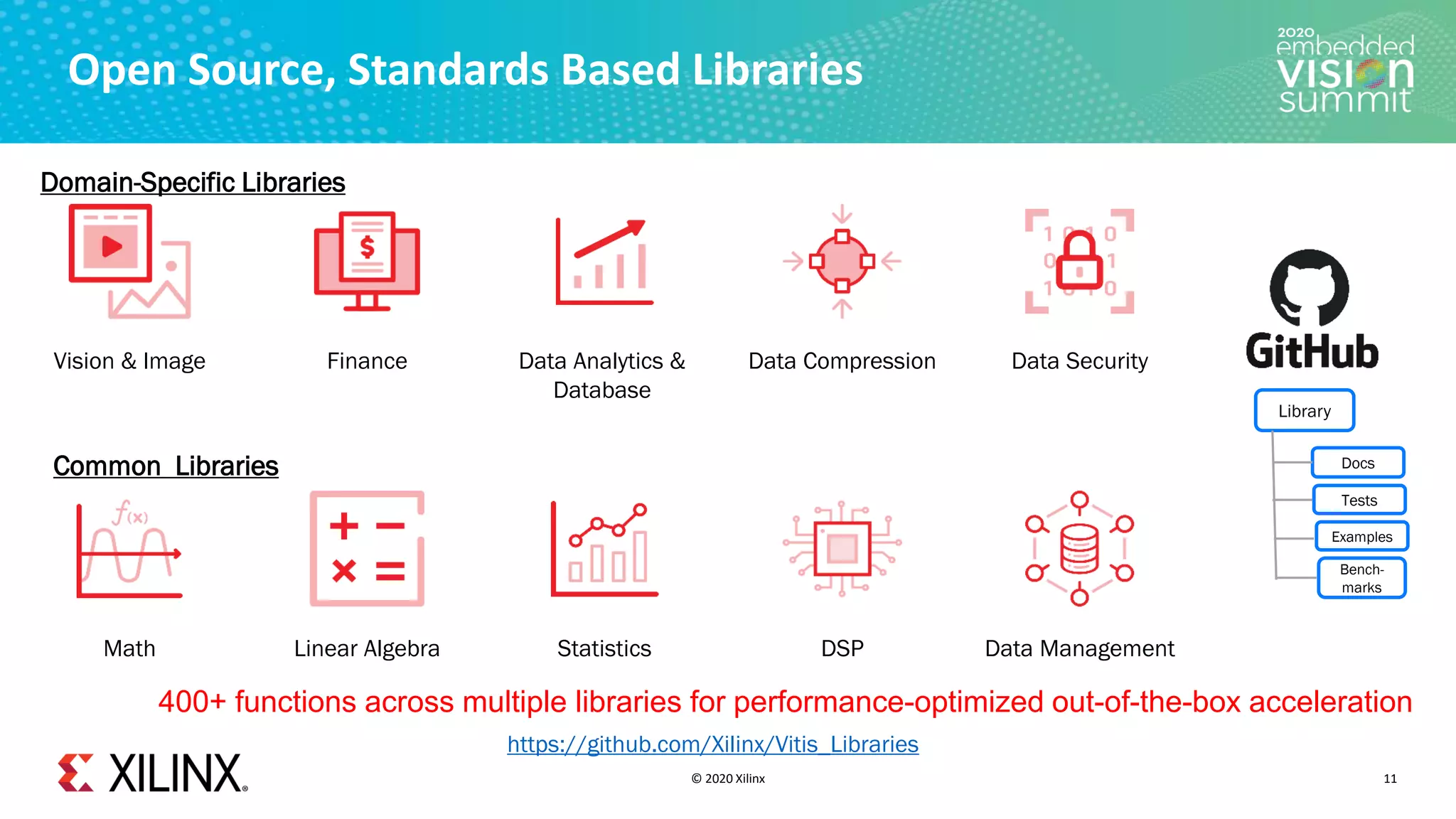

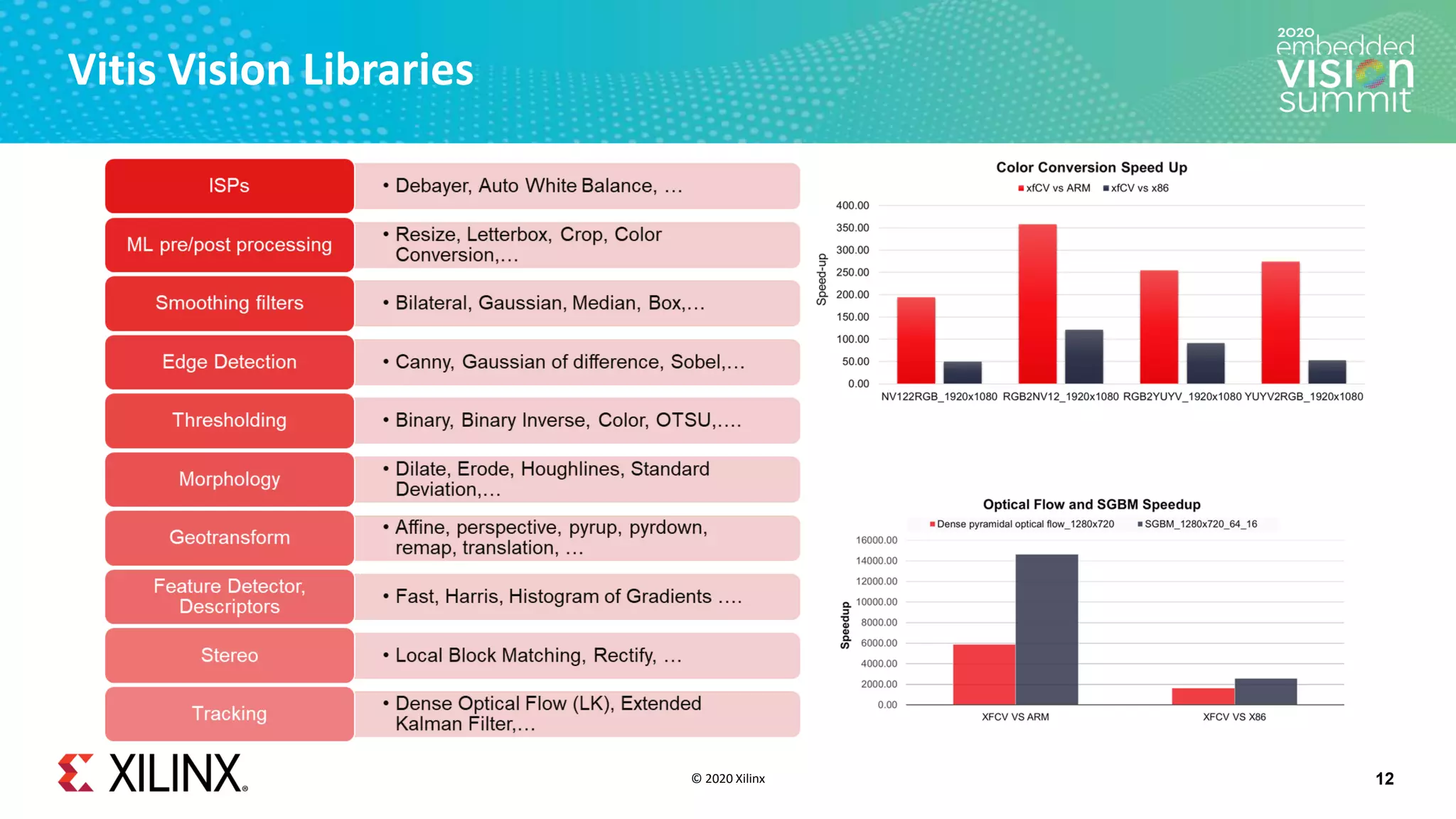

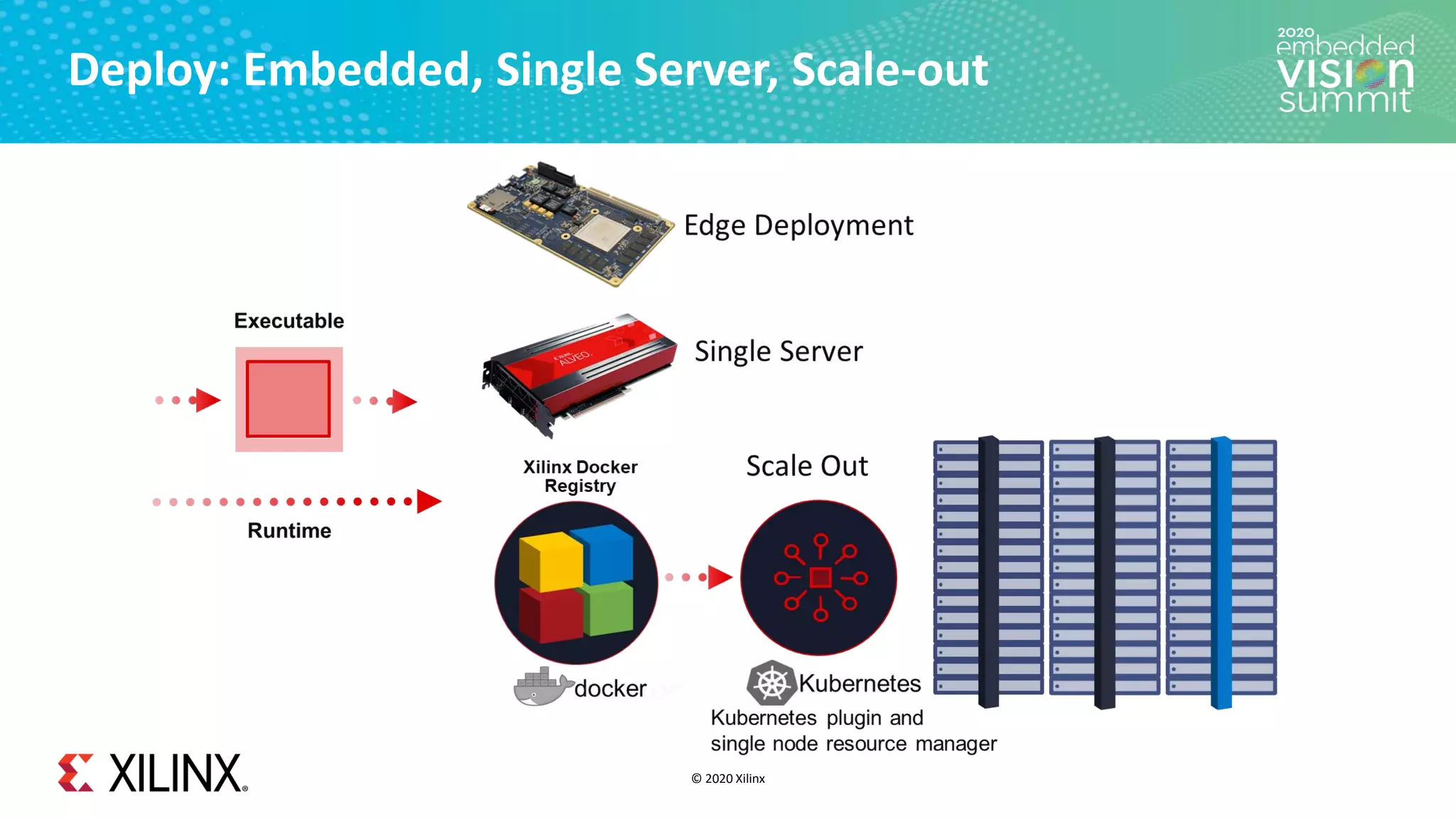

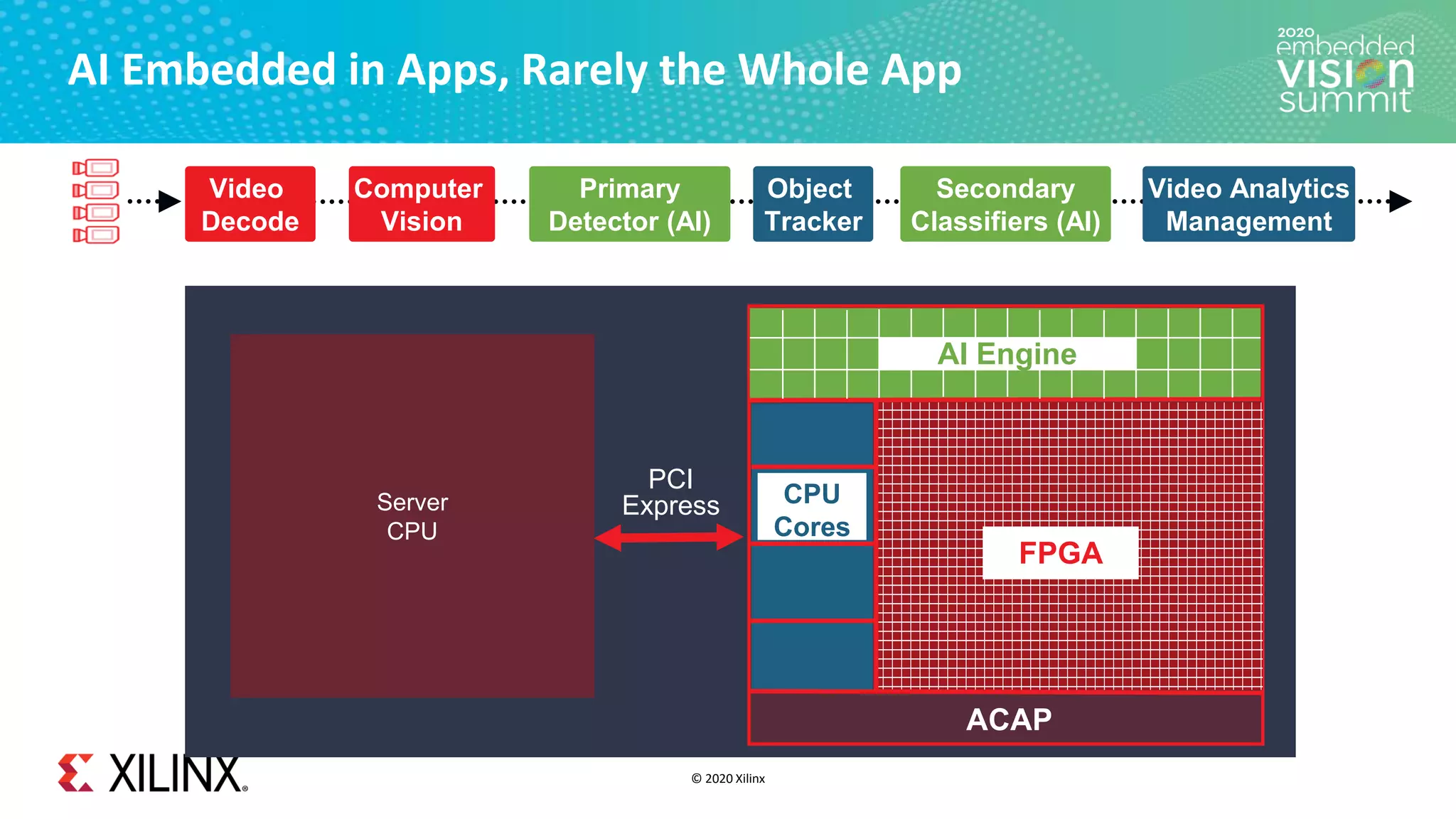

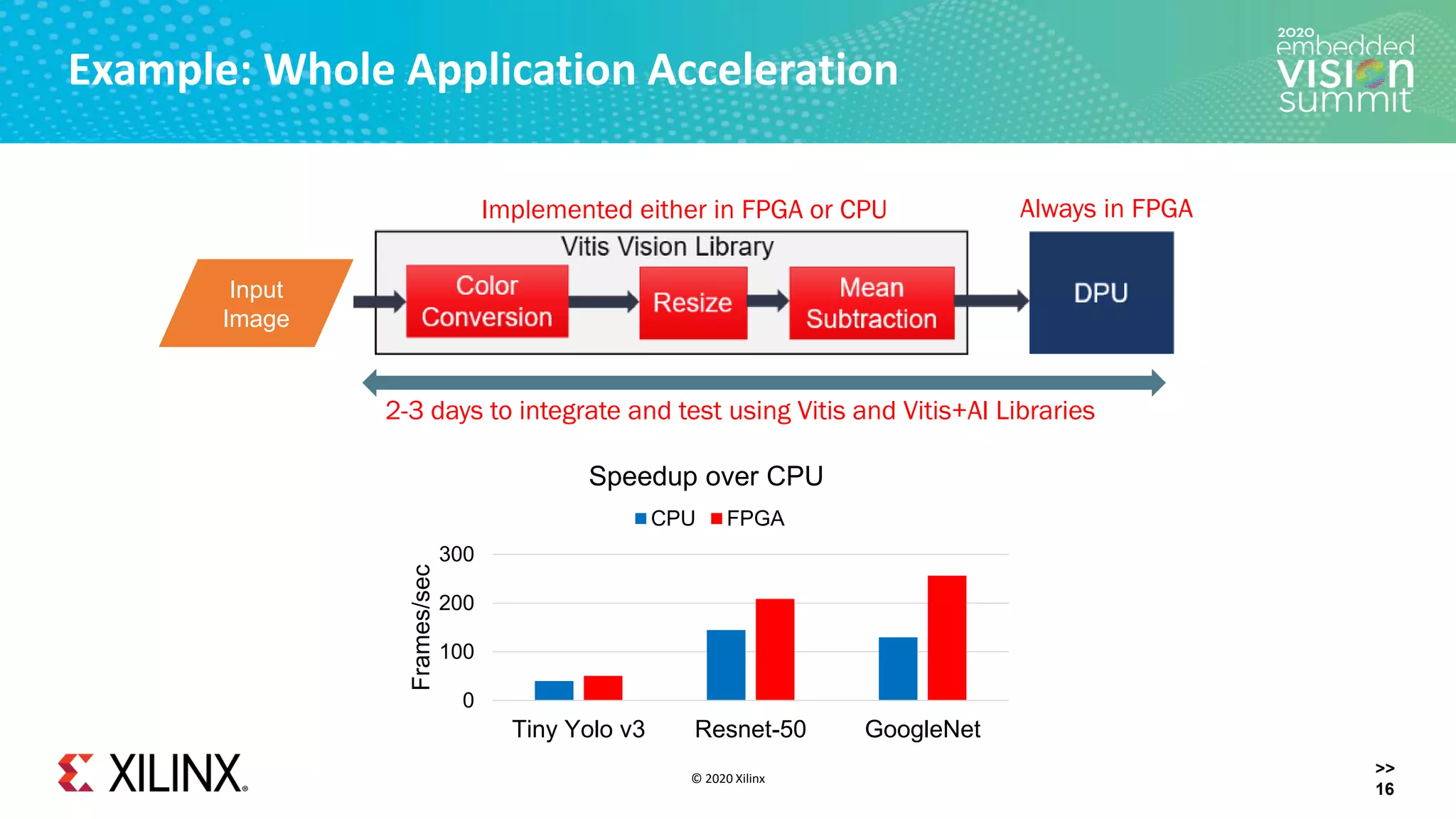

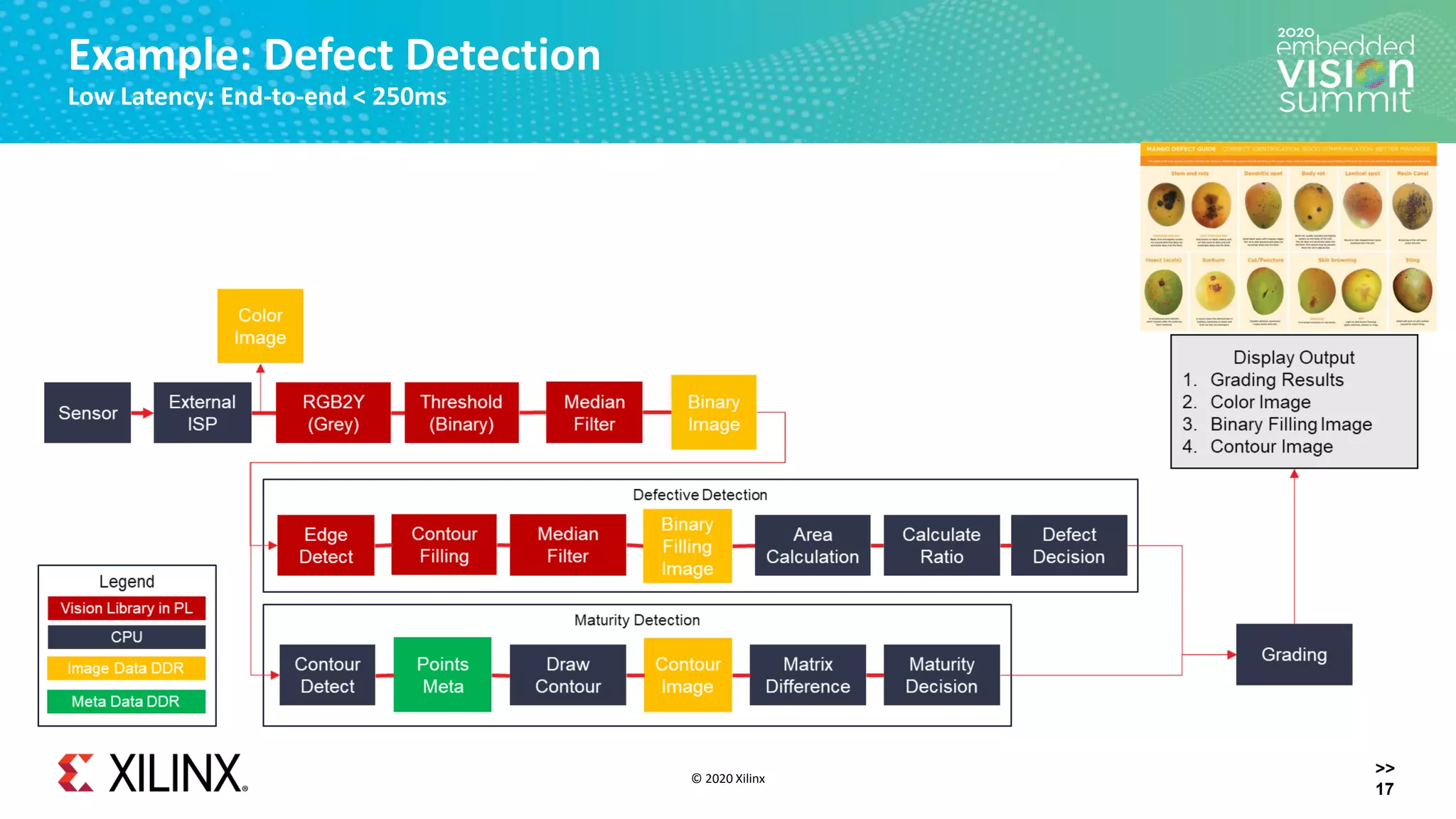

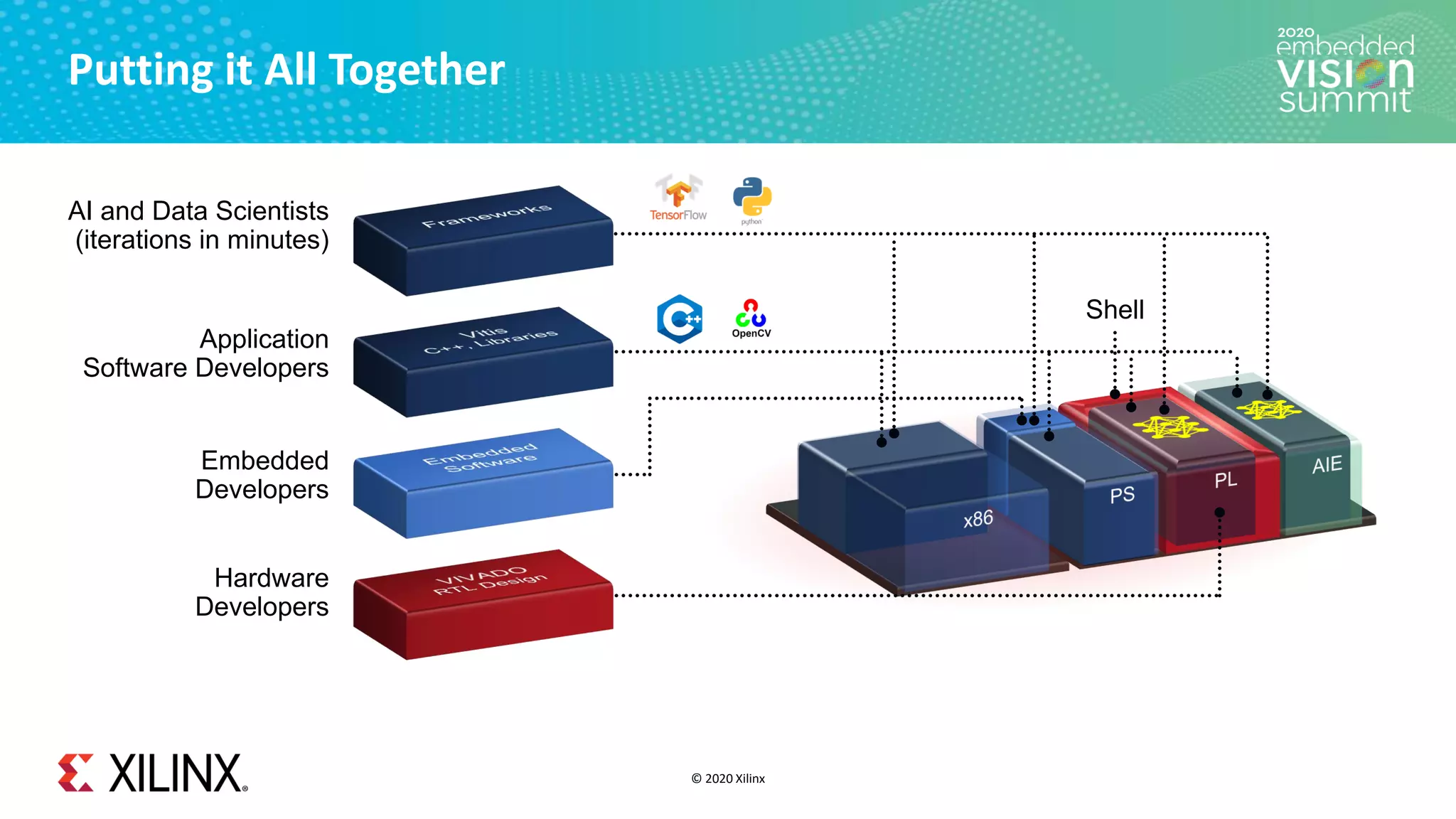

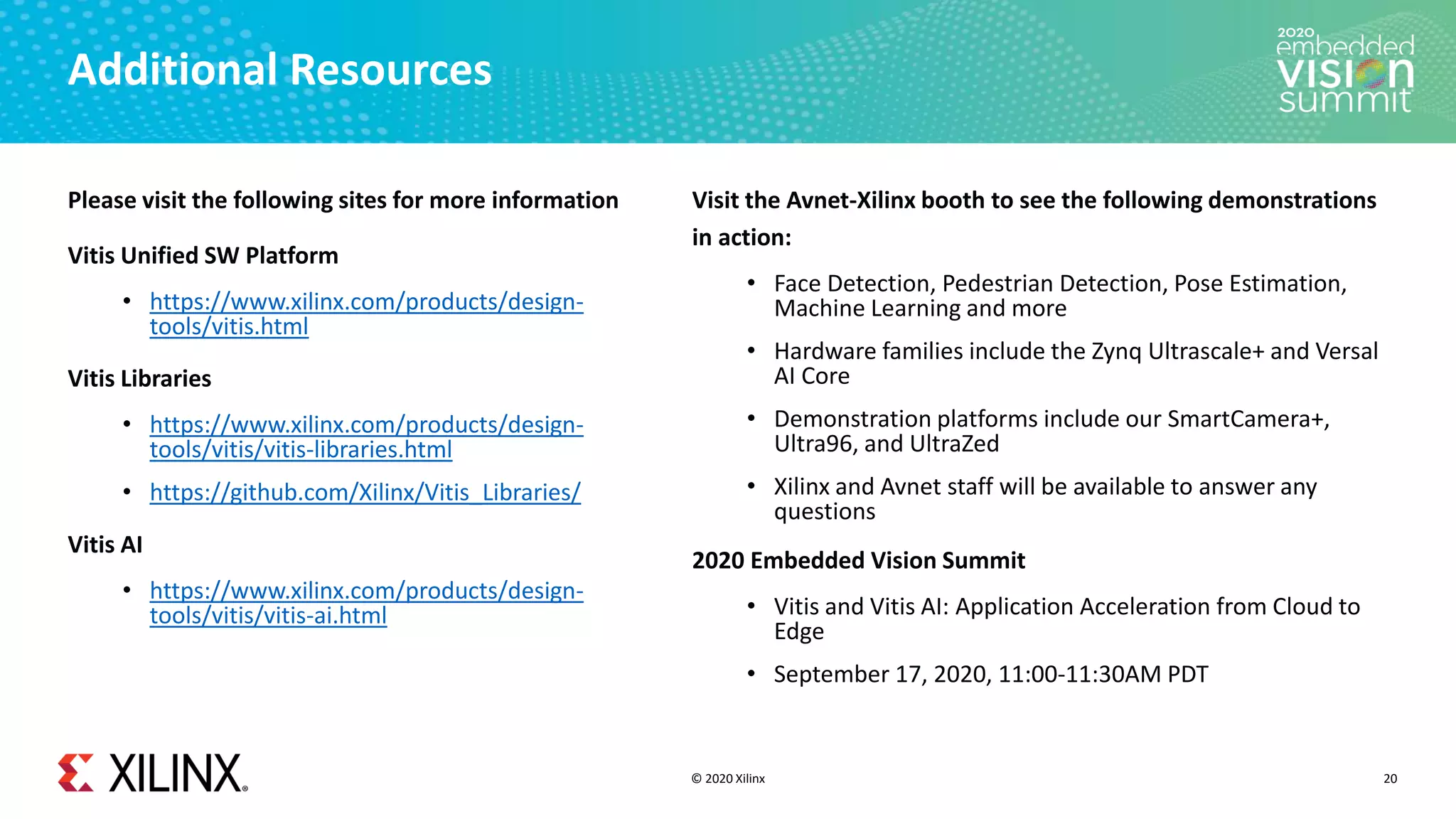

The document describes Xilinx's Vitis and Vitis AI platforms for application acceleration from cloud to edge, highlighting key challenges such as programming integration, retargetability, and efficient machine learning acceleration. It outlines a platform-based development approach, comprehensive development tools, open-source libraries, and various AI models for real-time inference. Additionally, it emphasizes participation in open-source standards and offers resources for further information.