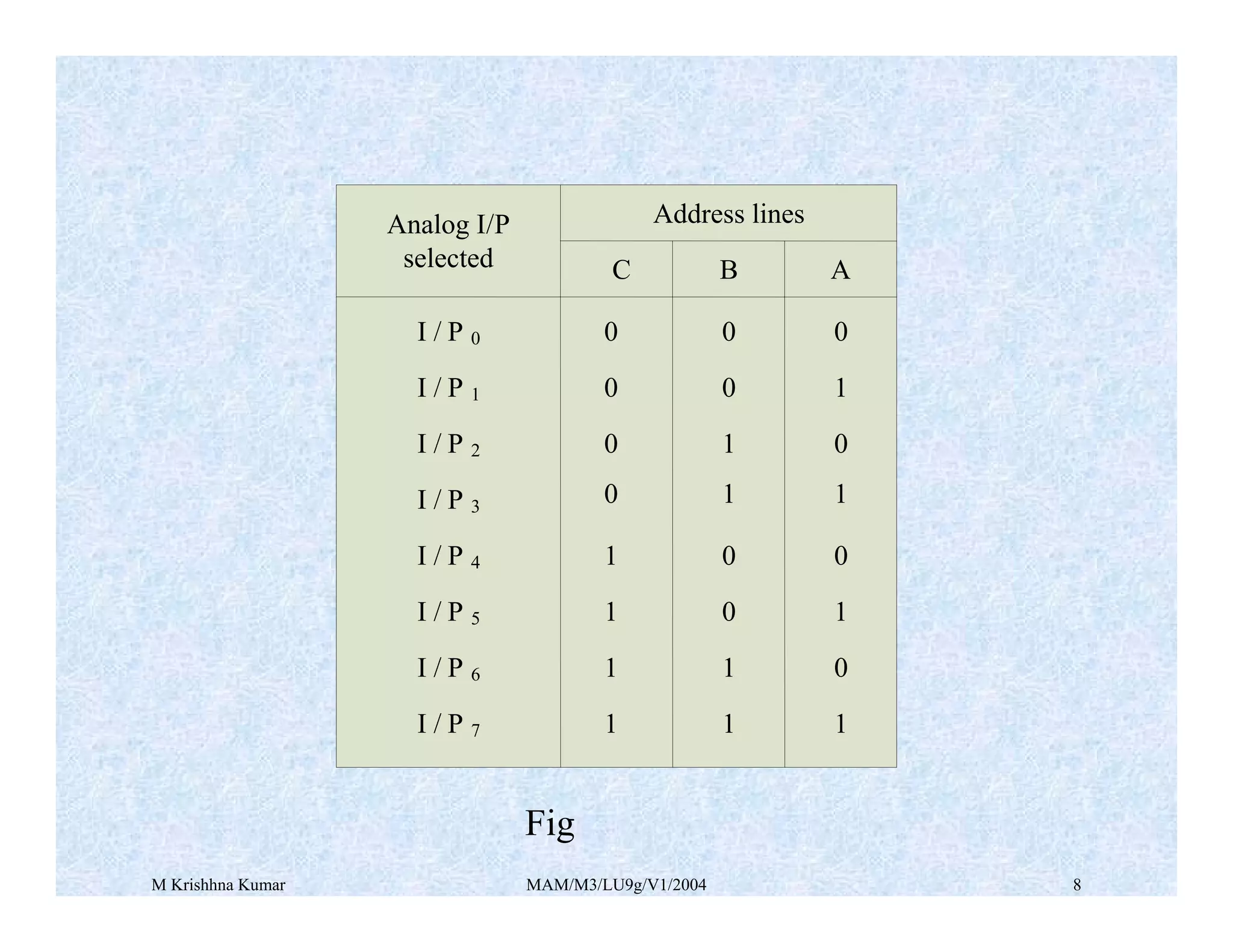

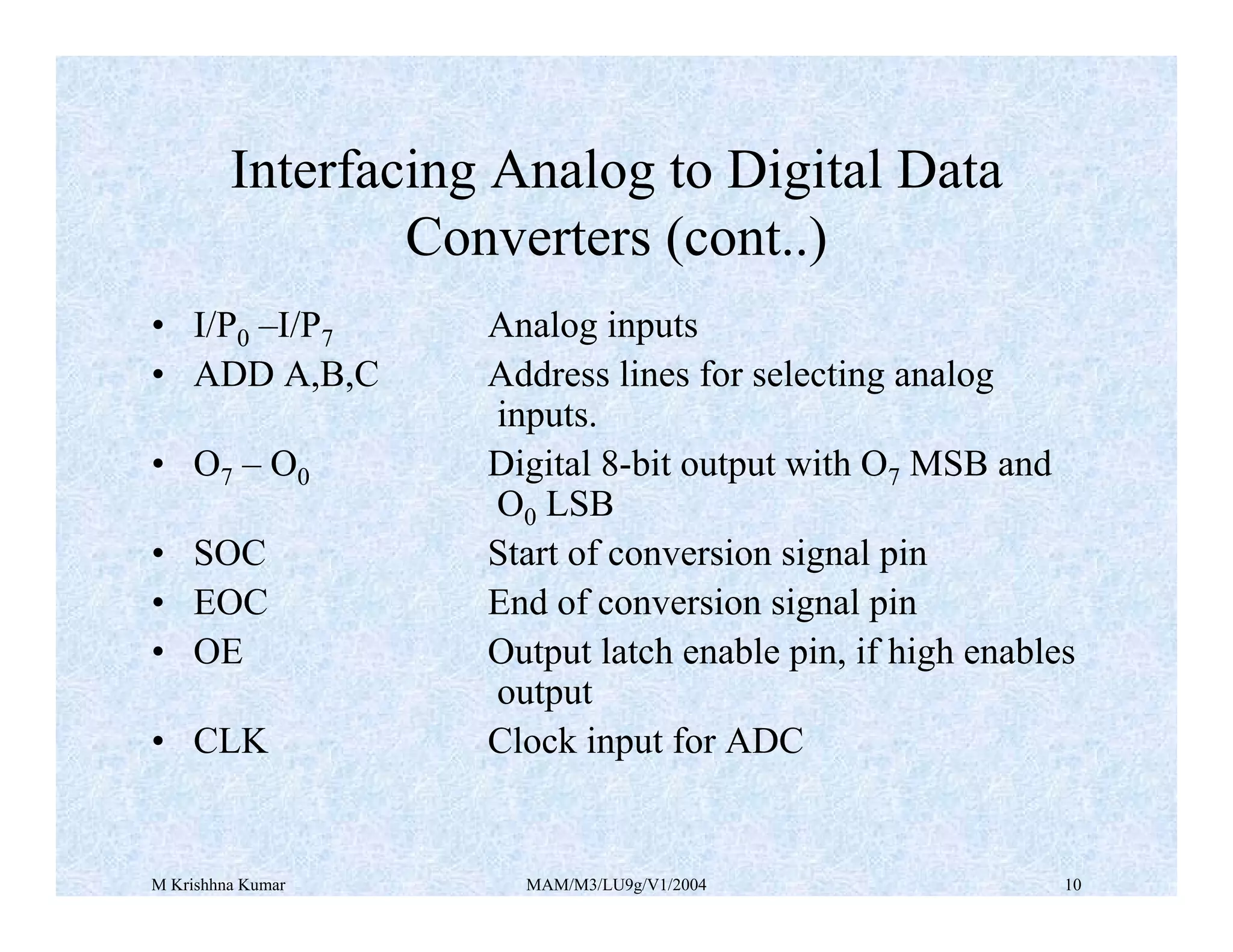

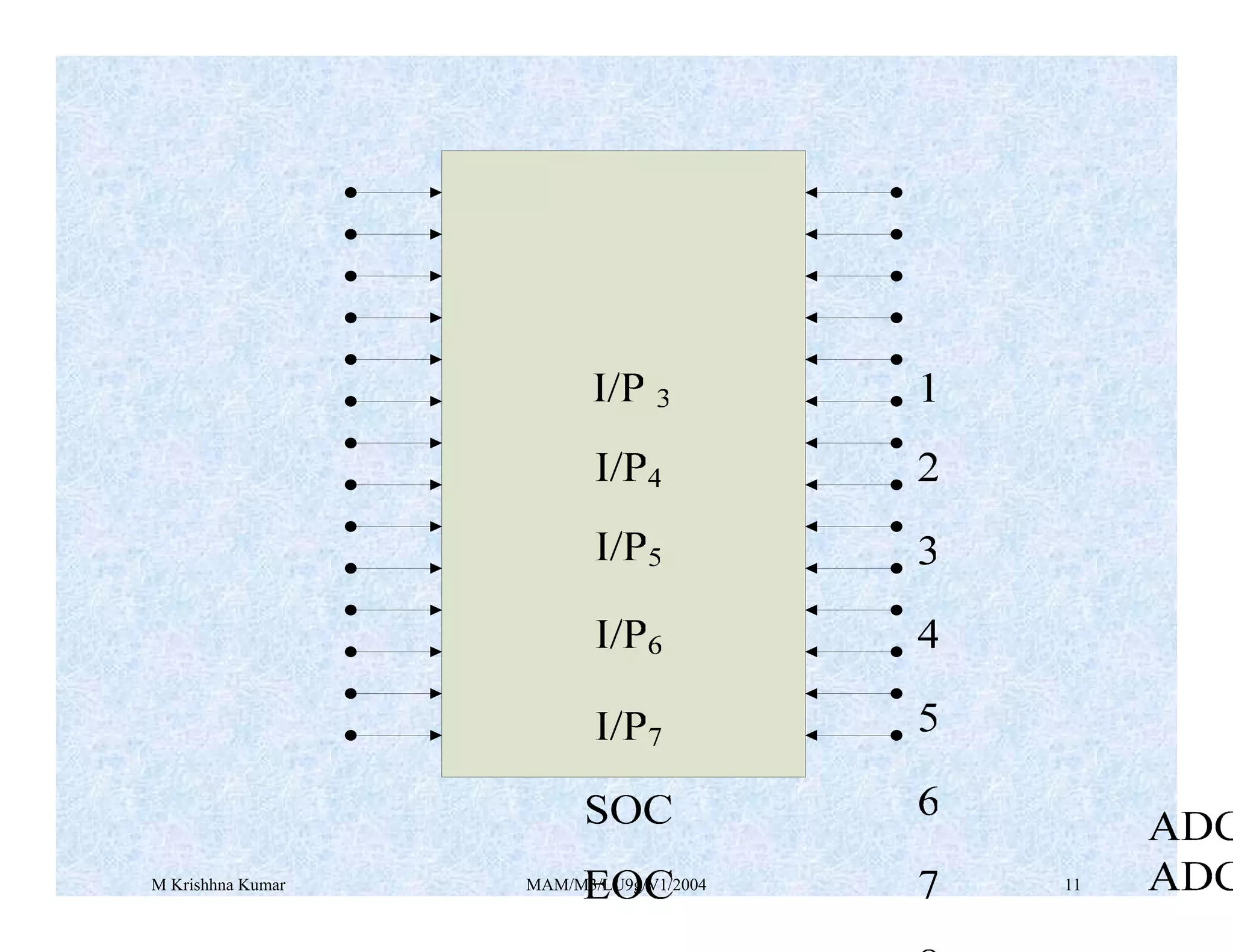

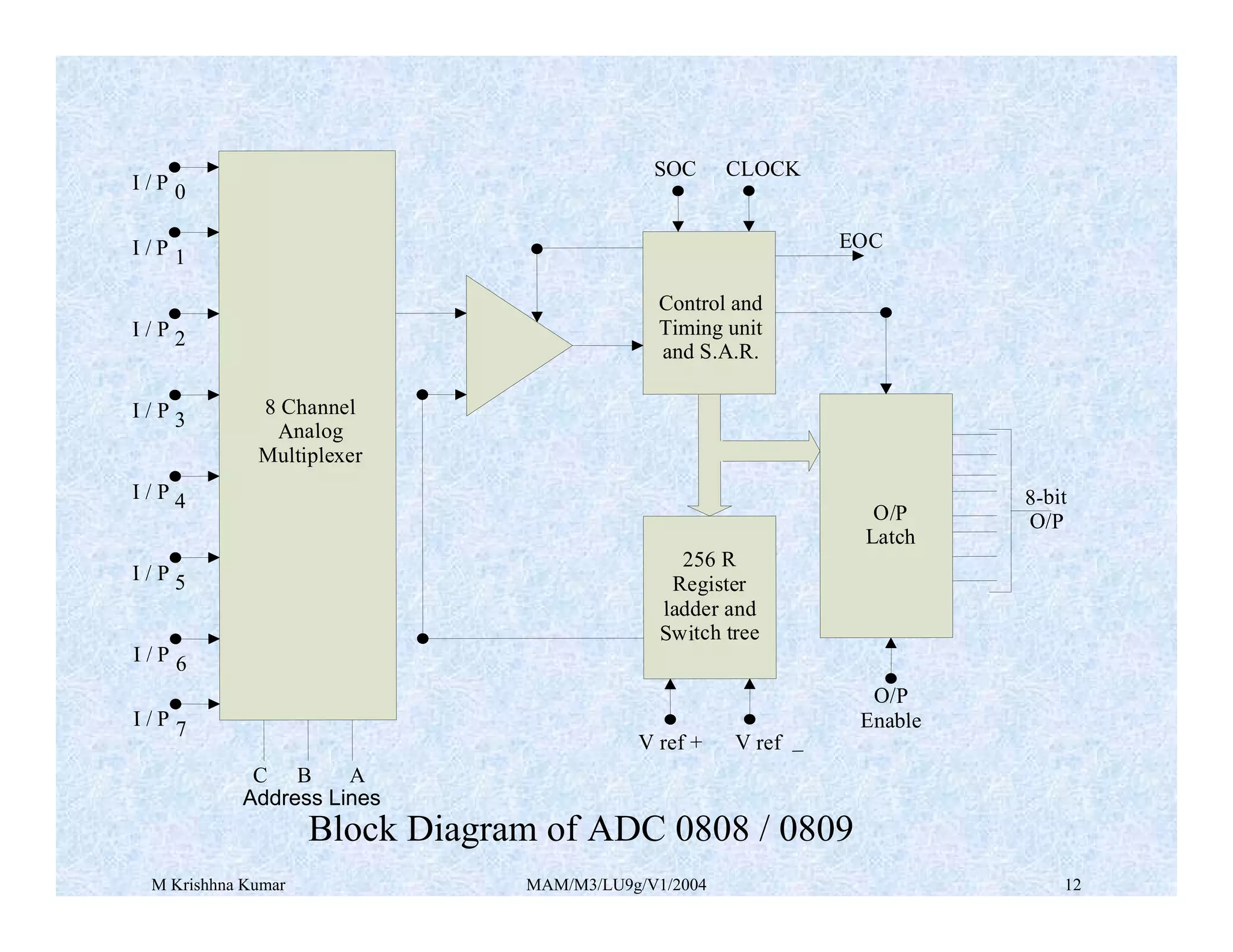

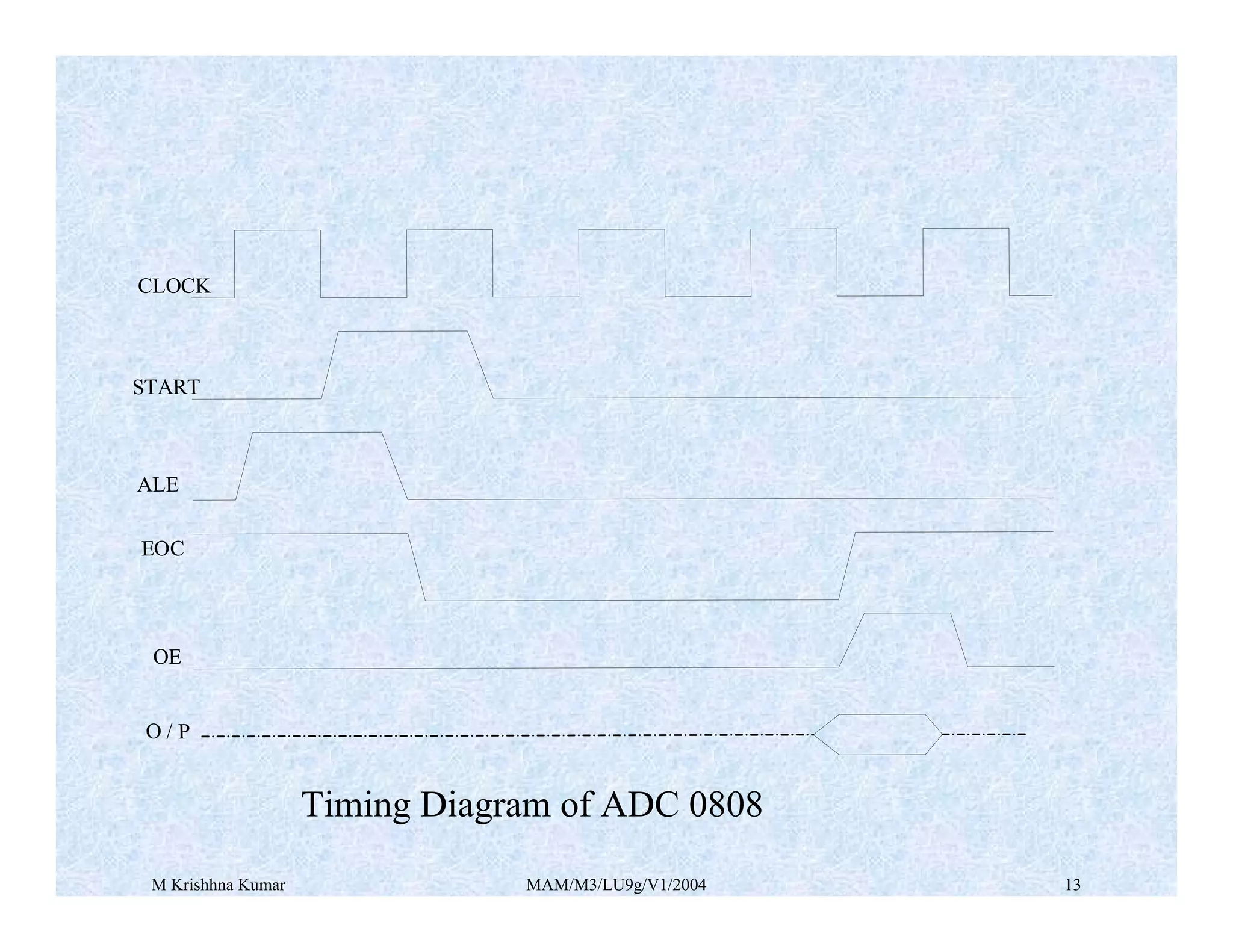

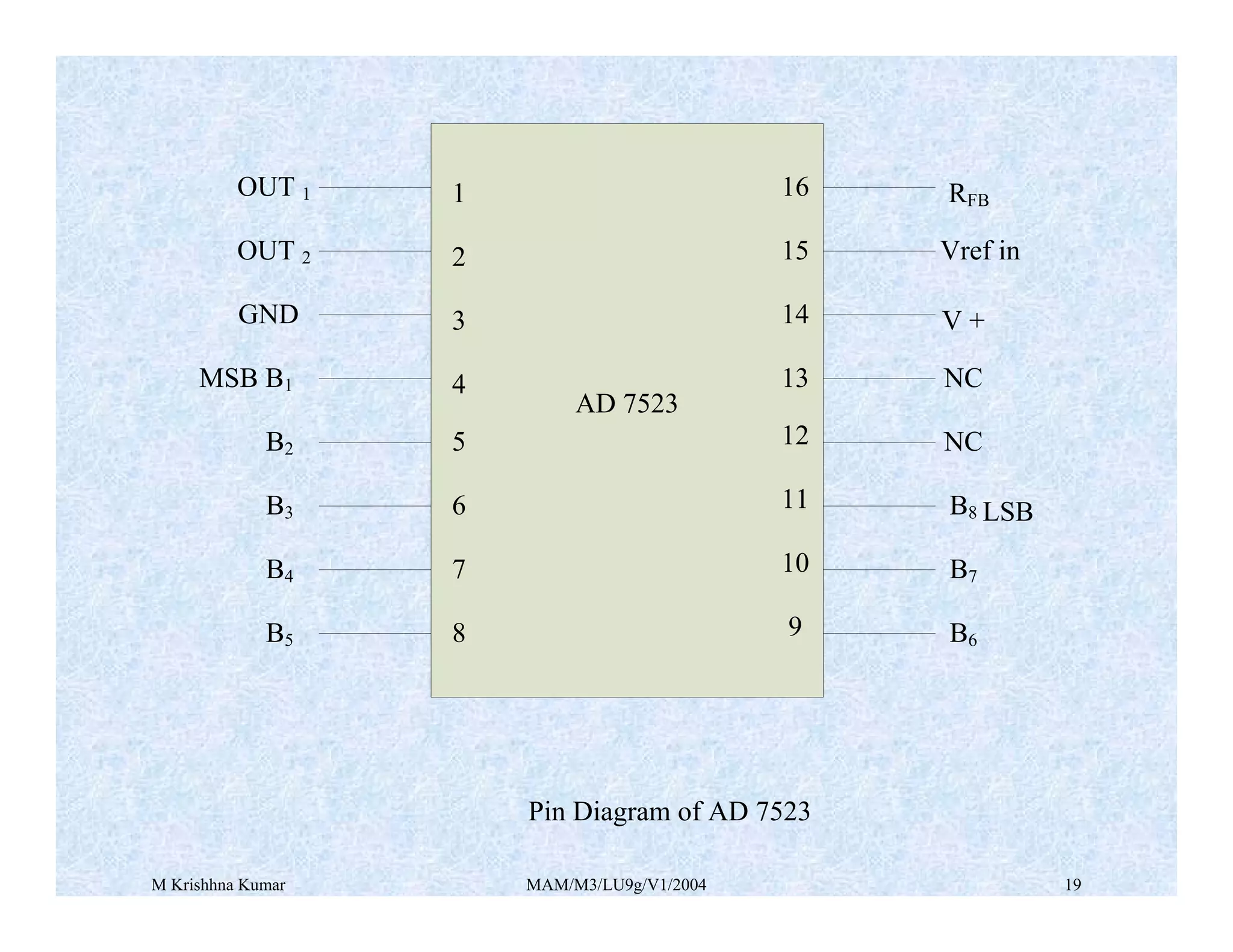

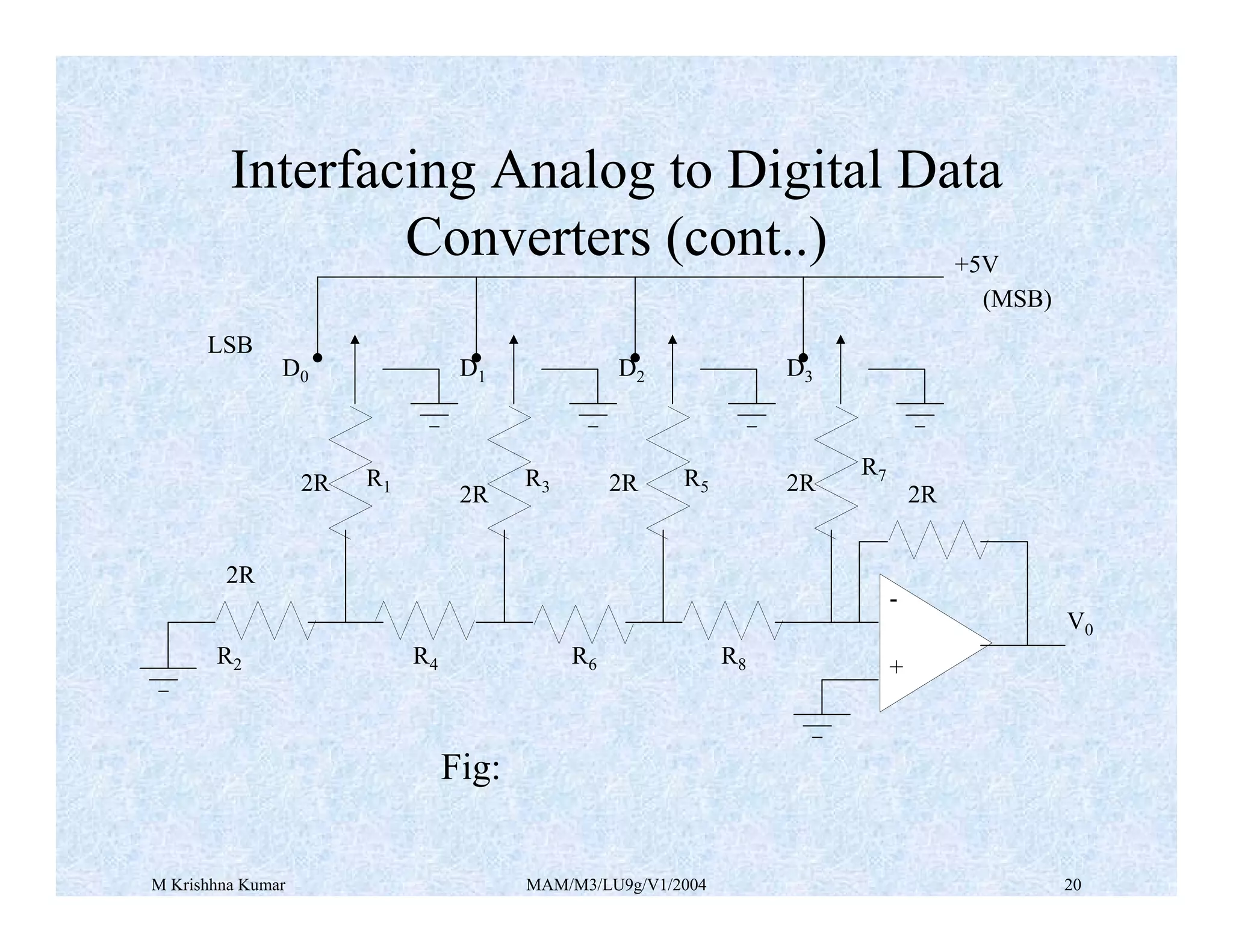

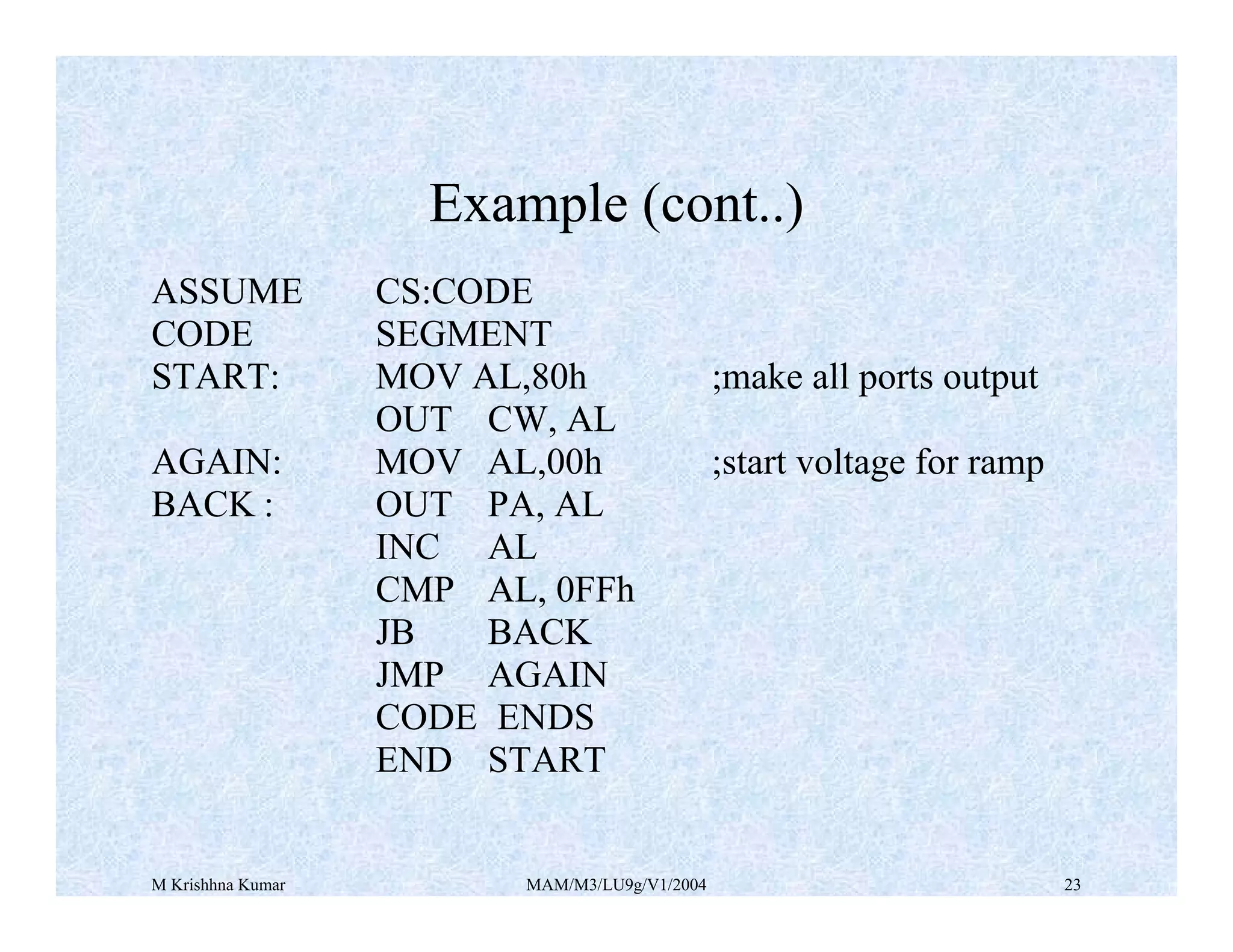

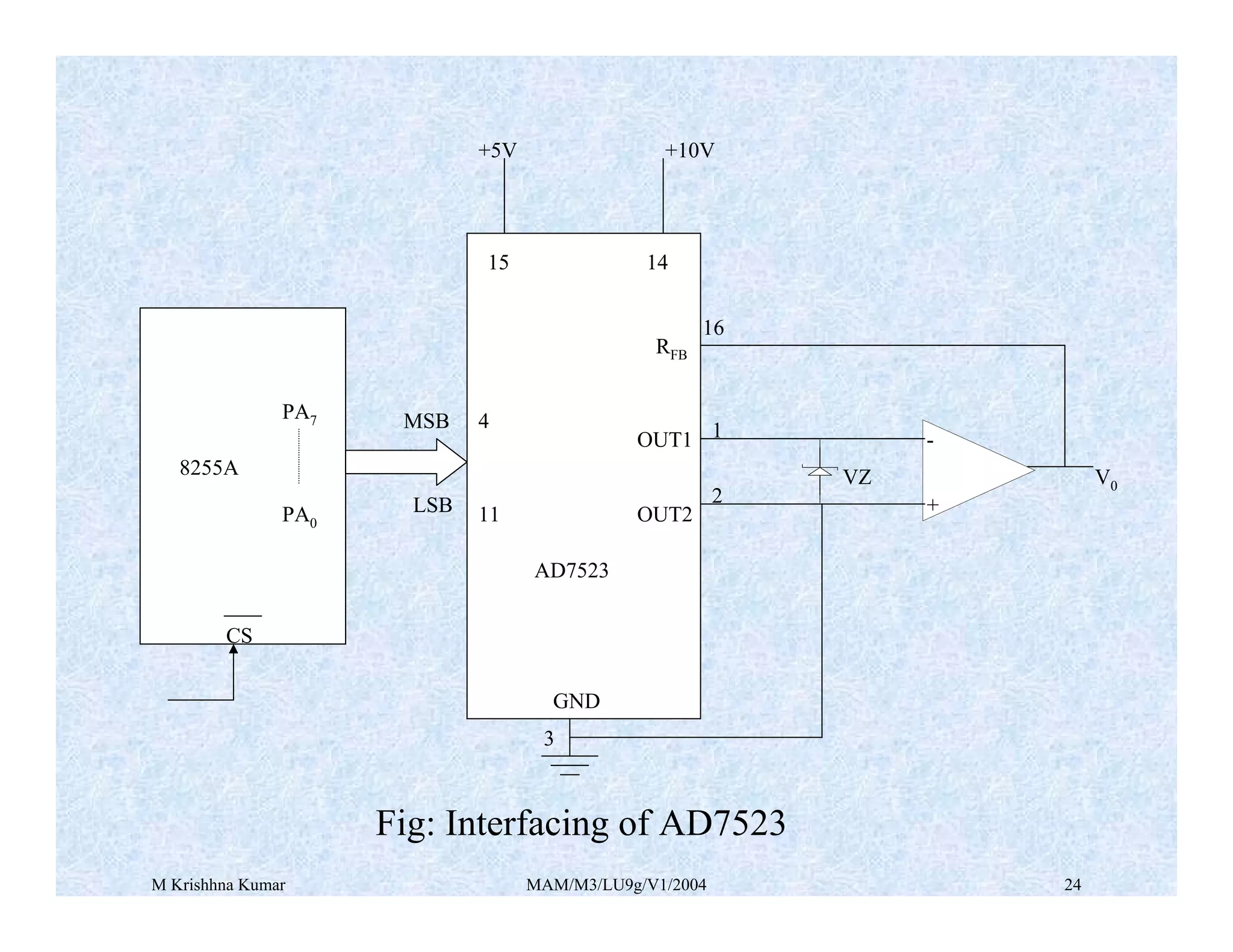

The document discusses interfacing analog to digital converters with microprocessors using the 8255 PIO. It describes how the 8255 is used to issue start of conversion pulses to the ADC and read the end of conversion and digital output signals. It provides examples of interfacing the ADC0808/0809 chip, which uses successive approximation conversion. Interfacing a digital to analog converter is also covered, with an example of interfacing the AD7523 DAC and generating an output sawtooth waveform.