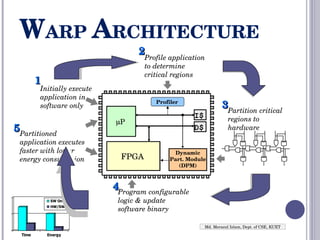

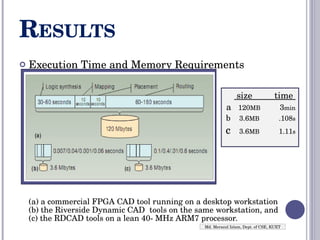

Warp processing is a technique that dynamically optimizes software to improve performance and energy efficiency. It works by profiling an application to identify critical regions, then partitioning those regions to hardware using an FPGA. The binary is updated to execute the partitioned regions on the FPGA circuit while the rest continues in software. This allows applications to achieve speedups of 2-100x or more while using 20x less memory and reducing power consumption by 38-94%.

![S PEEDUP C OMPARISON [a] Comparison of software execution on a digital signal processor (DSP) and warped execution on a warp processor to a 200-MHz ARM9 on single threaded applications. [b] Comparison of multithreaded application speedups on various 400-MHz ARM11-based multiprocessors and warp processors. Md. Merazul Islam, Dept. of CSE, KUET](https://image.slidesharecdn.com/0507036-100124145811-phpapp01/85/0507036-9-320.jpg)