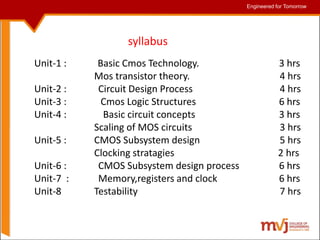

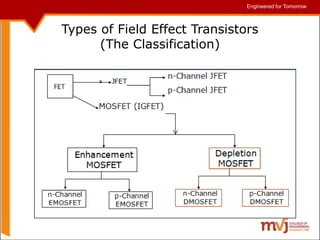

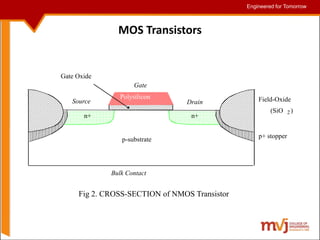

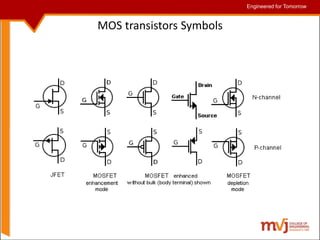

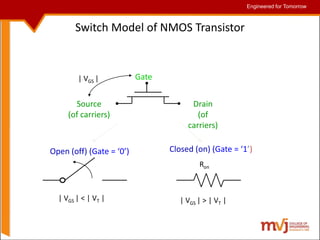

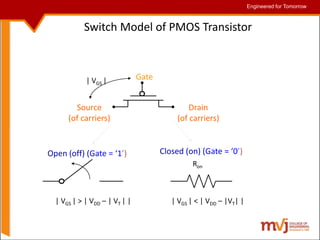

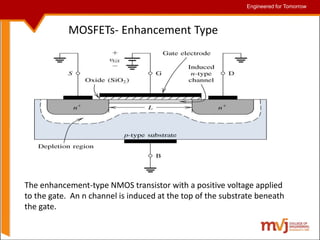

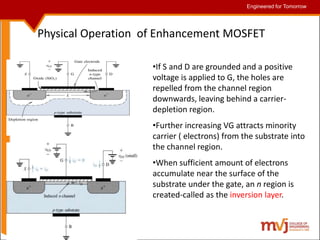

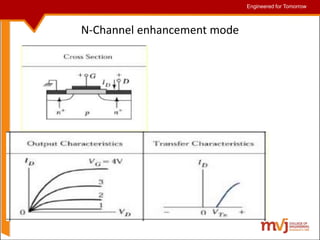

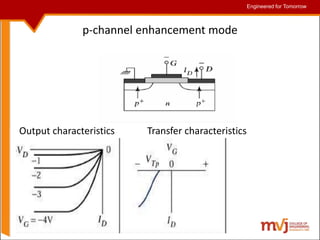

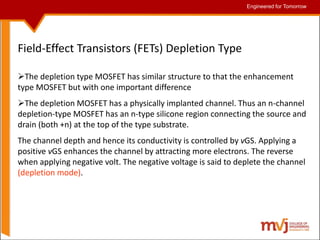

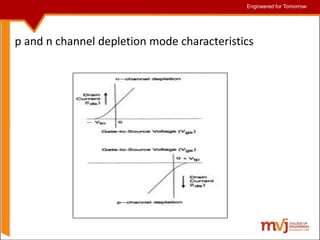

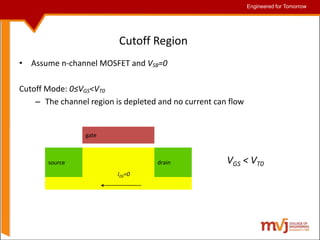

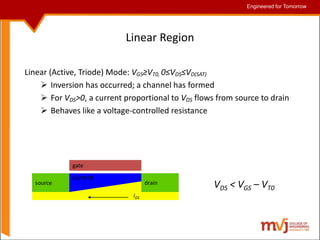

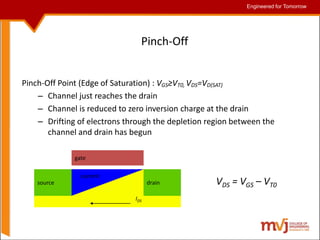

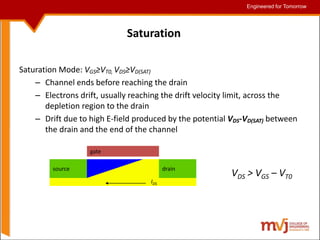

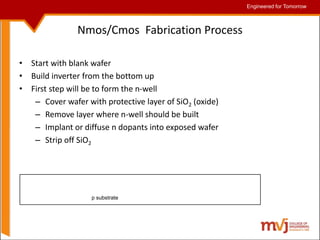

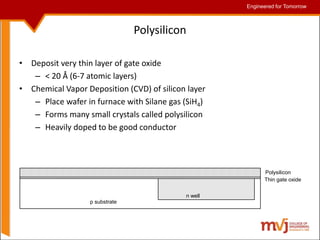

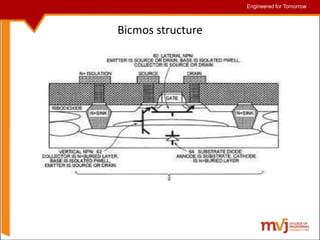

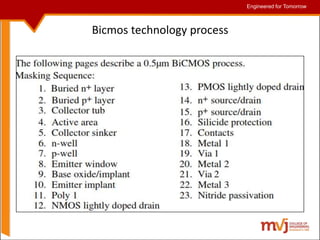

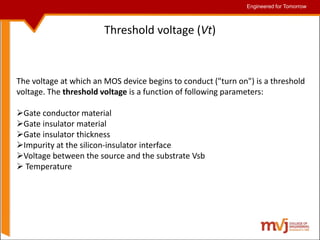

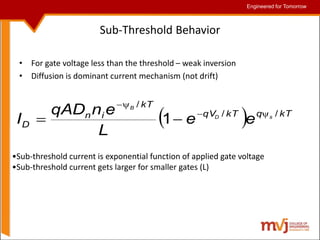

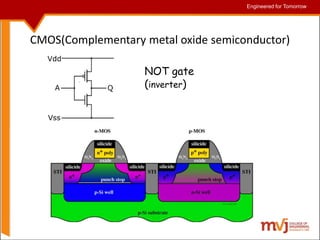

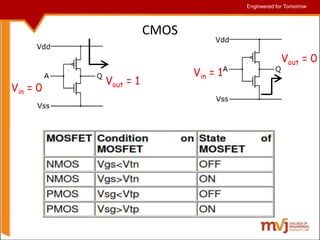

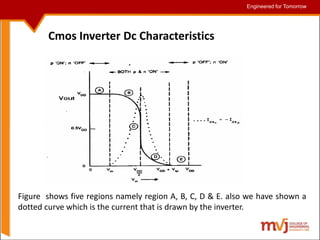

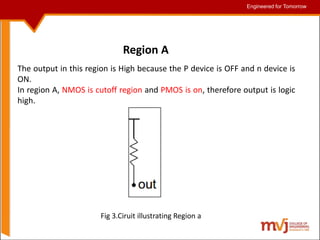

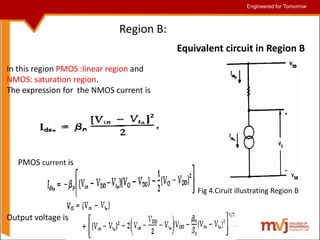

This document outlines the syllabus for a course on Fundamentals of CMOS VLSI. The syllabus covers 8 units over the course of the semester. Unit 1 covers basic CMOS technology and MOS transistor theory. Subsequent units cover circuit design processes, CMOS logic structures, basic circuit concepts, subsystem design, memory, registers, clocking, and testability. The document also provides an introduction to the topic and overview of MOS transistor operation and CMOS fabrication processes.