This document summarizes an FPGA carrier board called the SMT166. It has the following key features:

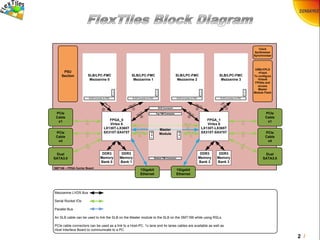

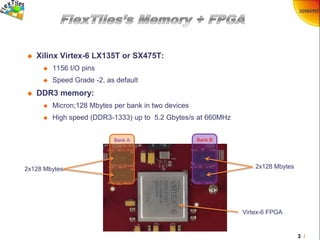

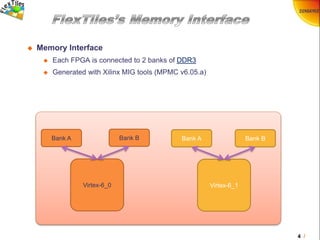

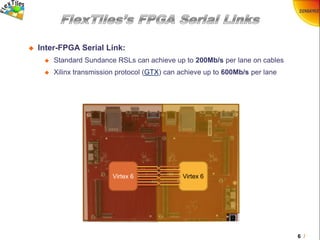

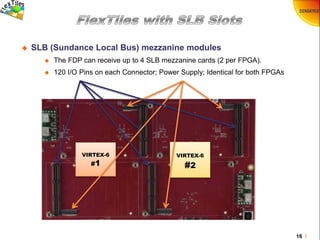

- It contains two Virtex-6 FPGAs and memory banks that can be used for processing and storage.

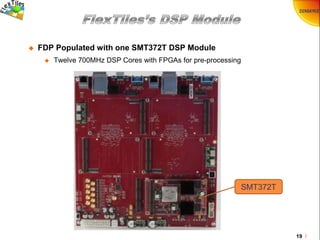

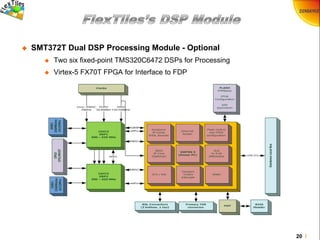

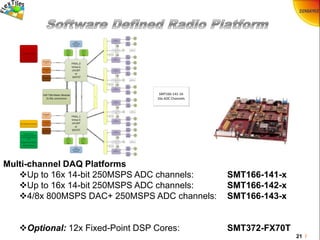

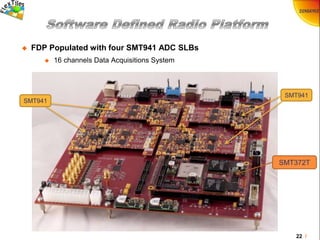

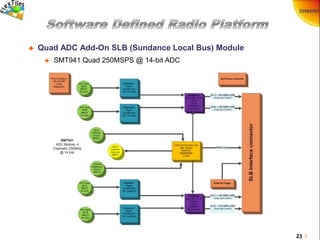

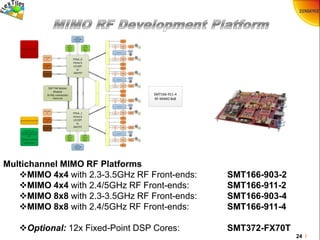

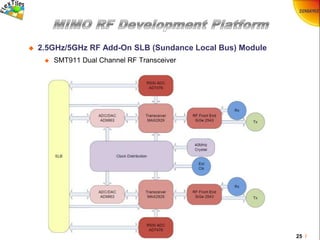

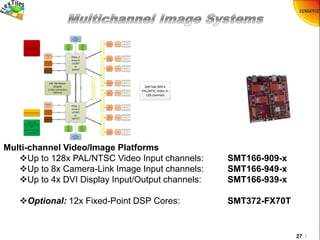

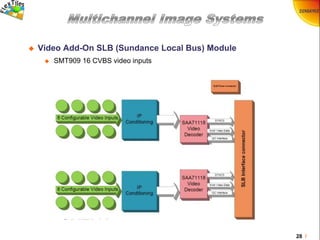

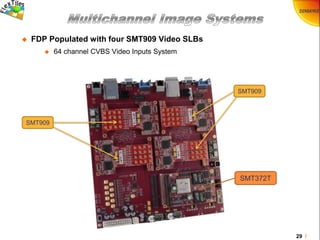

- It supports various mezzanine cards and modules through SLB connectors, including ADC boards and optional DSP modules.

- It provides interfaces such as PCIe, SATA, Ethernet and USB to connect to other devices and systems.