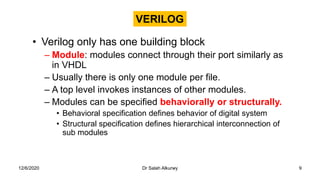

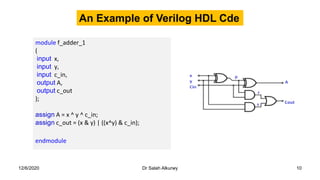

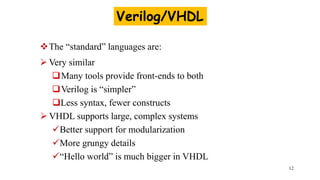

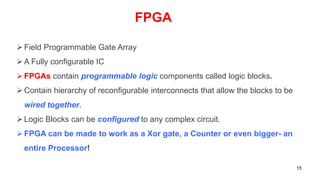

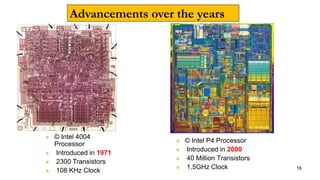

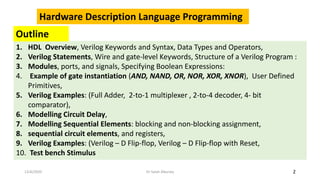

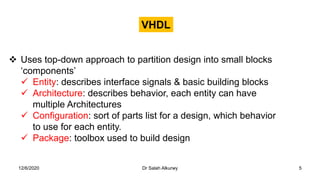

This document provides an outline for a lecture on hardware description language (HDL) programming. It discusses HDL overview and key concepts like Verilog and VHDL. Verilog was developed in the 1980s and became an IEEE standard in 1995. It uses modules as basic building blocks and has a C-like syntax. VHDL was developed for the Department of Defense and also became an IEEE standard. It uses a top-down design approach with entities, architectures, and configurations. Examples of coding in Verilog and uses of FPGAs are also provided.

![Verilog Background

Developed by Gateway Design Automation (1980)

Later acquired by Cadence Design(1989) who made

it public in 1990

Became a standardized in 1995 by IEEE (Std 1364)

regulated by Open Verilog International (OVI)

8

Gateway Design Automation. The company was privately held at that time by Dr. Prabhu

Goel, the inventor of the PO in 1985 DEM (Path-Oriented Decision Making) test generation

algorithm.[1] Verilog HDL was designed by Phil Moorby who was later to become the Chief

Designer for Verilog-XL

12/6/2020 Dr Salah Alkurwy](https://image.slidesharecdn.com/veriloghdl0001-221106180003-f6778d1c/85/Verilog-HDL-0001-pdf-8-320.jpg)