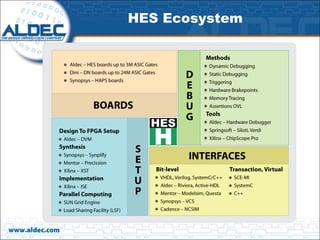

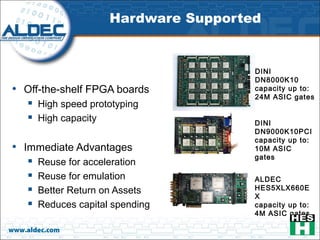

Aldec is a leading EDA company founded in 1984 that provides RTL simulation, verification, and emulation solutions. It has over 200 employees and 30,000 licenses worldwide. Aldec's key products include Active-HDL for simulation, Riviera-PRO for verification, ALINTTM for linting, and HES for emulation. Aldec focuses on continuous innovation to provide better performance, more features, and lower prices than competitors.

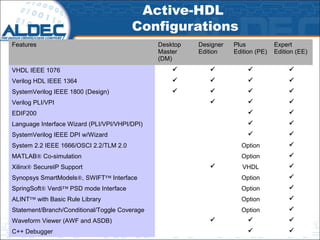

![DVM Configurations

Features Pototyping Acceleration Emulation

(Proto) (Xcell) (Elite)

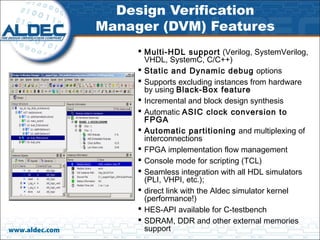

Design Verification Manger [DVM™]

Automatic Design Partitioning w/ LVDS Signal Multiplexing

Blackbox Functionality (Excludes modules)

Static Debugging Probes

Static Debugging Probes w/ Xilinx ChipScope™ Pro

Static Debugging Probes w/ Aldec LA (ALA for SCE-MI)

Dynamic Probes (for SCE-MI)

Clock Conversion and Analysis

Memory Model Mapping (maps to on-board memory)

Prototyping API and function library (interface with C++)

HDL Co-Simulator Interface (Aldec/CDNS/MG/SNPS)

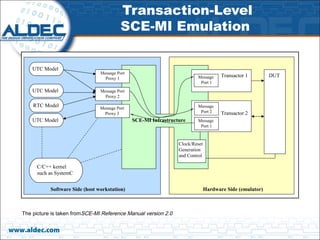

SCE-MI 2.0 HW/SW Infrastructure (SCE-MI C++ API)

C/C++/SC Testbench Wrapper

OVL Assertions Support

Vector Based Emulation

Multi-FPGA Boards Support Option Option

www.aldec.com](https://image.slidesharecdn.com/aldecoverview2011-10revised-130130233113-phpapp02/85/Aldec-overview-2011-10-revised-30-320.jpg)