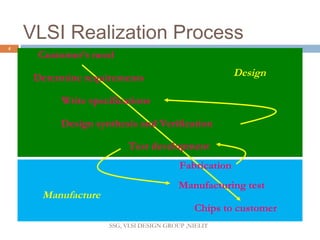

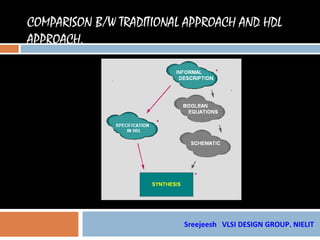

Hardware description languages (HDLs) like VHDL and Verilog allow designers to model digital circuits and systems. HDLs enable increased productivity through design reuse, faster design changes, and exploration of alternative architectures. VHDL is a popular, industry standard HDL that supports modeling designs hierarchically at different levels of abstraction from behavioral to structural. VHDL models can be simulated and synthesized, facilitating early verification of a design's functionality before implementation.