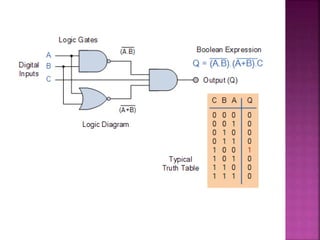

This document discusses hardware description languages used in electronics design. It describes how HDLs like VHDL and Verilog are used to program digital and mixed-signal circuits. Simulation allows validation of the design against specifications. The document also discusses formal verification using property specification languages and different modeling styles for Verilog like gate-level, dataflow, and behavioral modeling.