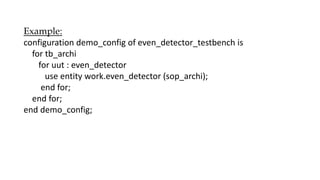

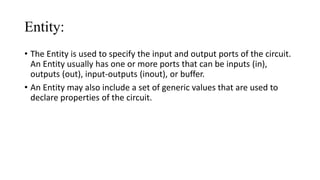

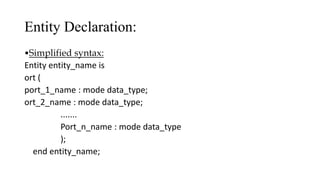

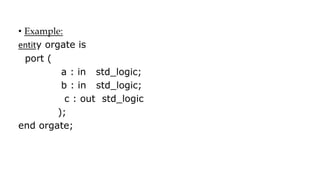

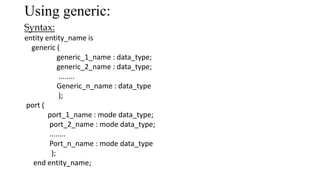

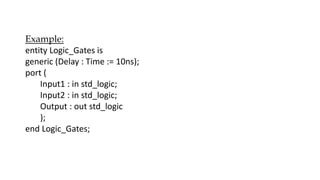

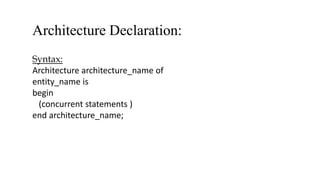

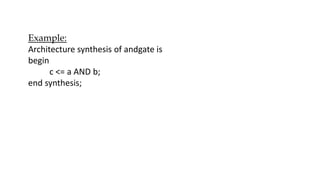

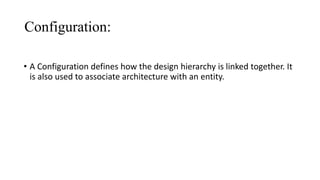

This document discusses the Hardware Description Language (HDL) VHDL. It provides an overview of VHDL, including that it is used to describe and simulate digital circuits, and is an IEEE standard. The key elements of VHDL are then described - entities define input/output ports, architectures describe how the circuit operates, and configurations define how designs are linked together. Examples of each element are provided. Finally, it briefly discusses VHDL modeling styles and objects like constants, variables, and signals.

![Configuration Declaration:

Syntax:

configuration configuration_name of entity_name is

--configuration declarations

for architecture_name

for instance_label : component_name

use entity library_name.entity_name(architecture_name);

end for;

--

end for;

end [configuration] [configuration_name];](https://image.slidesharecdn.com/presentation1-231217131804-ed7822cc/85/Digital-principle-and-computer-design-Presentation-1-pptx-16-320.jpg)