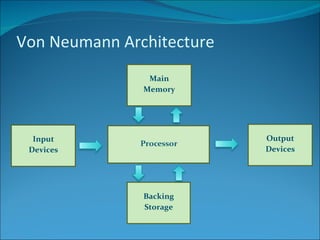

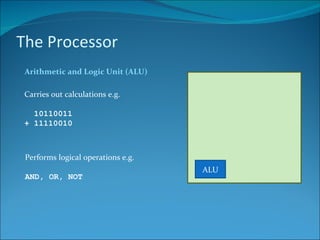

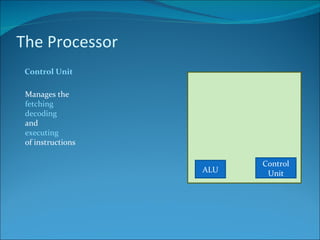

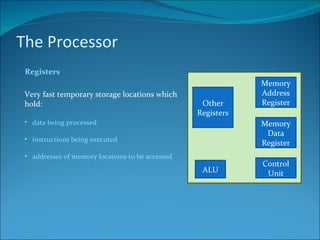

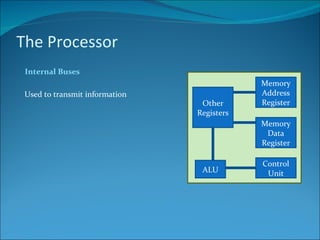

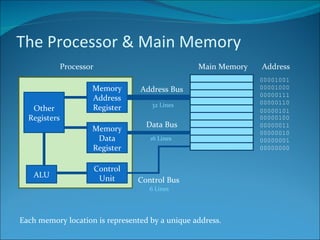

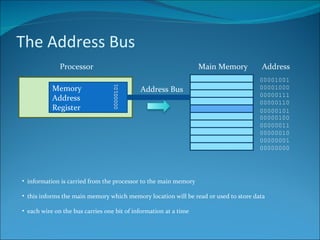

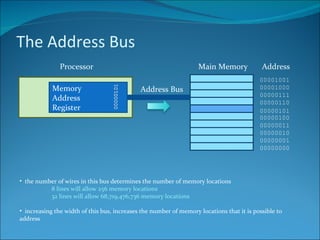

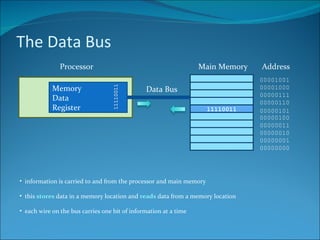

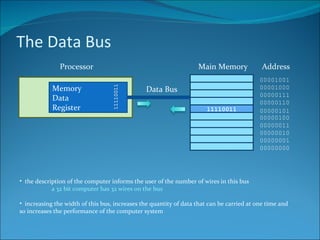

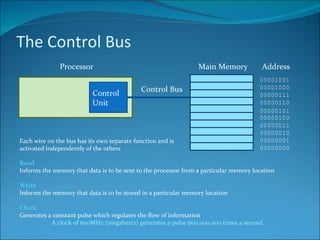

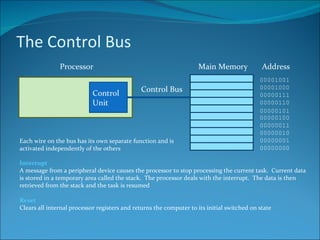

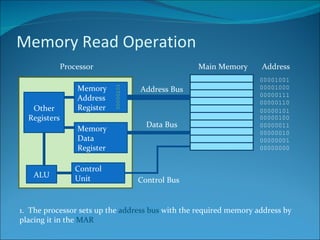

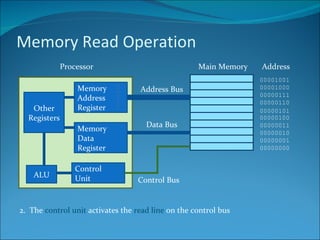

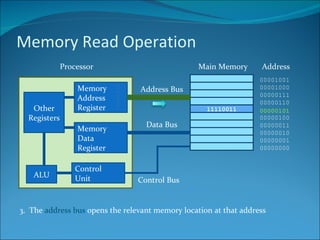

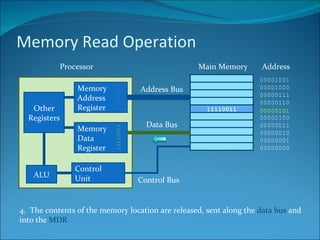

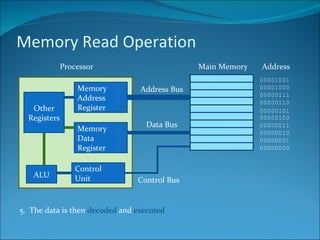

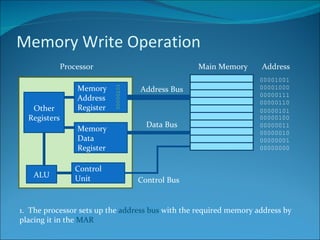

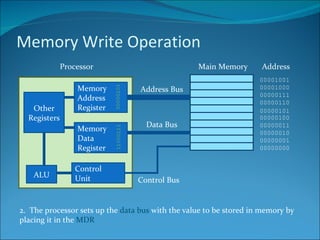

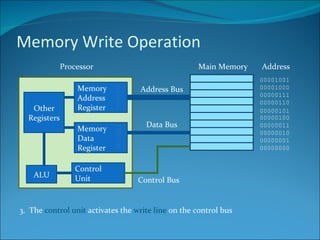

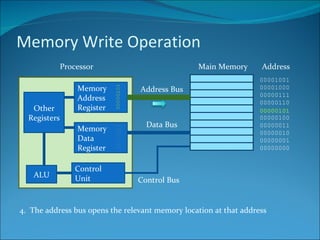

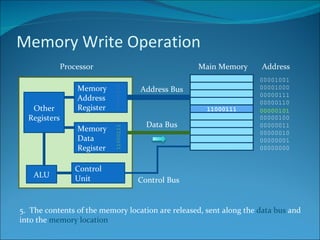

The document describes the basic components and functioning of the Von Neumann architecture. It explains that the processor contains an arithmetic logic unit (ALU) and control unit which fetch and execute instructions from main memory via buses. It then outlines the memory read and write operations, where the address bus accesses the desired location and the data bus transfers data between processor and memory.