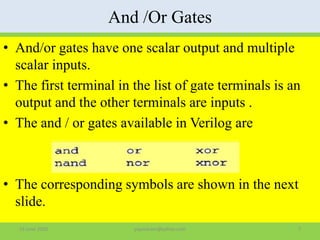

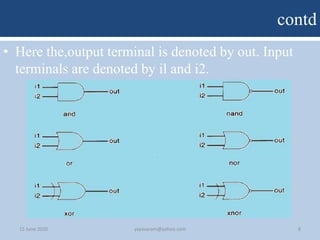

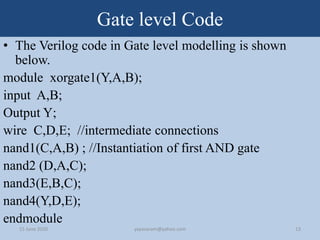

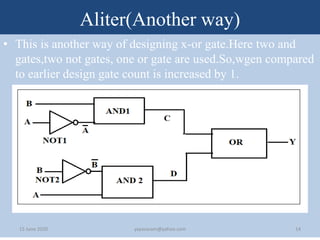

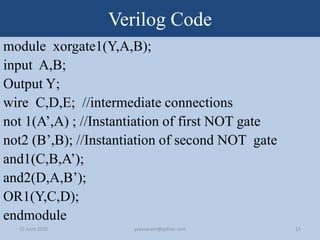

- Gate level modeling in Verilog uses basic logic gates like AND, OR, NOT etc. as modules to represent digital circuits.

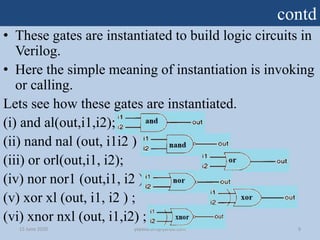

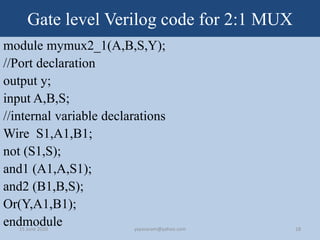

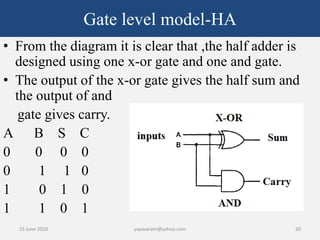

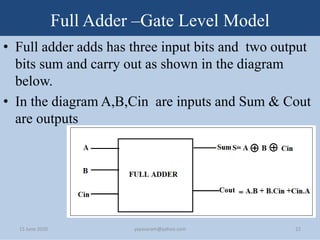

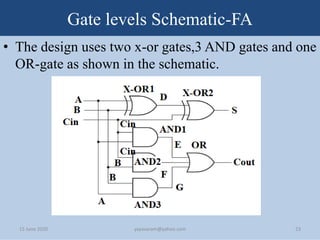

- Common digital components like multiplexers, half adders, full adders can be designed using gate level modeling by connecting the basic gates.

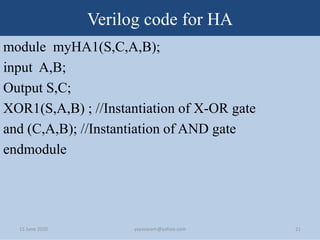

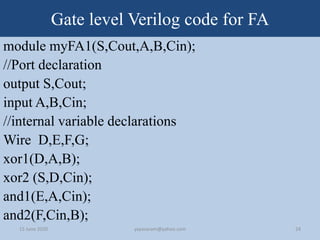

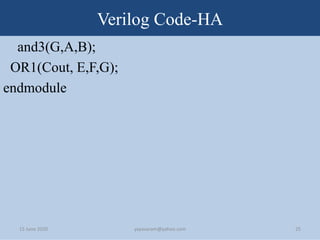

- The document provides examples of gate level Verilog code for a 2:1 multiplexer, half adder, and full adder by instantiating AND, OR, XOR and NOT gates.