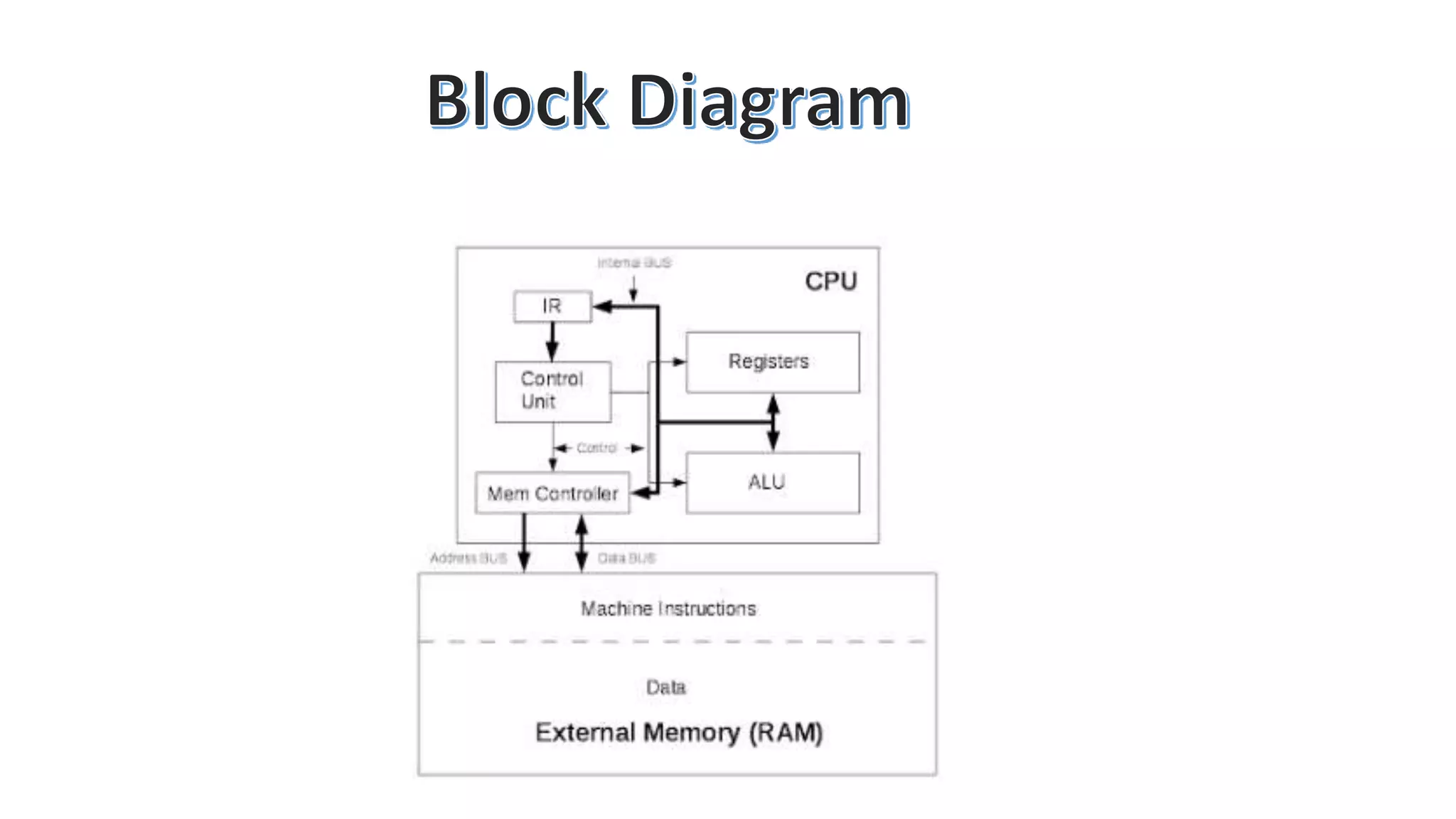

This document summarizes a presentation about single accumulator based CPU organization. It discusses that early computers used this organization where the accumulator register is used implicitly for all instructions and stores results. It notes the main points are the accumulator always stores the first ALU operand and the second comes from registers or memory. Instructions are one address and the CPU is a one address machine. It provides examples of load, store, and ALU operations. Finally, it discusses advantages of short instructions and faster cycles but disadvantages of increased program size and execution time for complex expressions.

![ALUoperation –

>In this type of operation, arithmetic operations are performed on

the data.

For ex: MULT X

>where X is the address of the operand. The MULT instruction in

this example performs the operation,

AC <-- AC * M[X]](https://image.slidesharecdn.com/singleaccumulatorbasedcpu-230524095354-fcdb41c3/75/Single-accumulator-based-CPU-pptx-7-2048.jpg)

![>AC is the Accumulator and M[X] is the memory word located at

location X.

>This type of CPU organization is first used in PDP-8

processor and is used for process control and laboratory

applications.

>It has been totally replaced by the introduction of the new

general register based CPU.](https://image.slidesharecdn.com/singleaccumulatorbasedcpu-230524095354-fcdb41c3/75/Single-accumulator-based-CPU-pptx-8-2048.jpg)