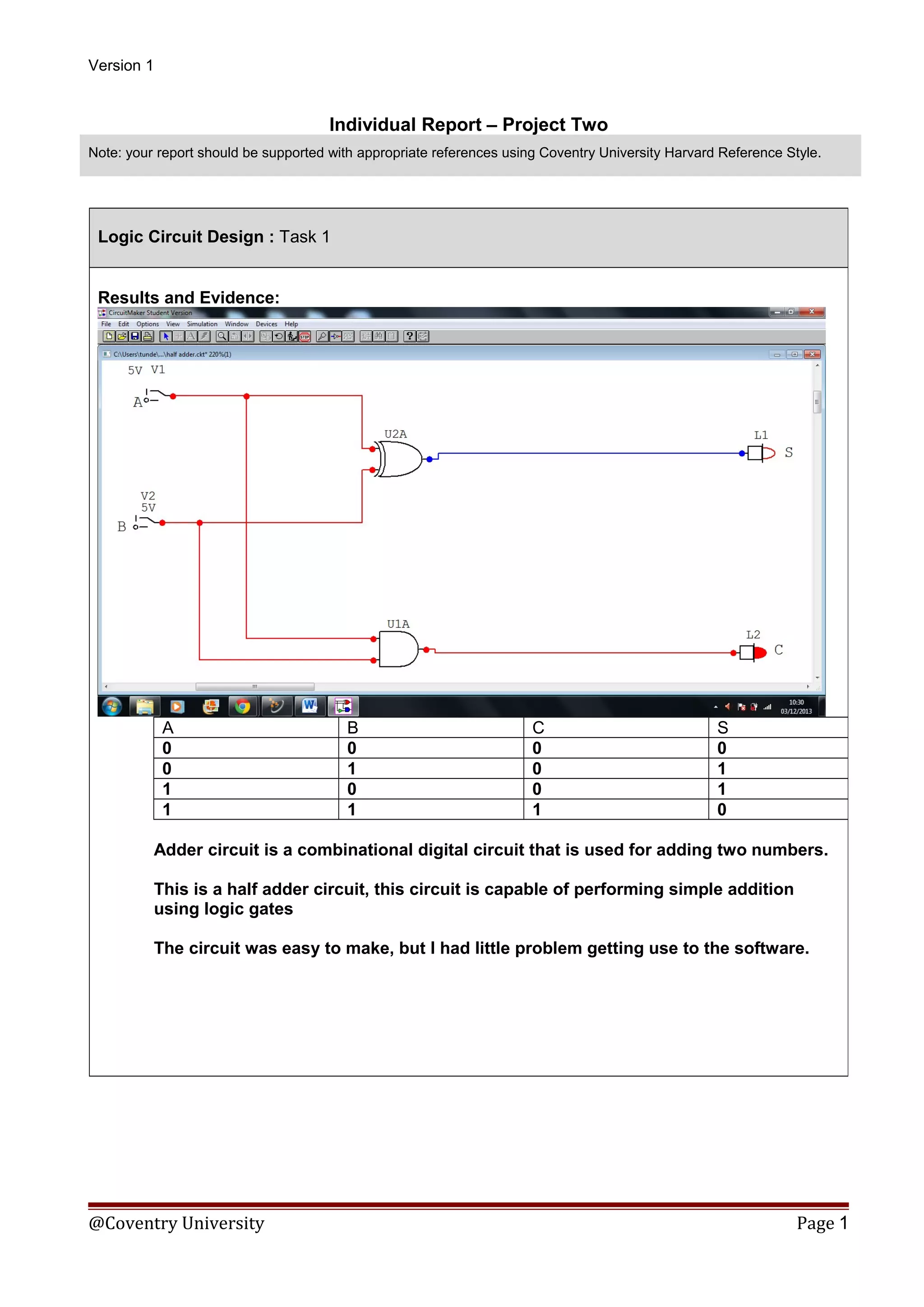

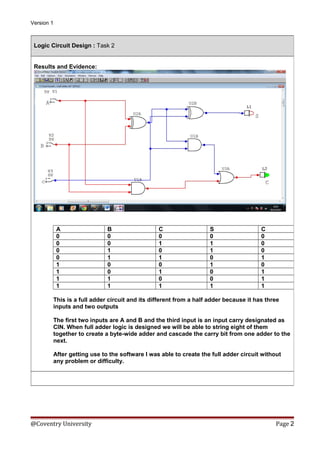

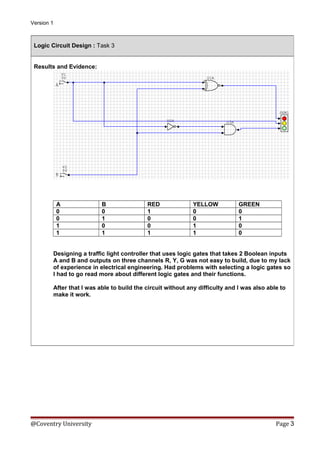

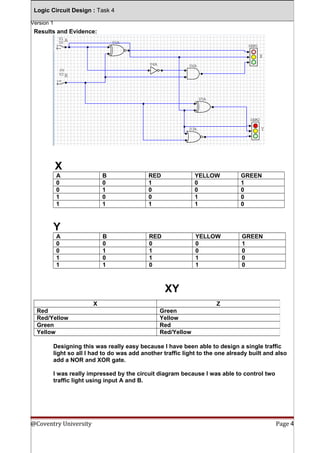

This document discusses the results of 5 tasks related to logic circuit design. Task 1 describes a half adder circuit that performs simple addition using logic gates. Task 2 details a full adder circuit that has three inputs and two outputs. Task 3 discusses designing a traffic light controller circuit using logic gates. Task 4 explains controlling two traffic lights using additional logic gates. Task 5 compares CISC and RISC processor designs, noting CISC uses complex instructions while RISC focuses on simplicity and speed.