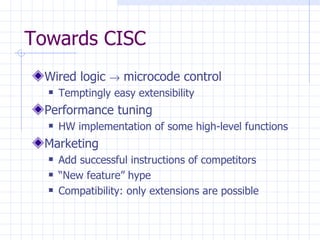

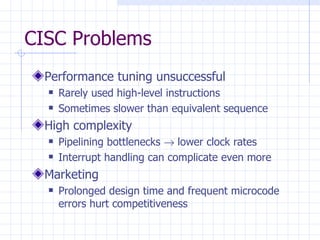

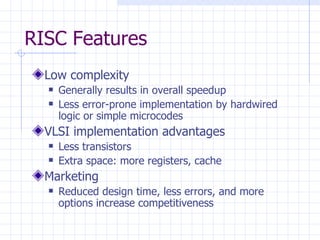

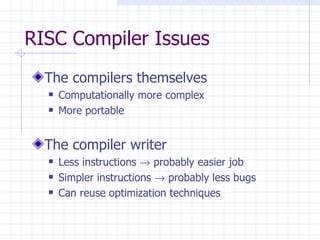

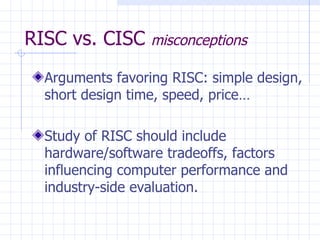

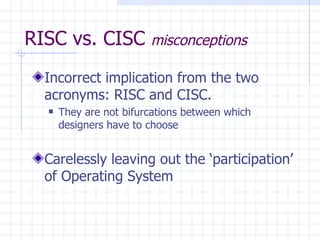

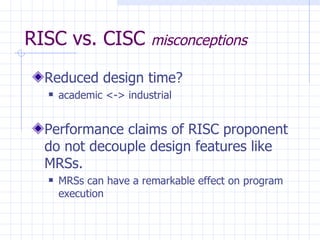

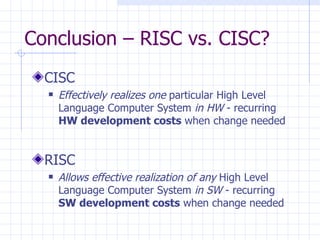

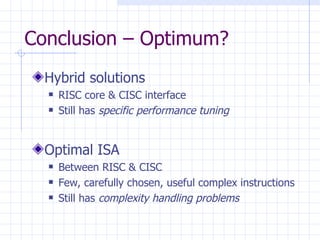

The document discusses the differences between RISC and CISC architectures. RISC architectures have lower complexity through hardwired logic and simpler instruction sets, which can result in higher performance. However, CISC architectures have more extensive instruction sets which allow hardware implementation of high-level functions. The trade-offs between hardware and software complexity must be considered, as well as industry factors, in evaluating RISC vs CISC. An optimal solution may be a hybrid architecture with a RISC core and CISC-like instructions.