The document provides an overview of the course content for Digital Electronics Circuits. It is divided into three modules:

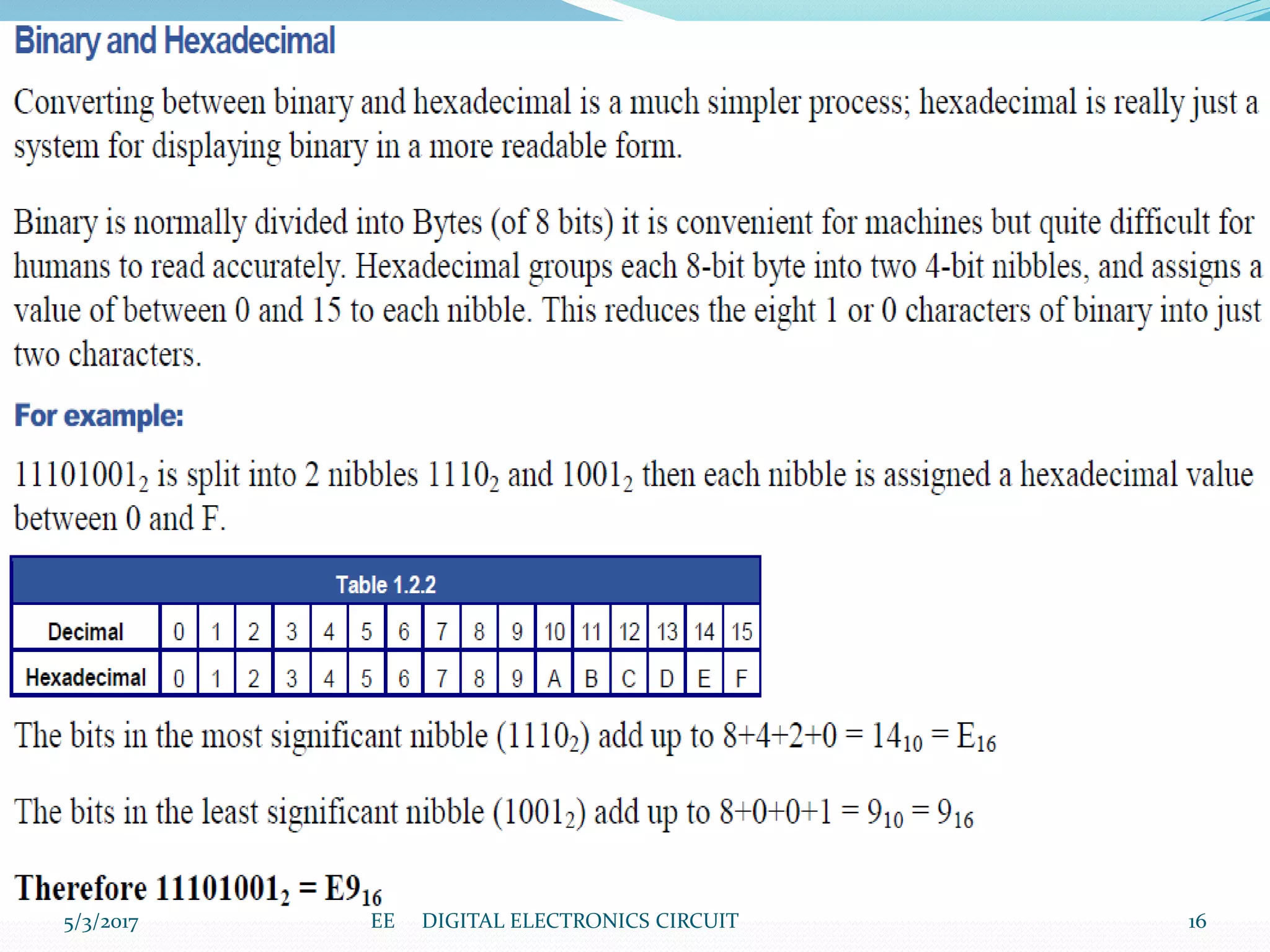

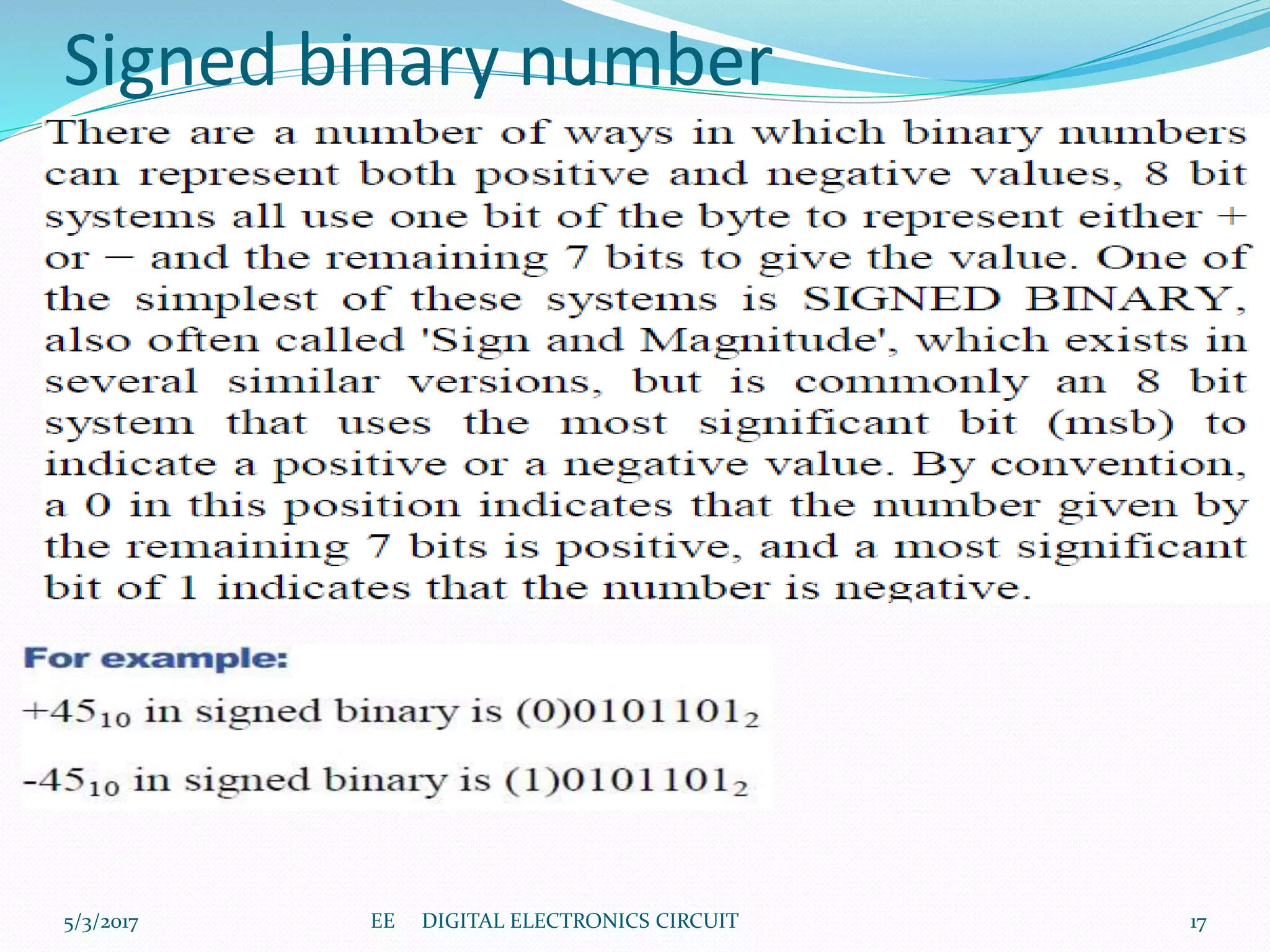

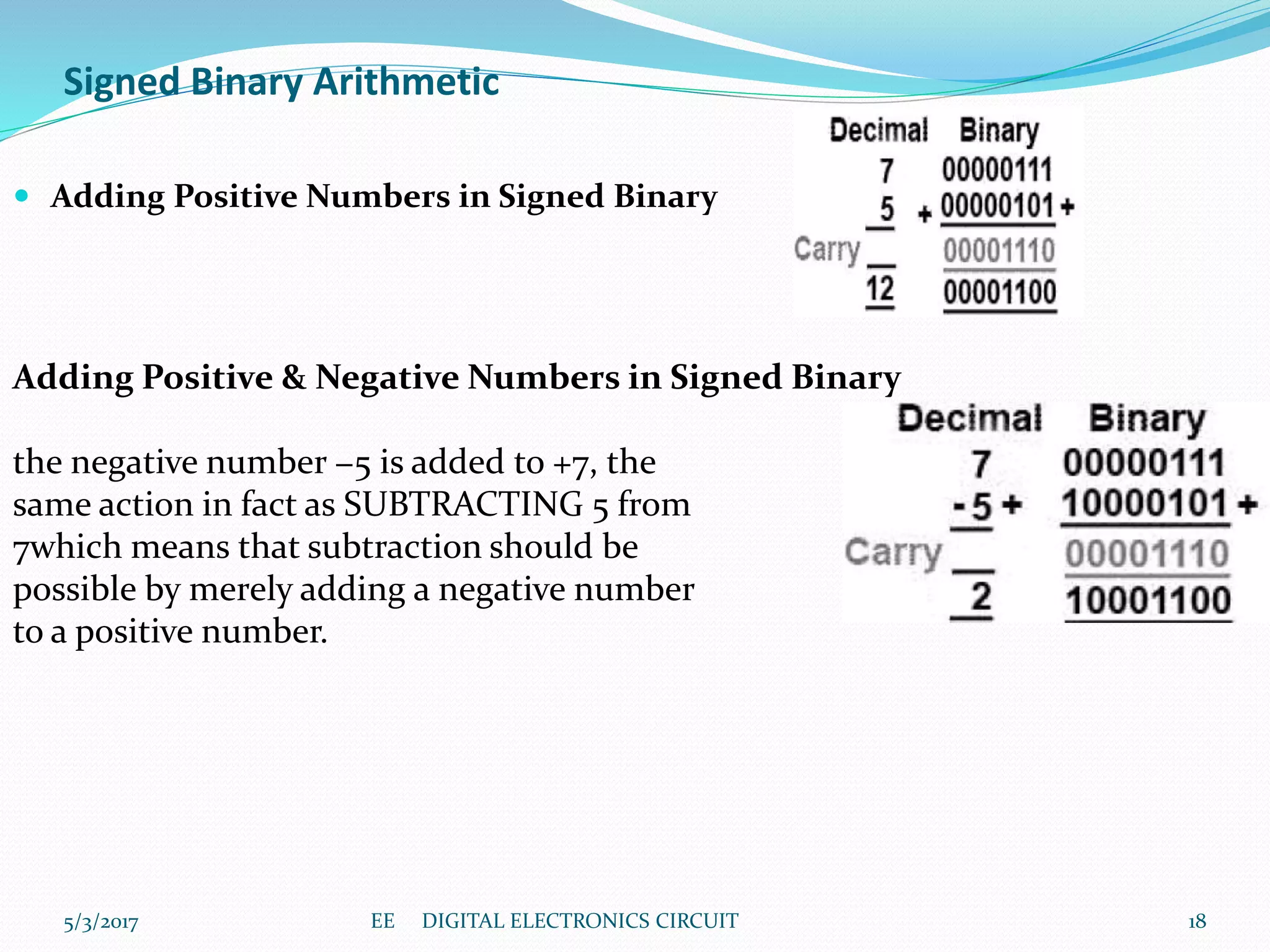

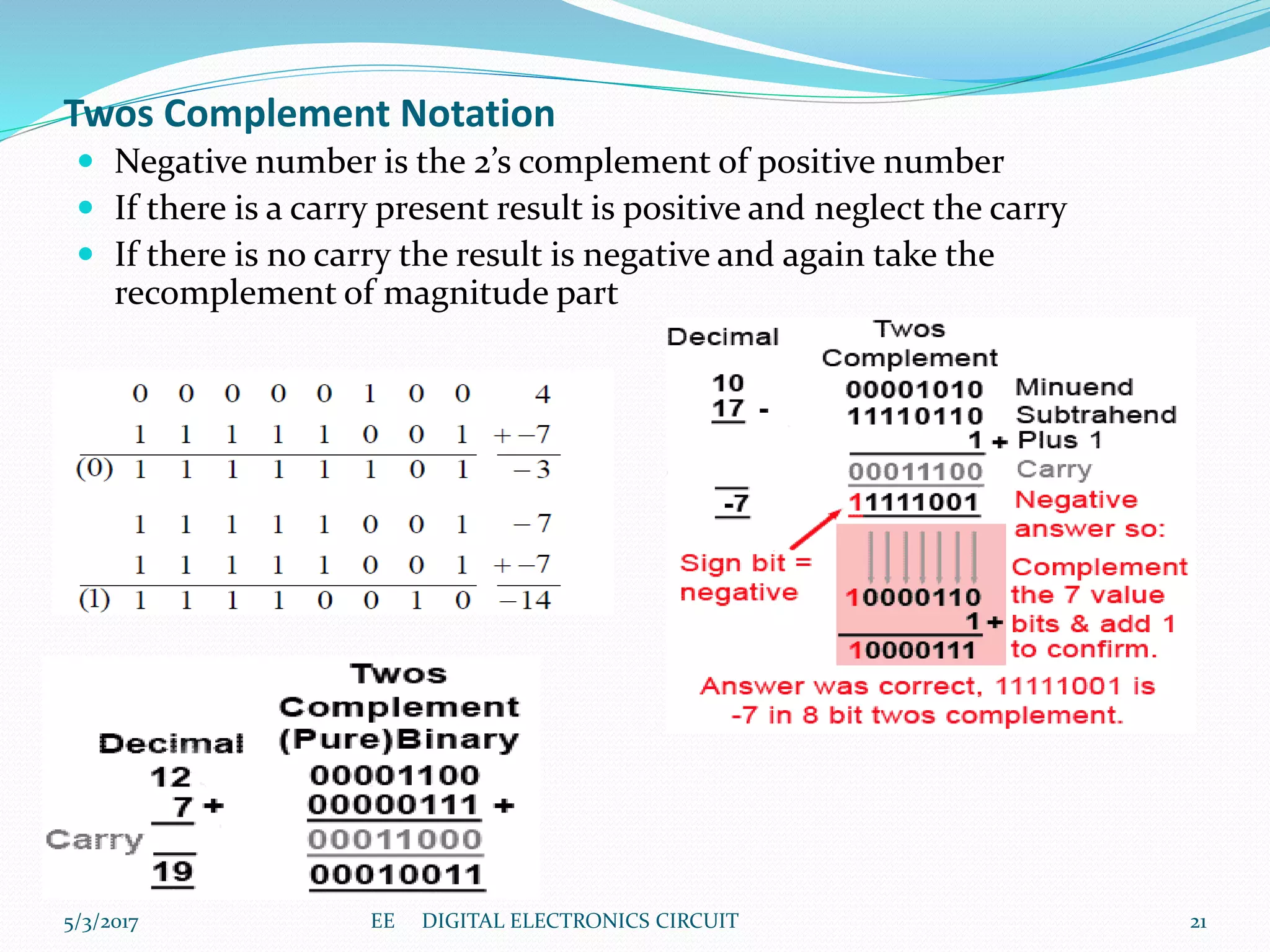

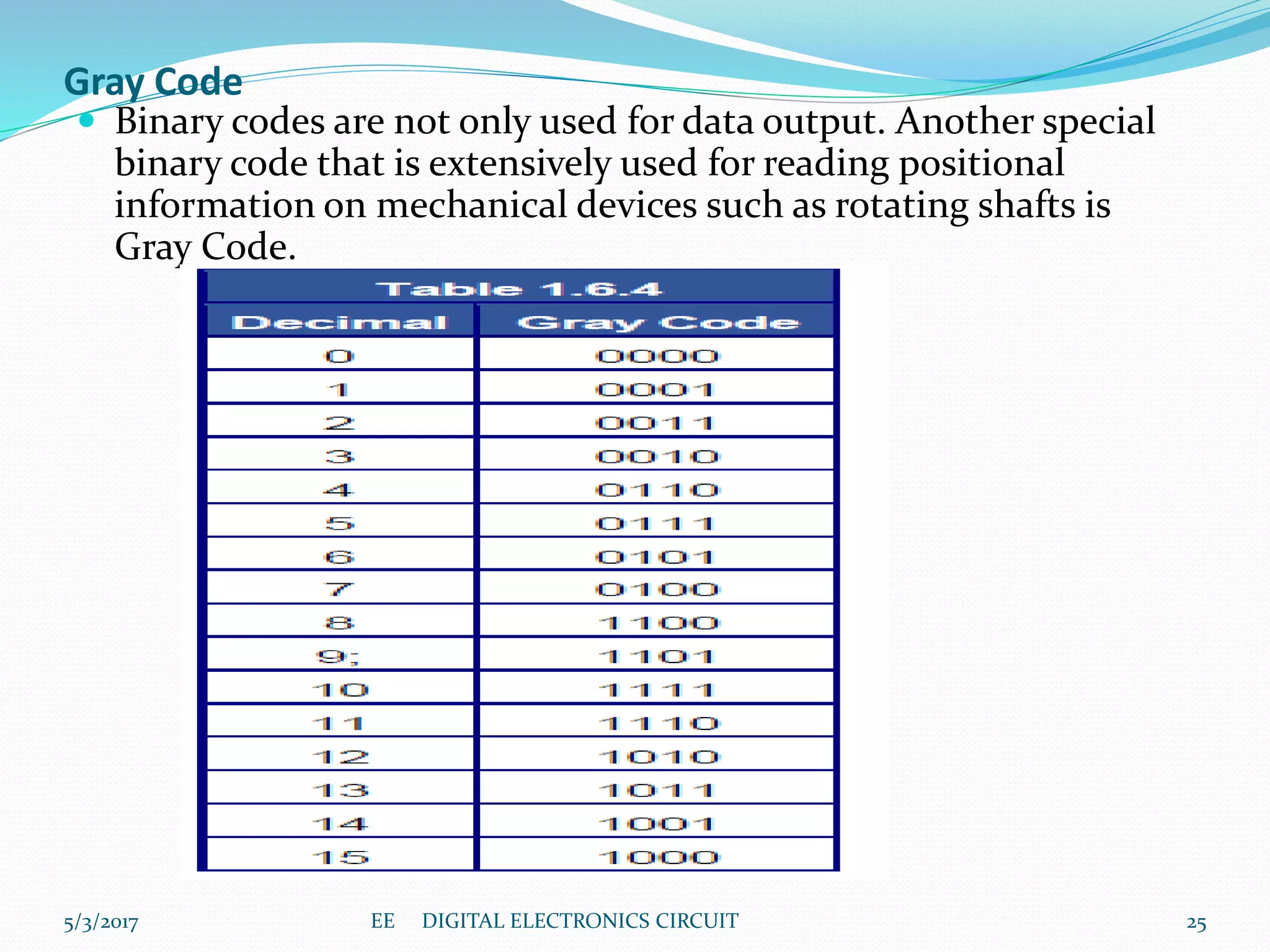

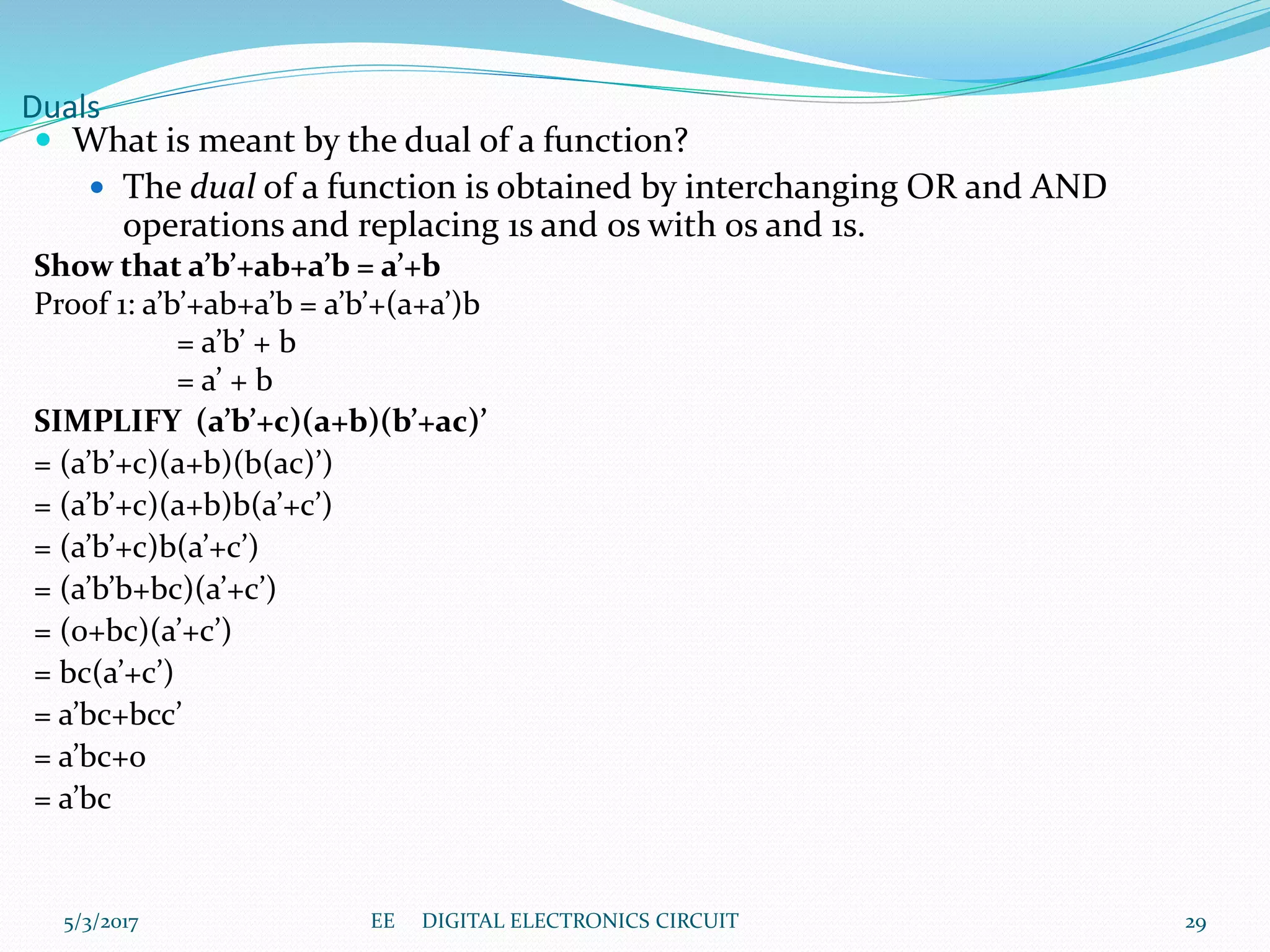

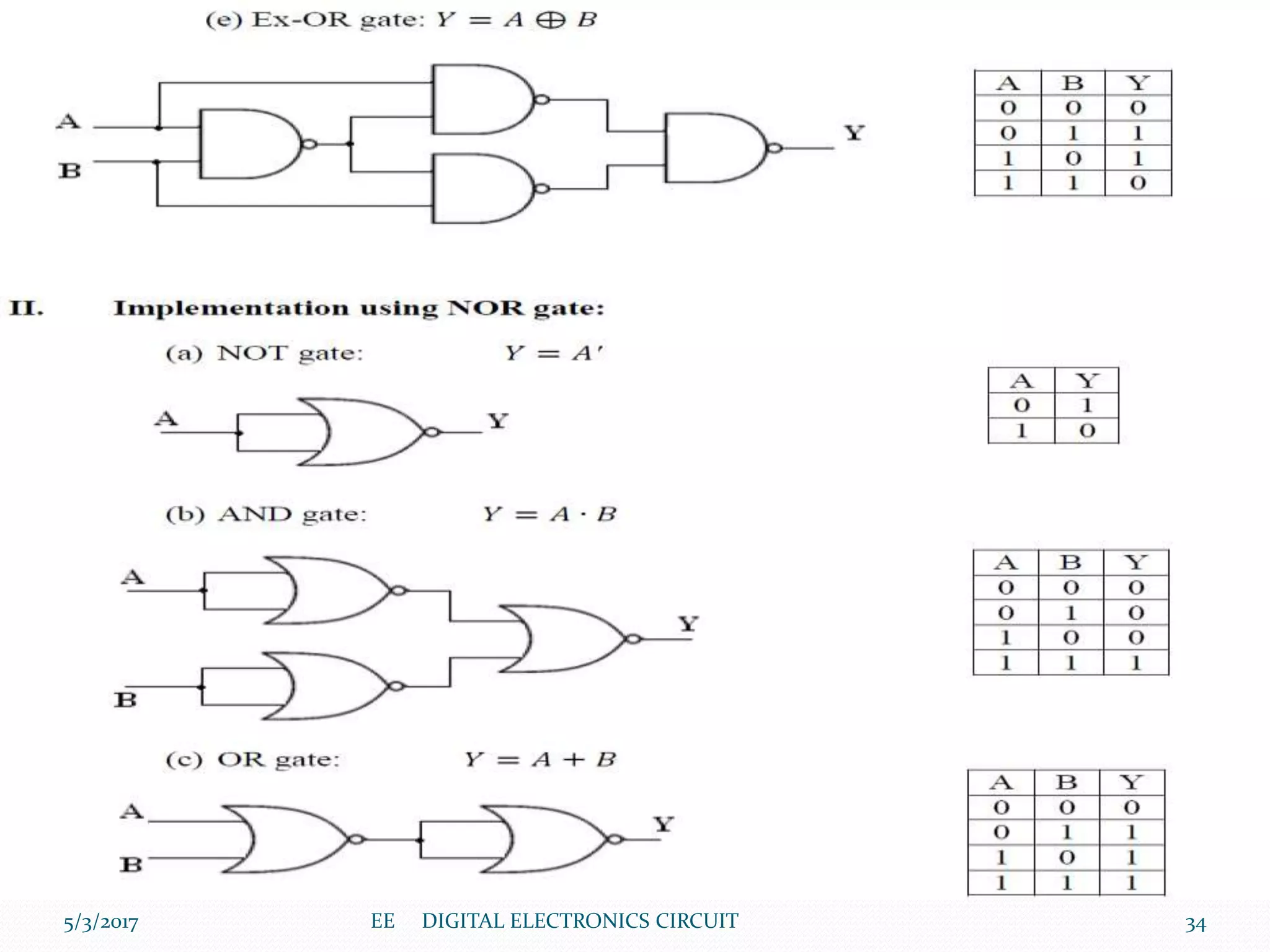

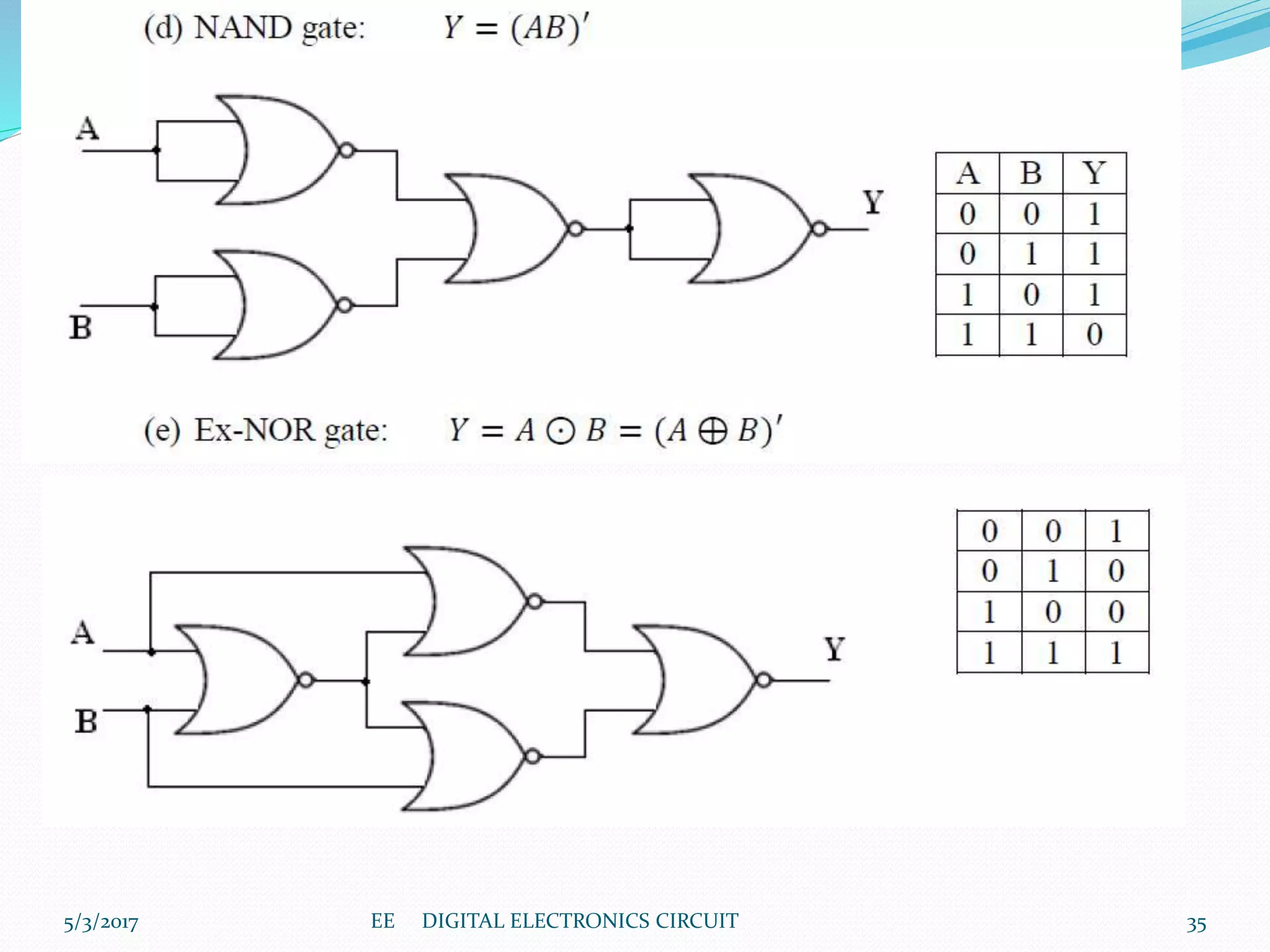

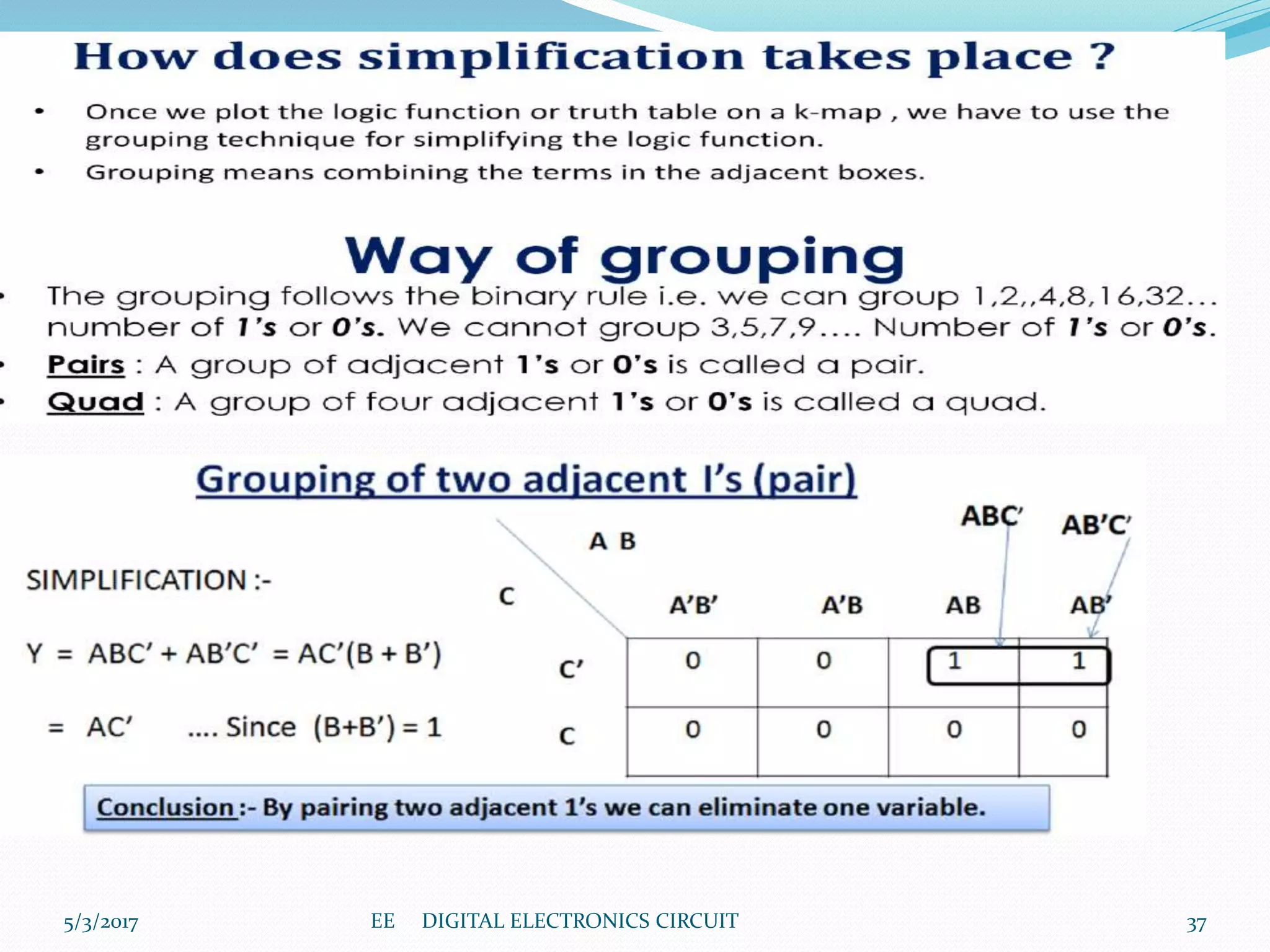

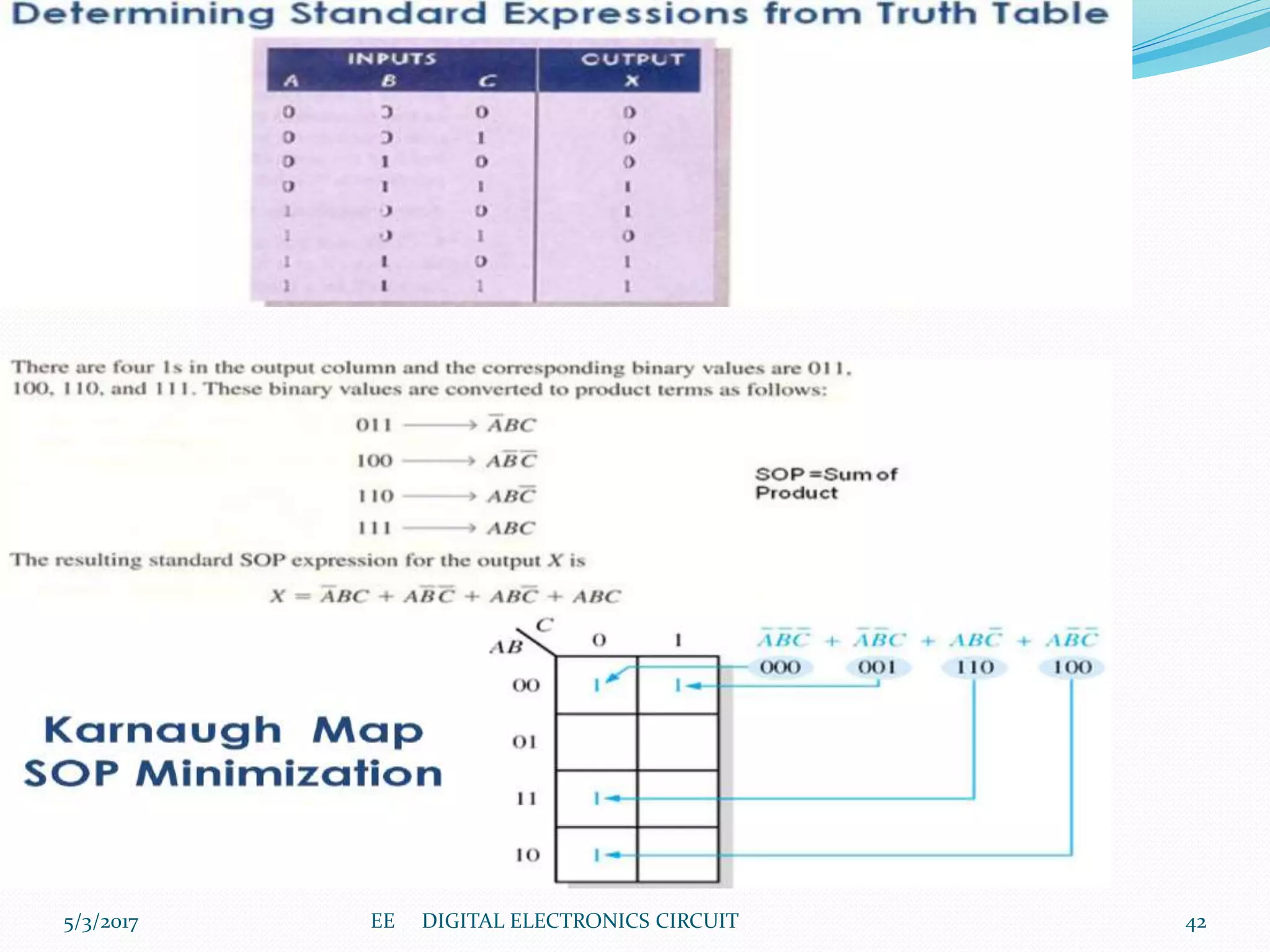

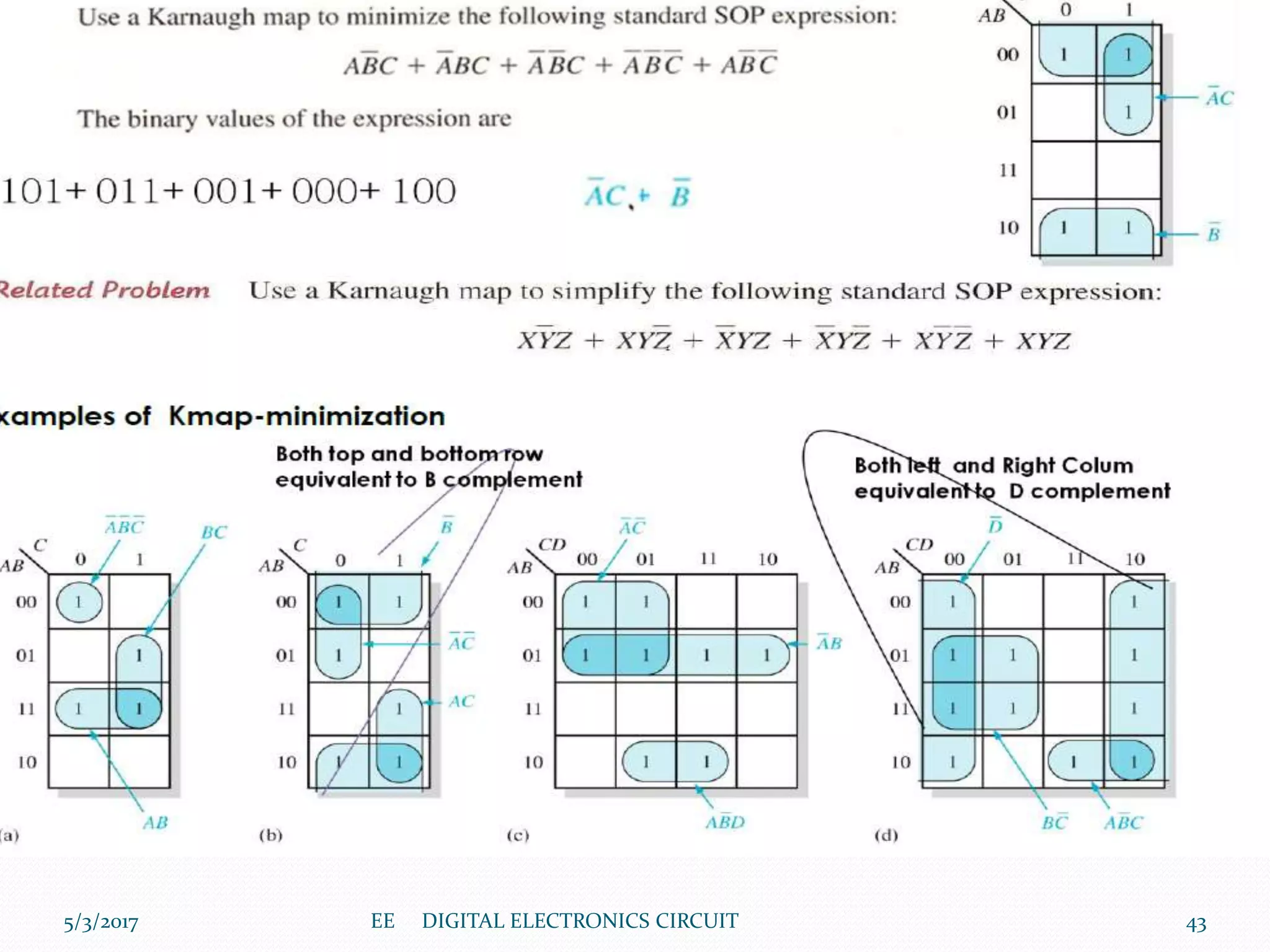

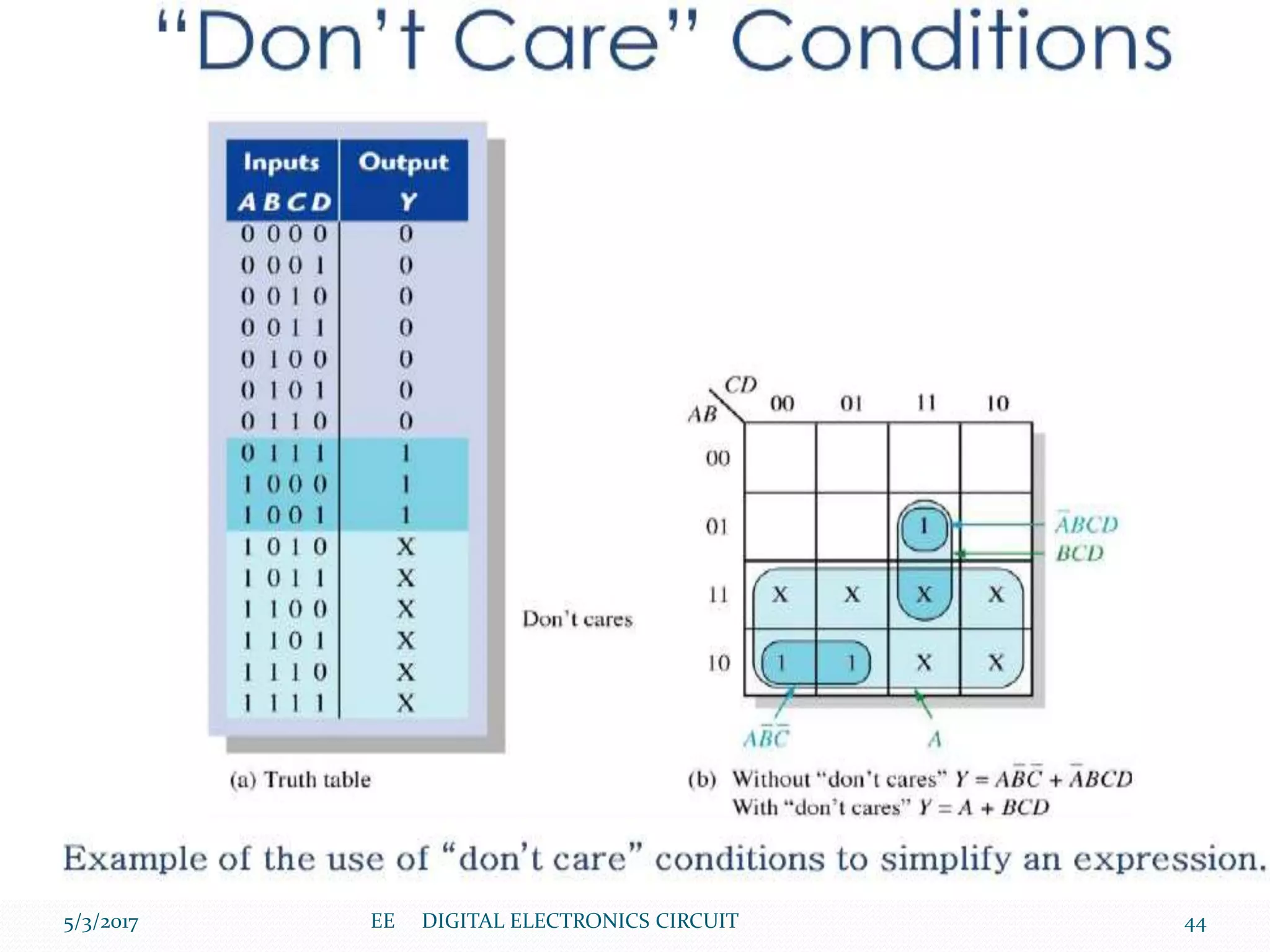

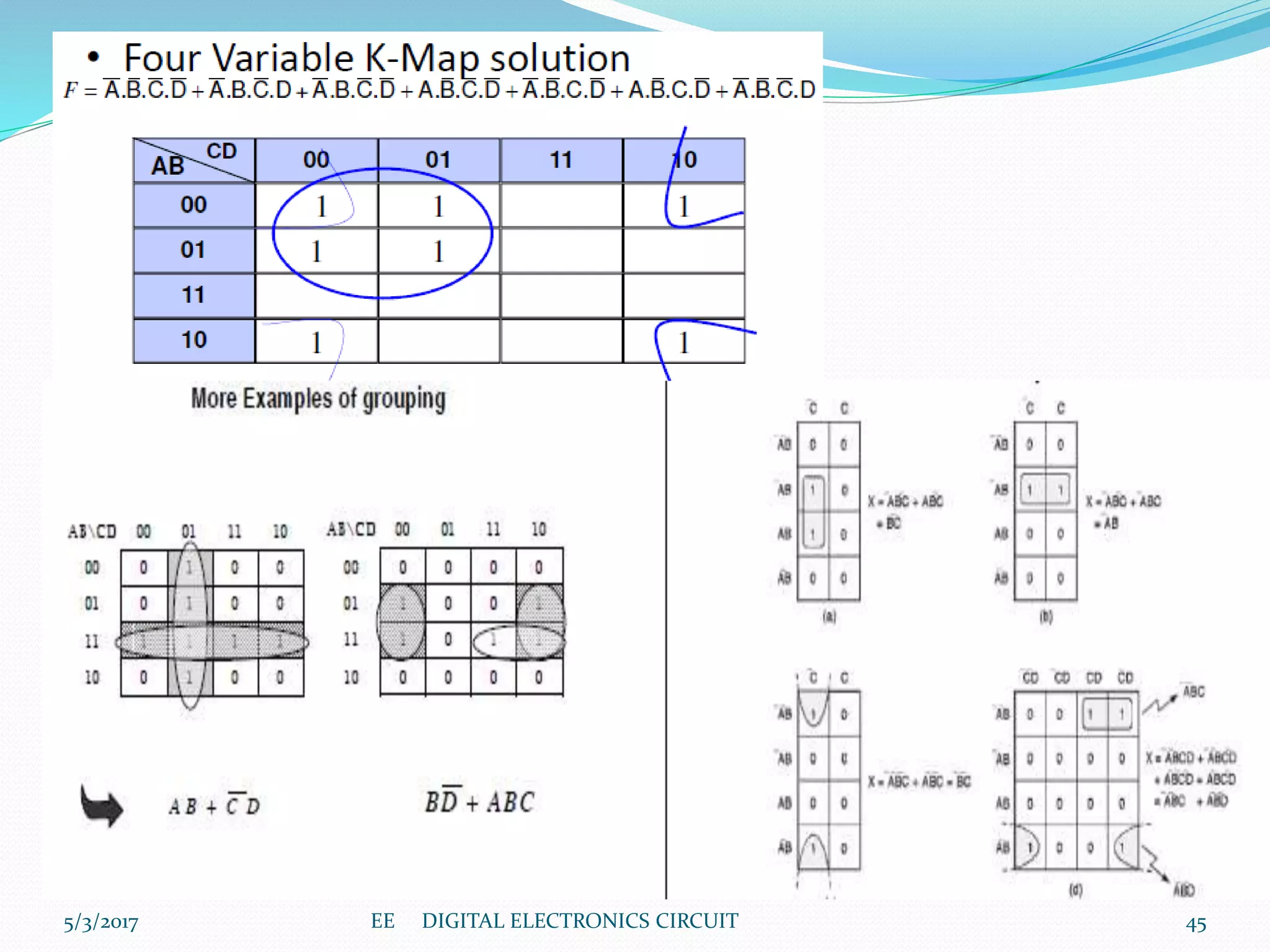

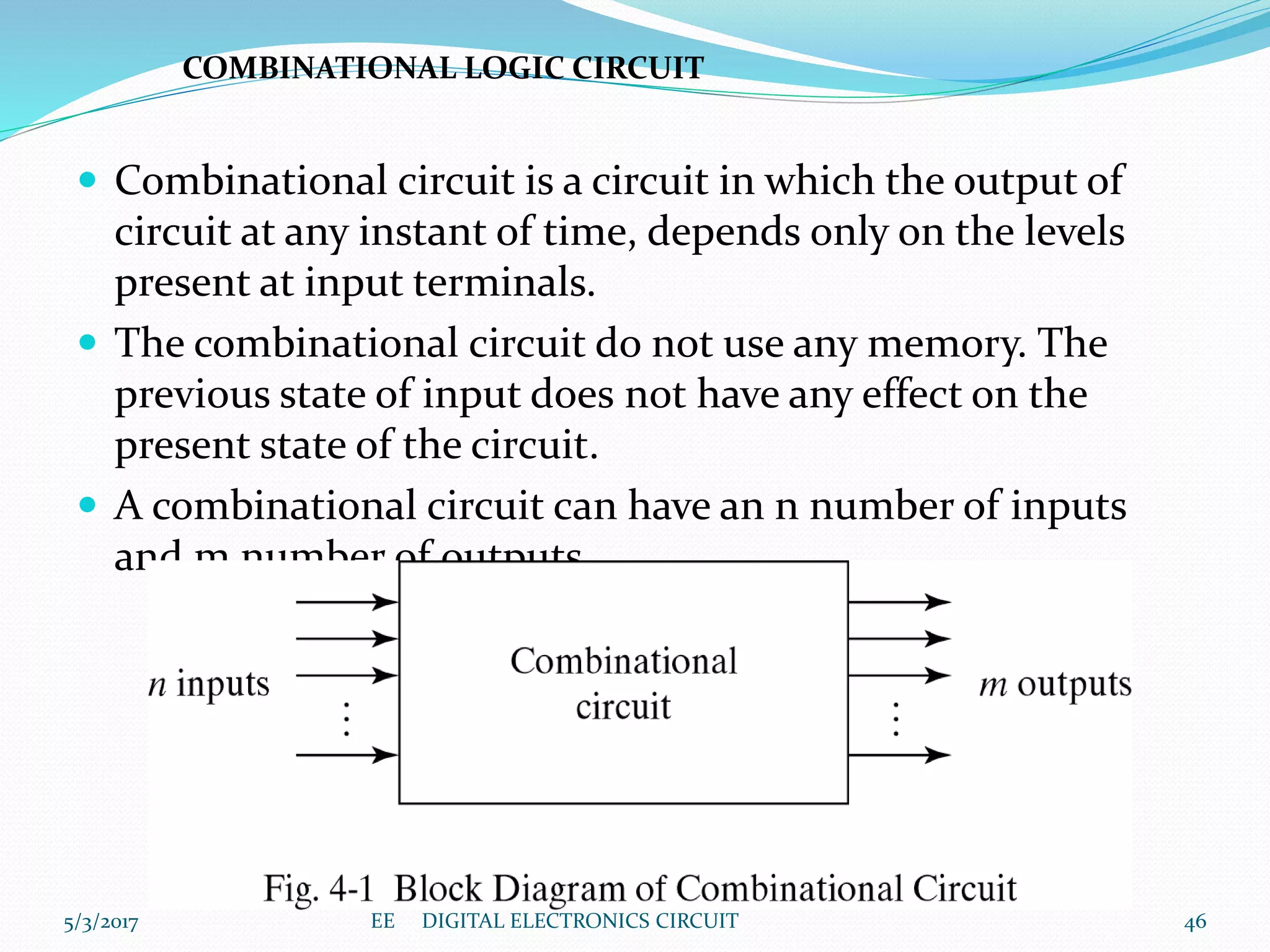

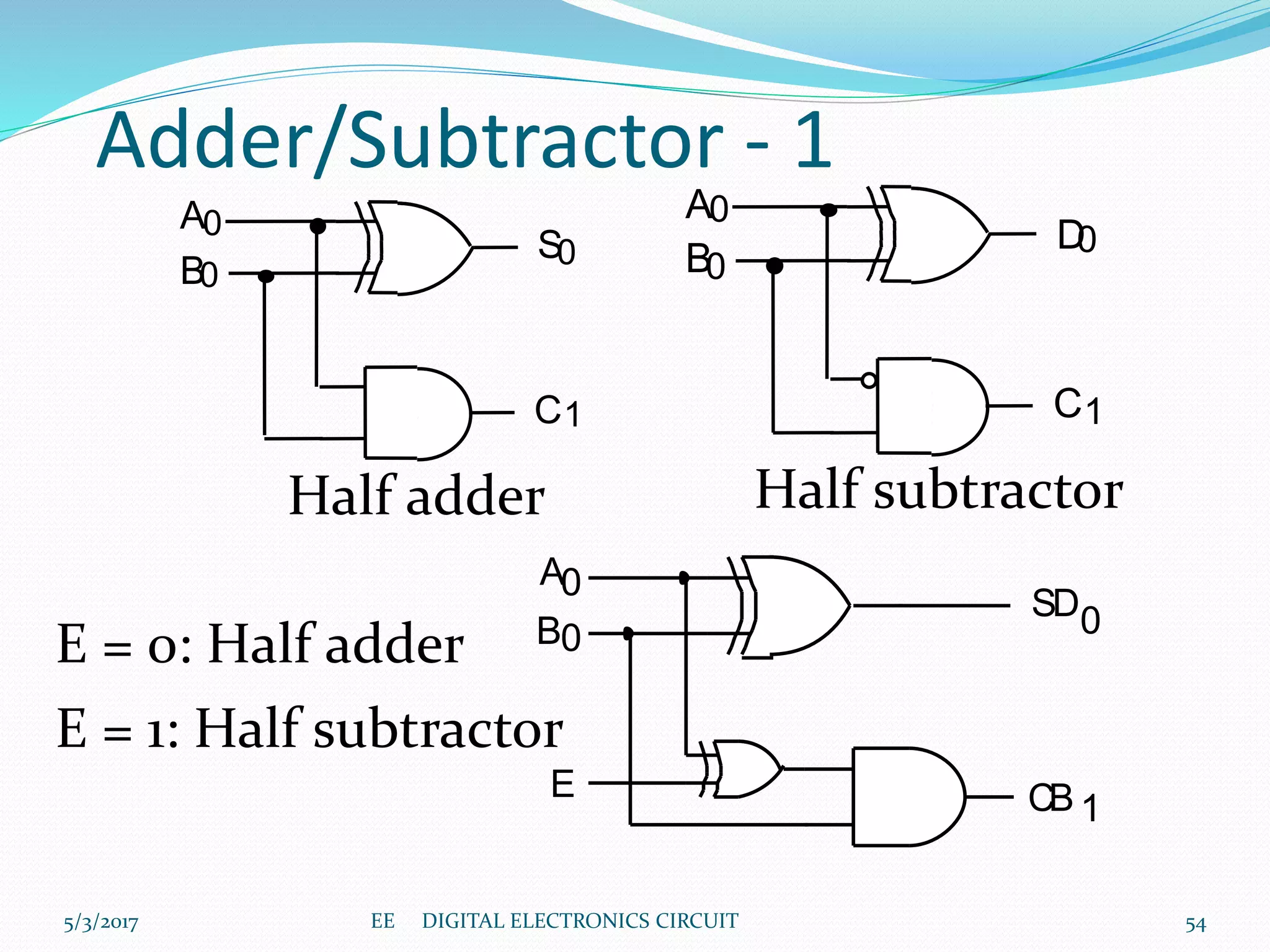

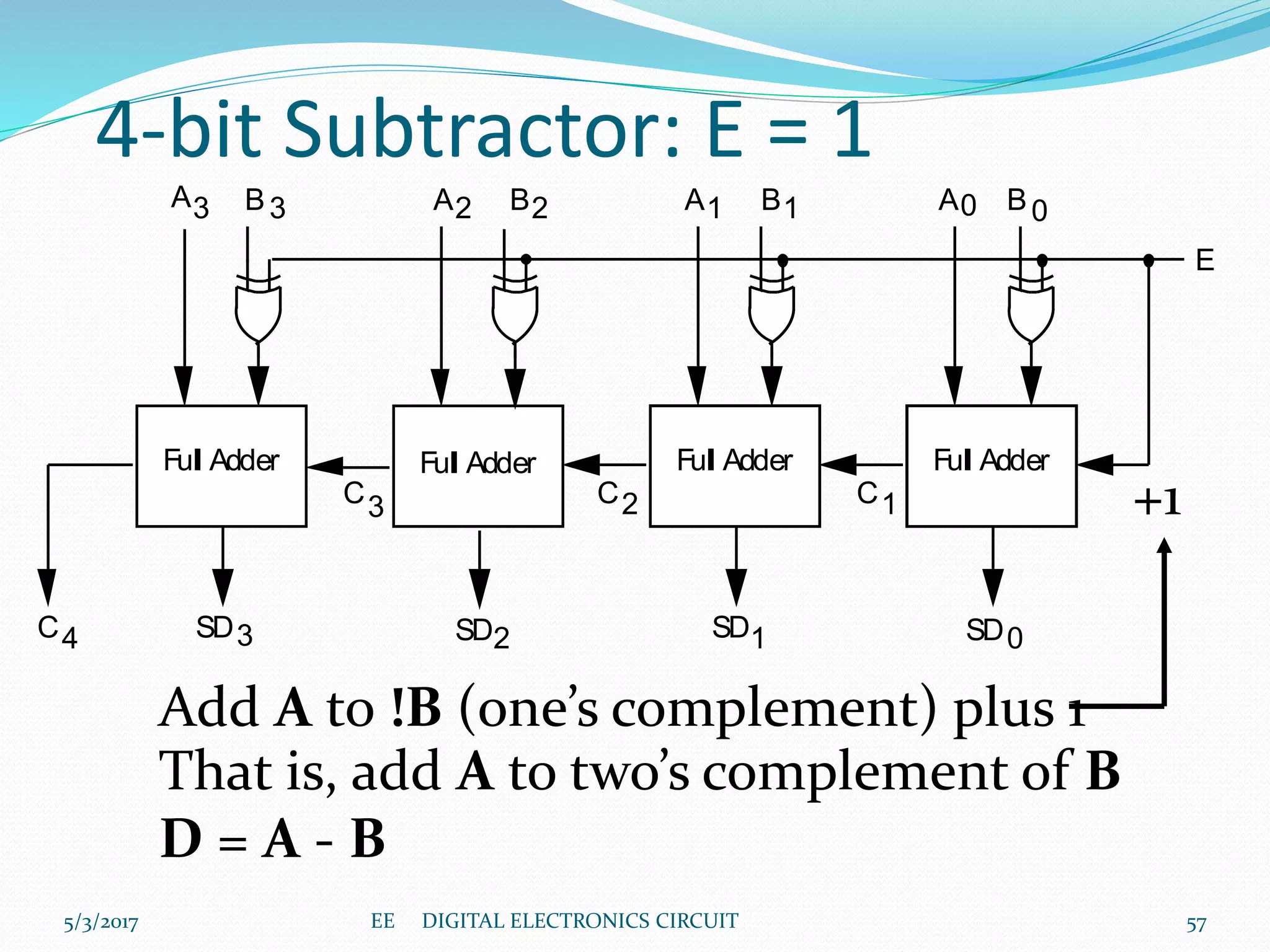

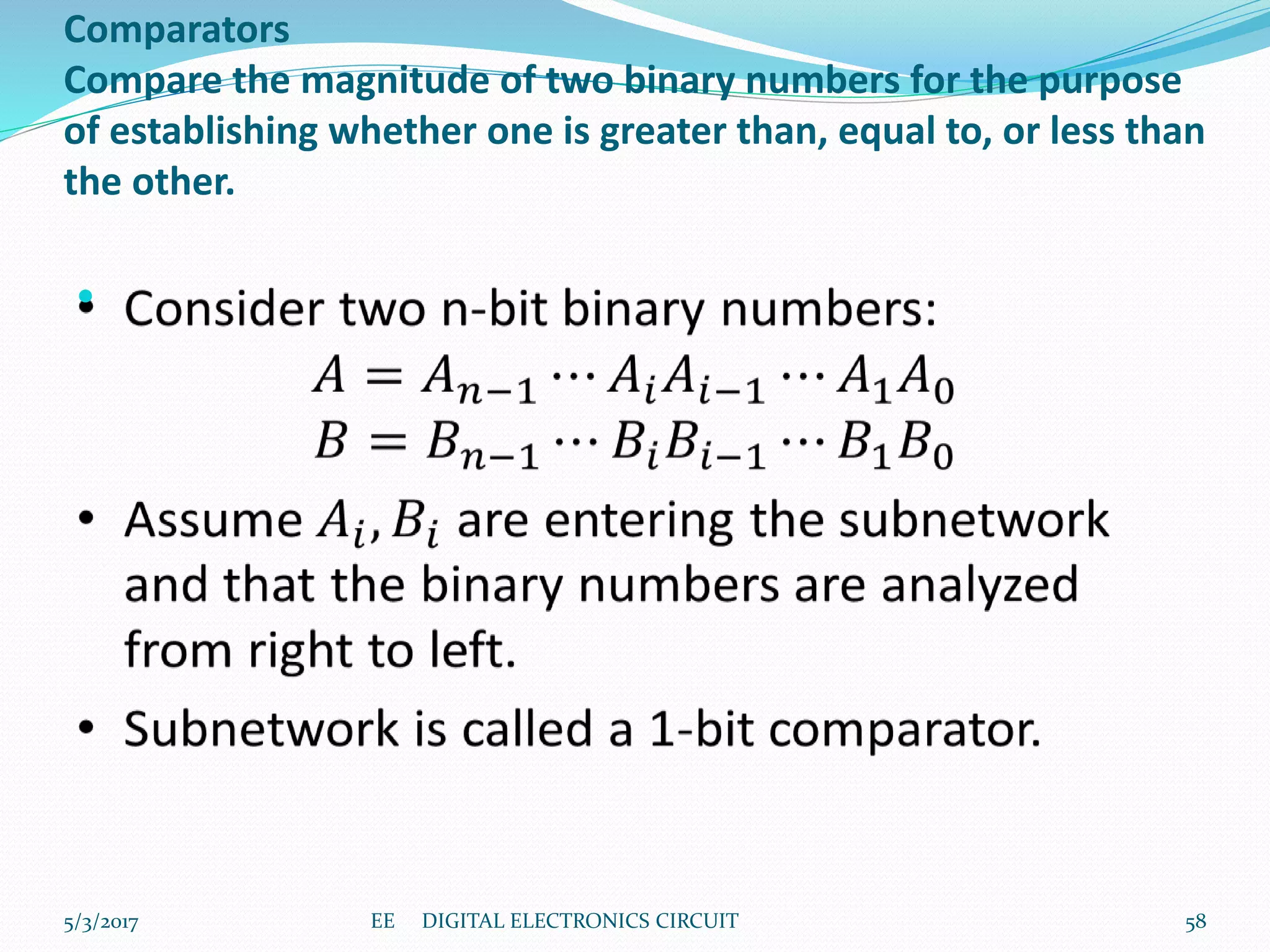

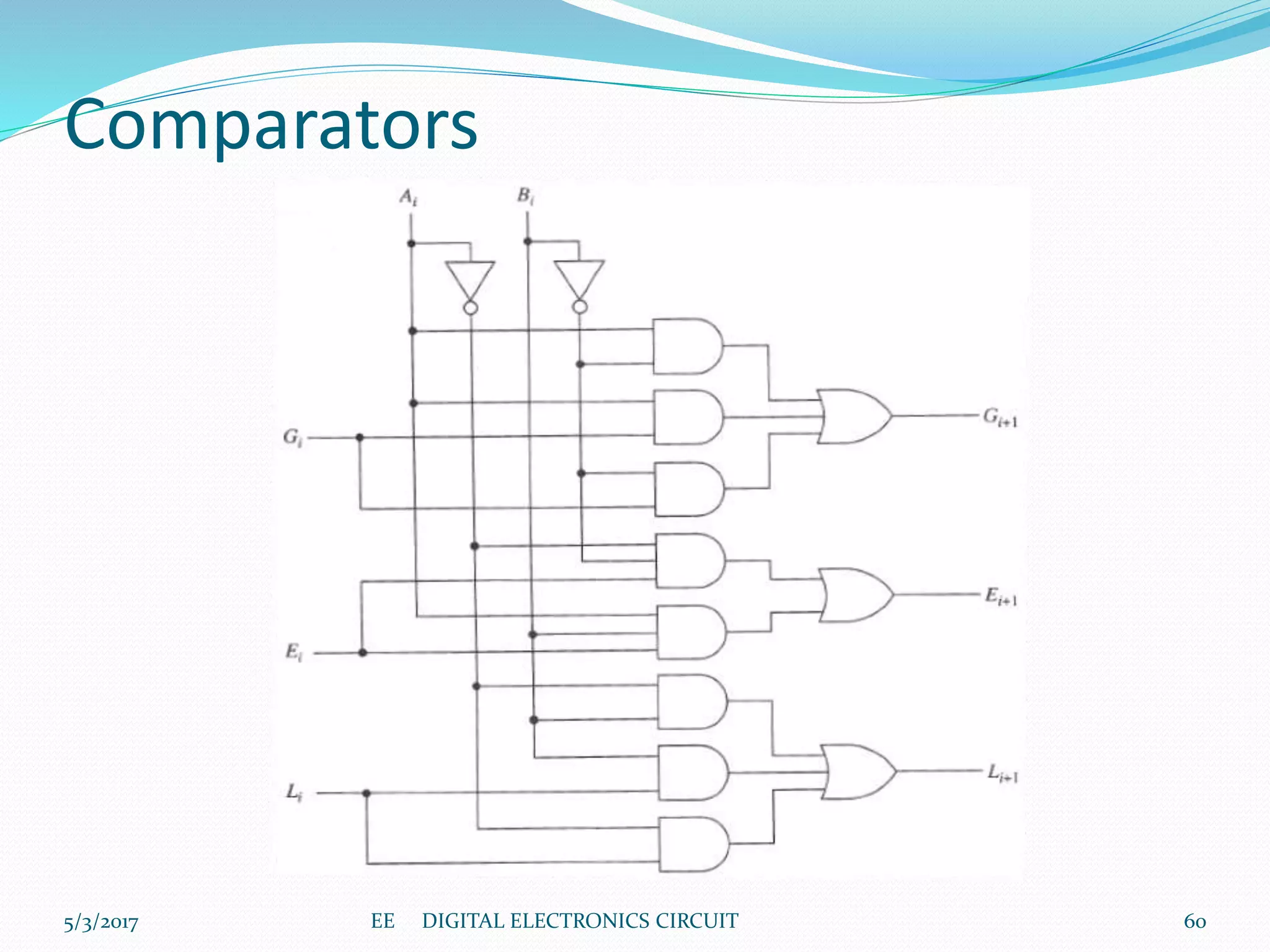

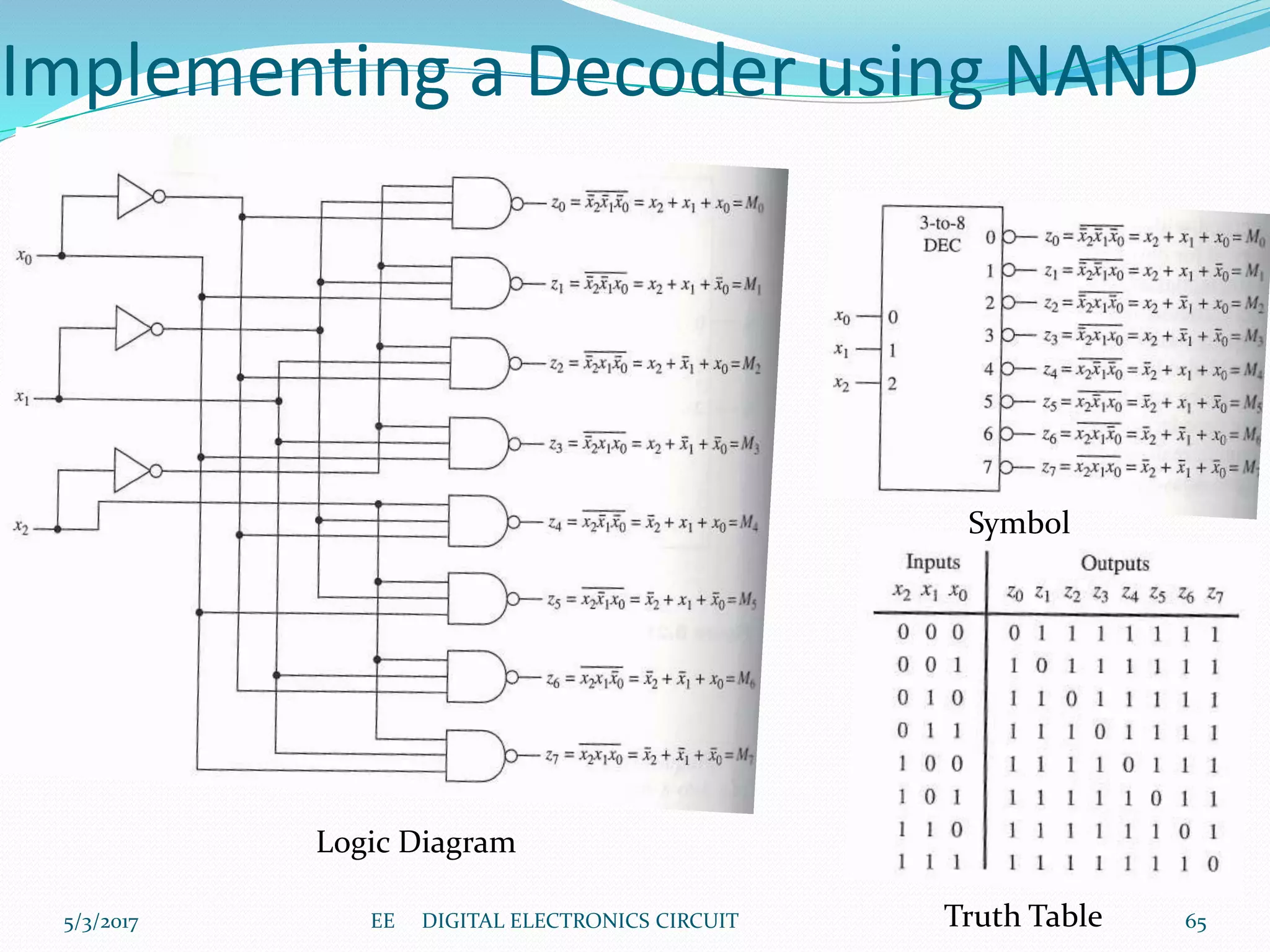

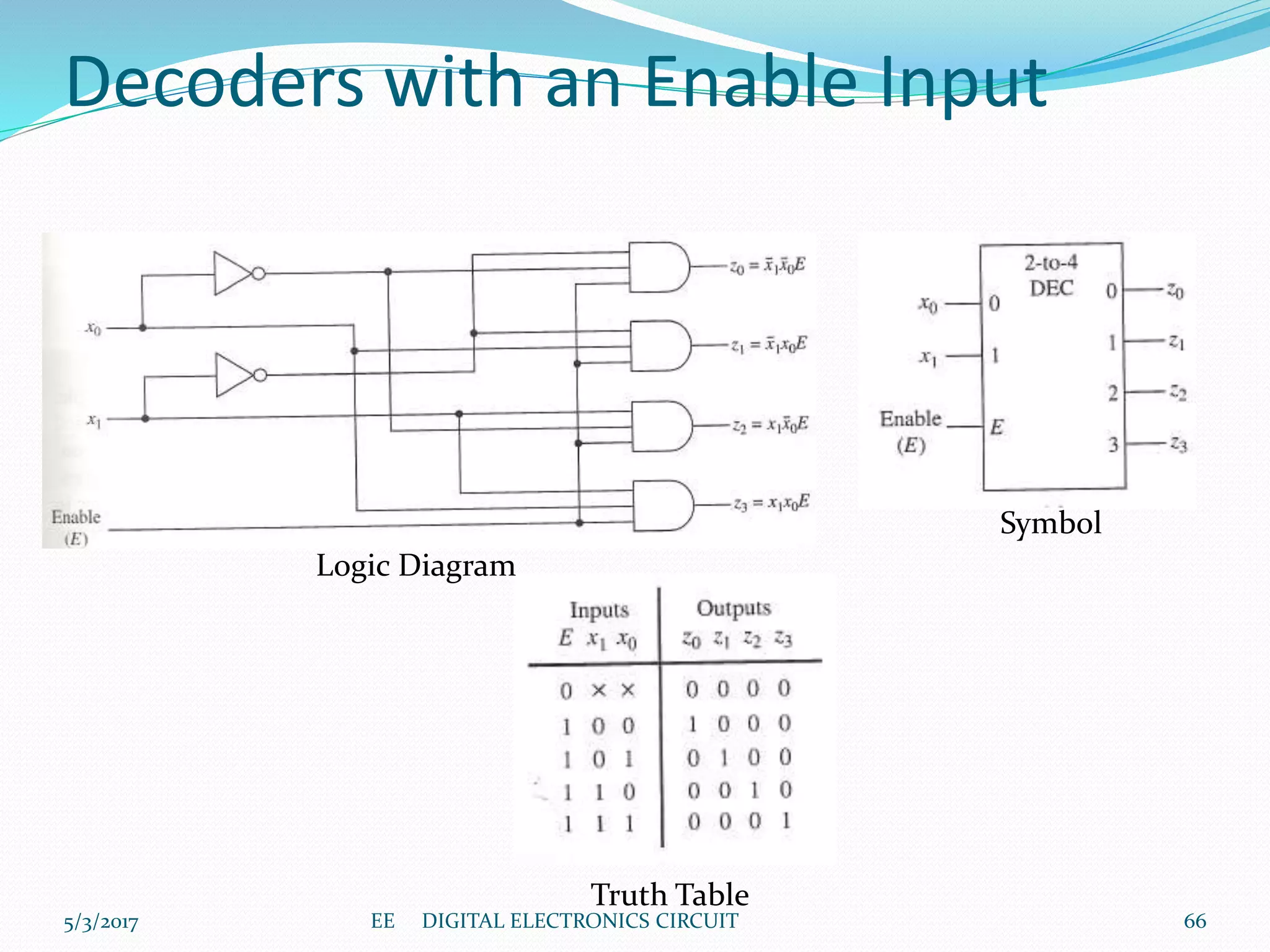

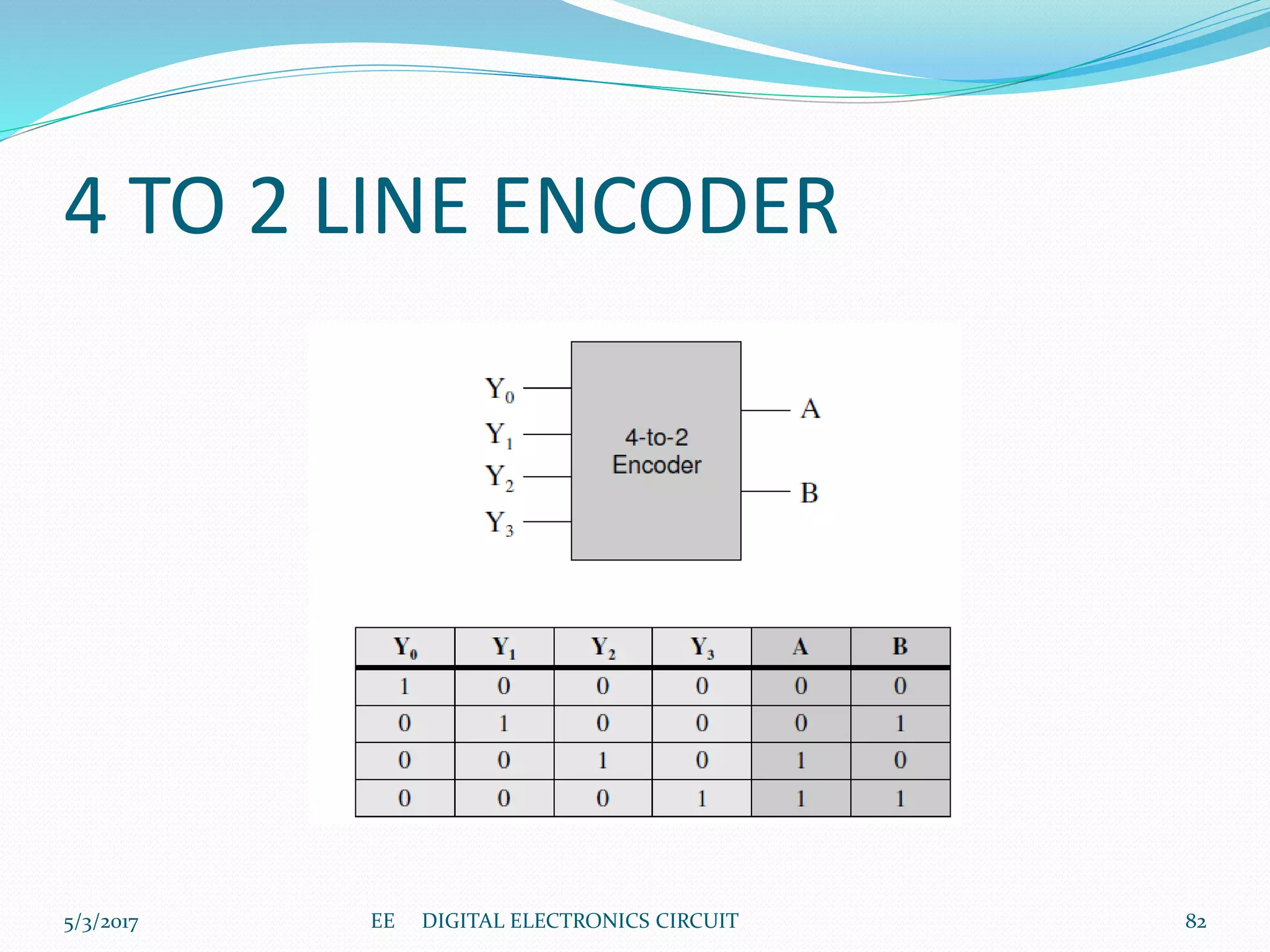

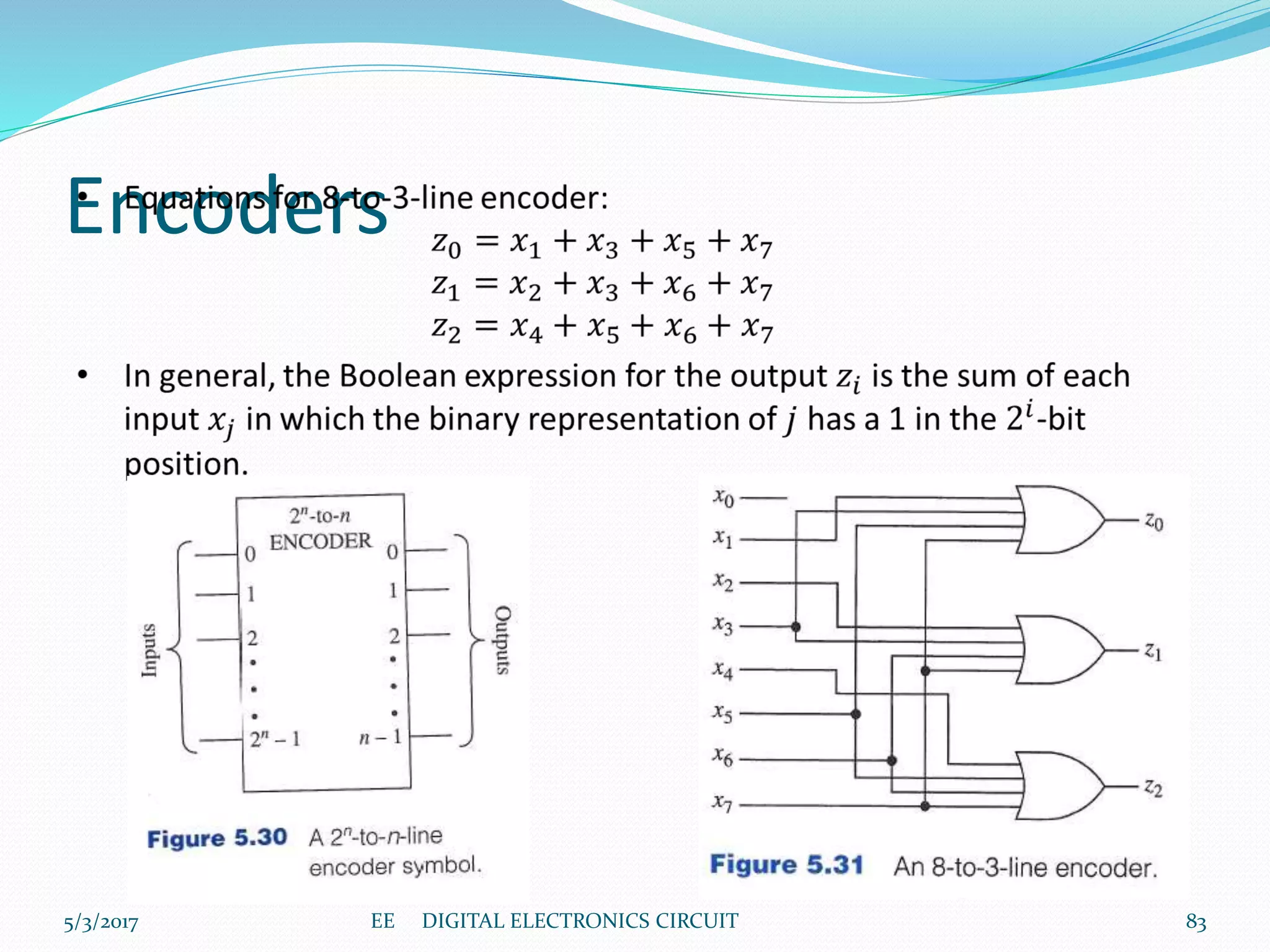

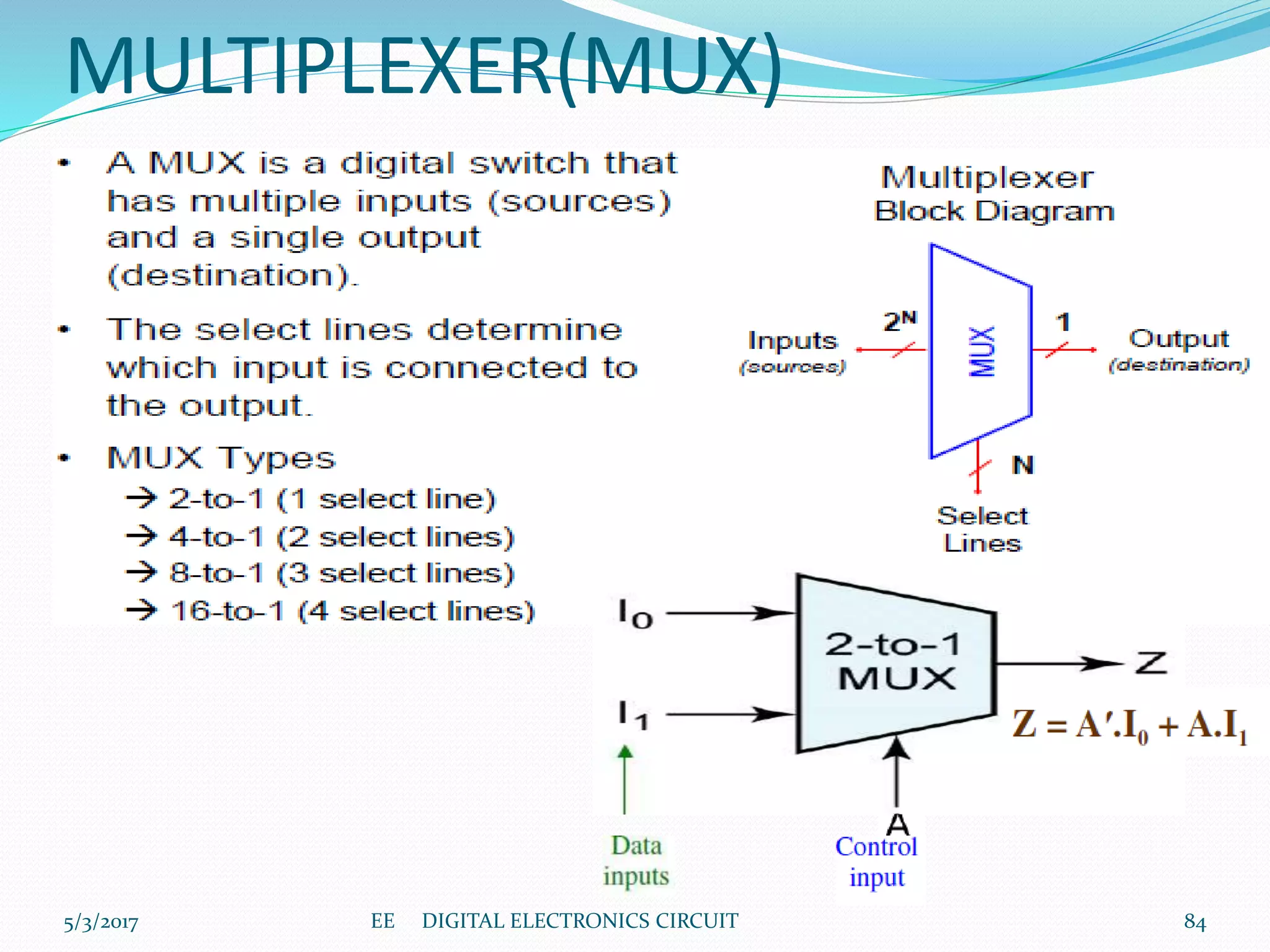

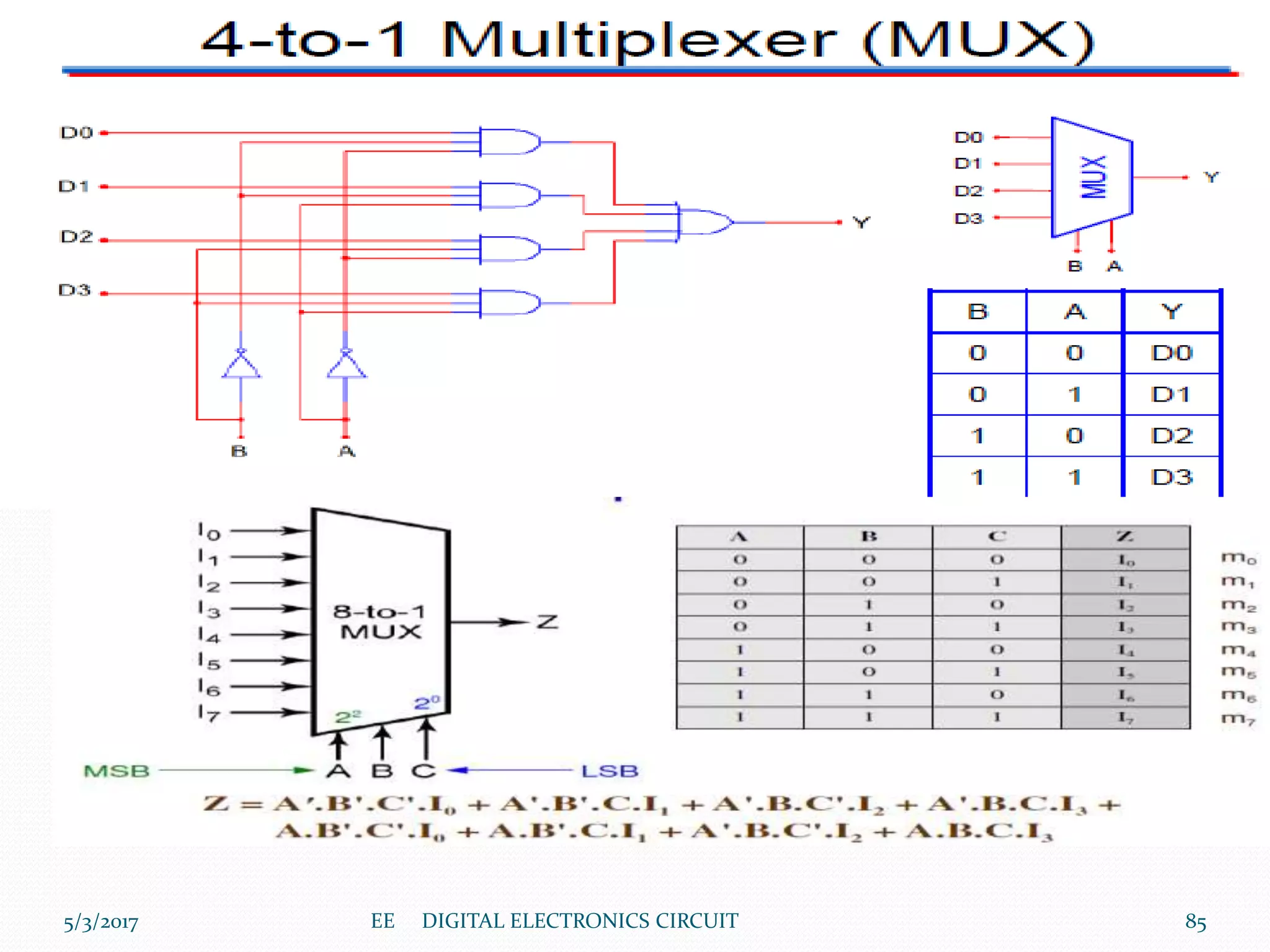

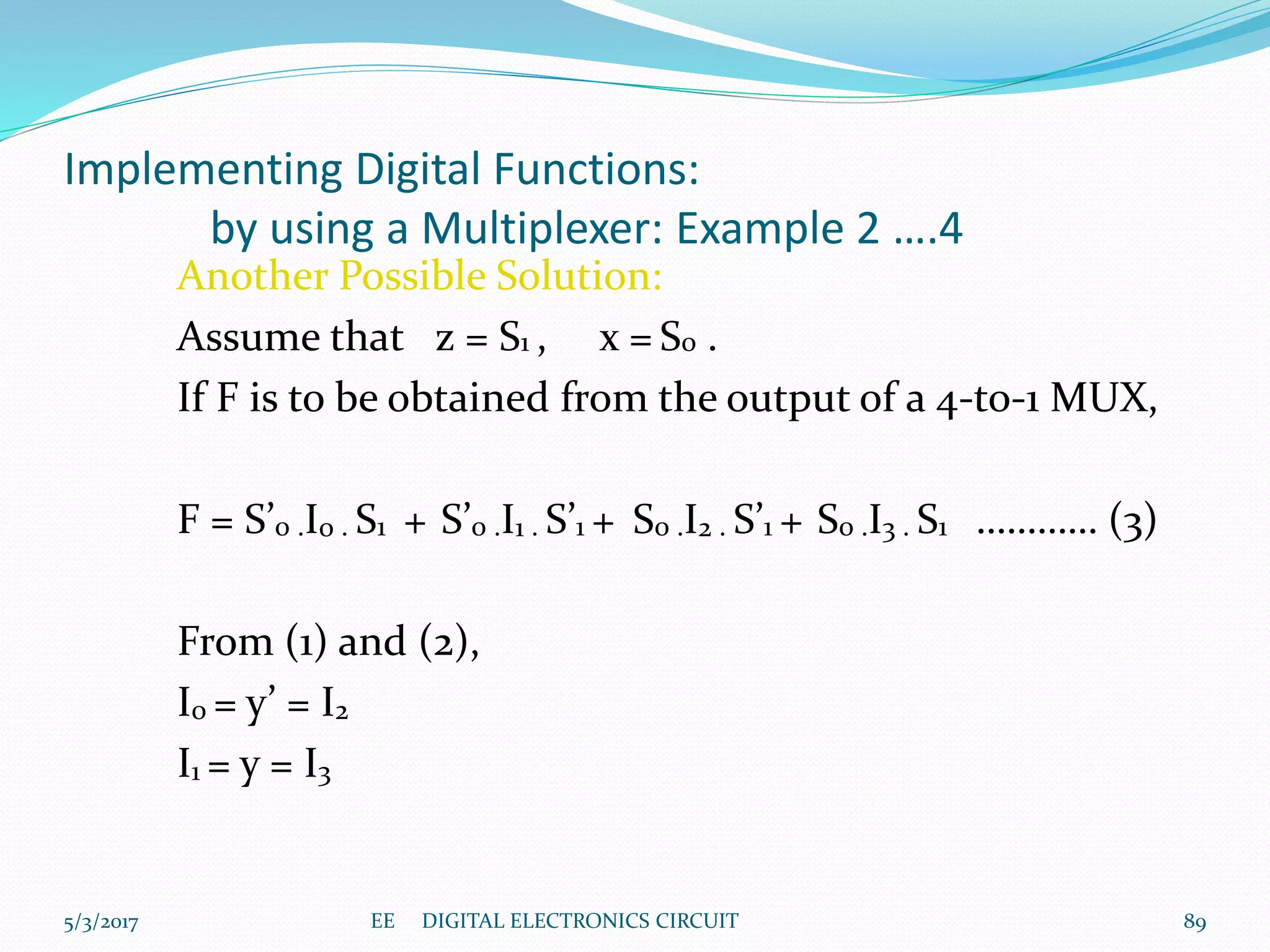

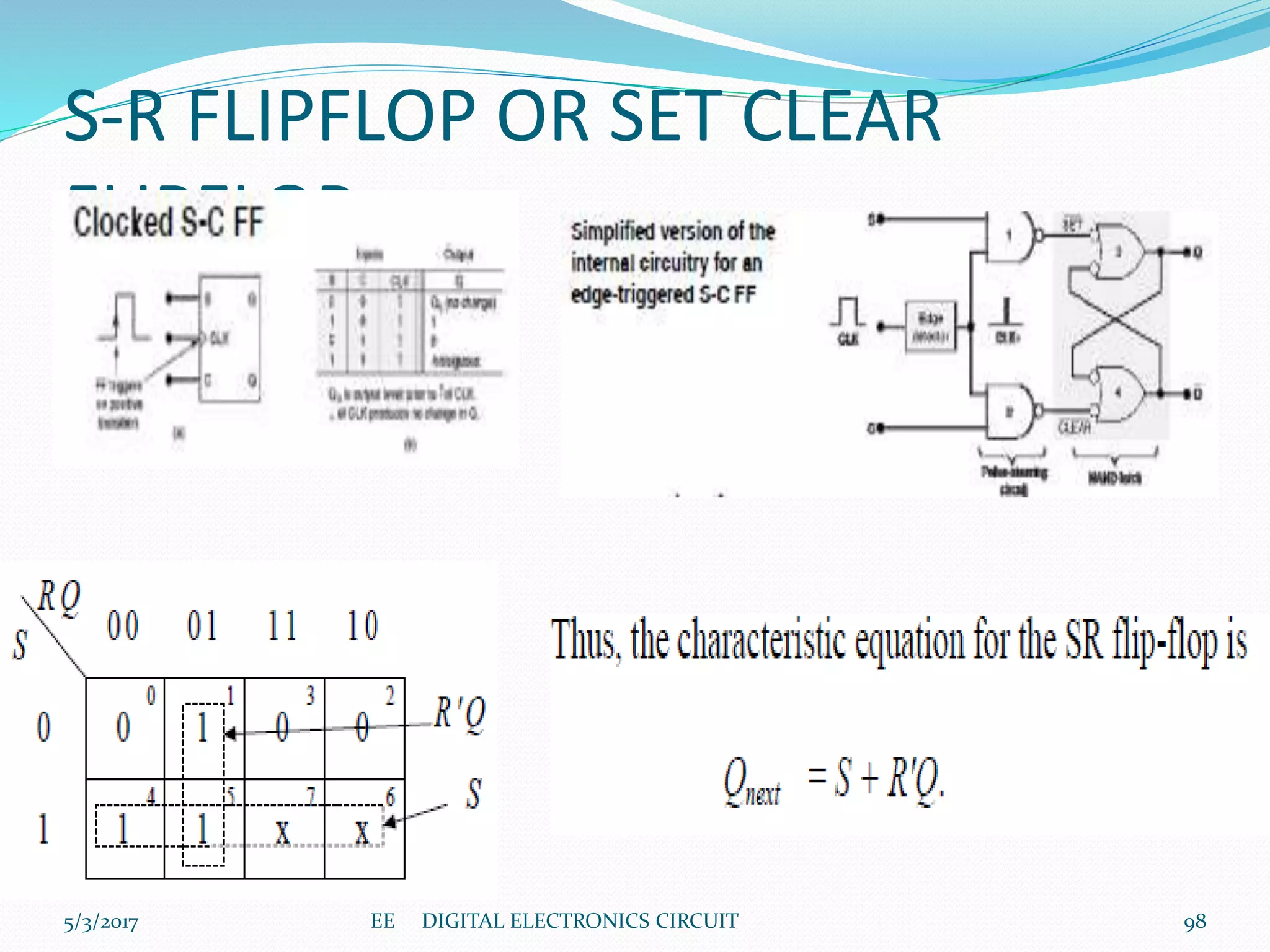

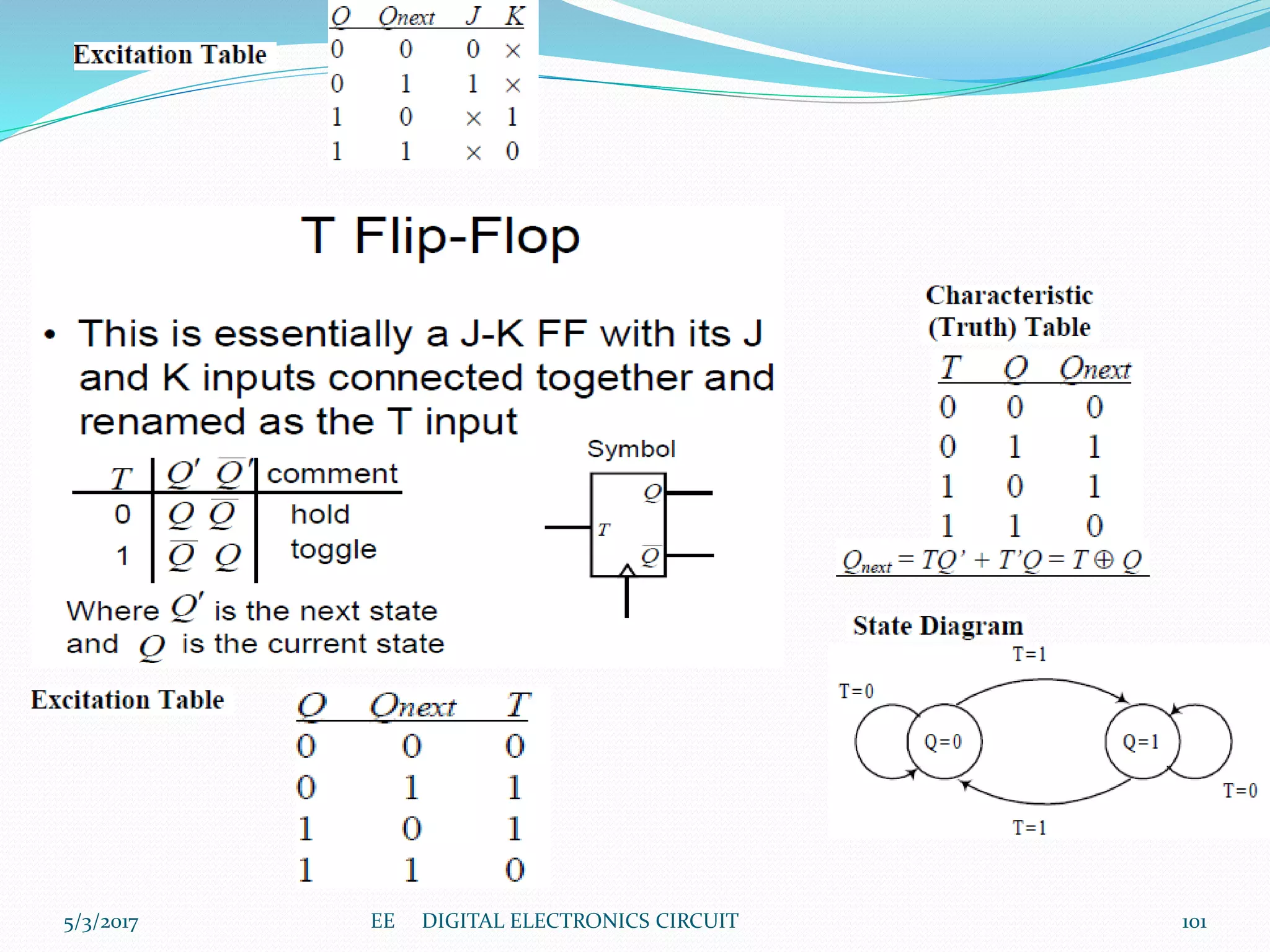

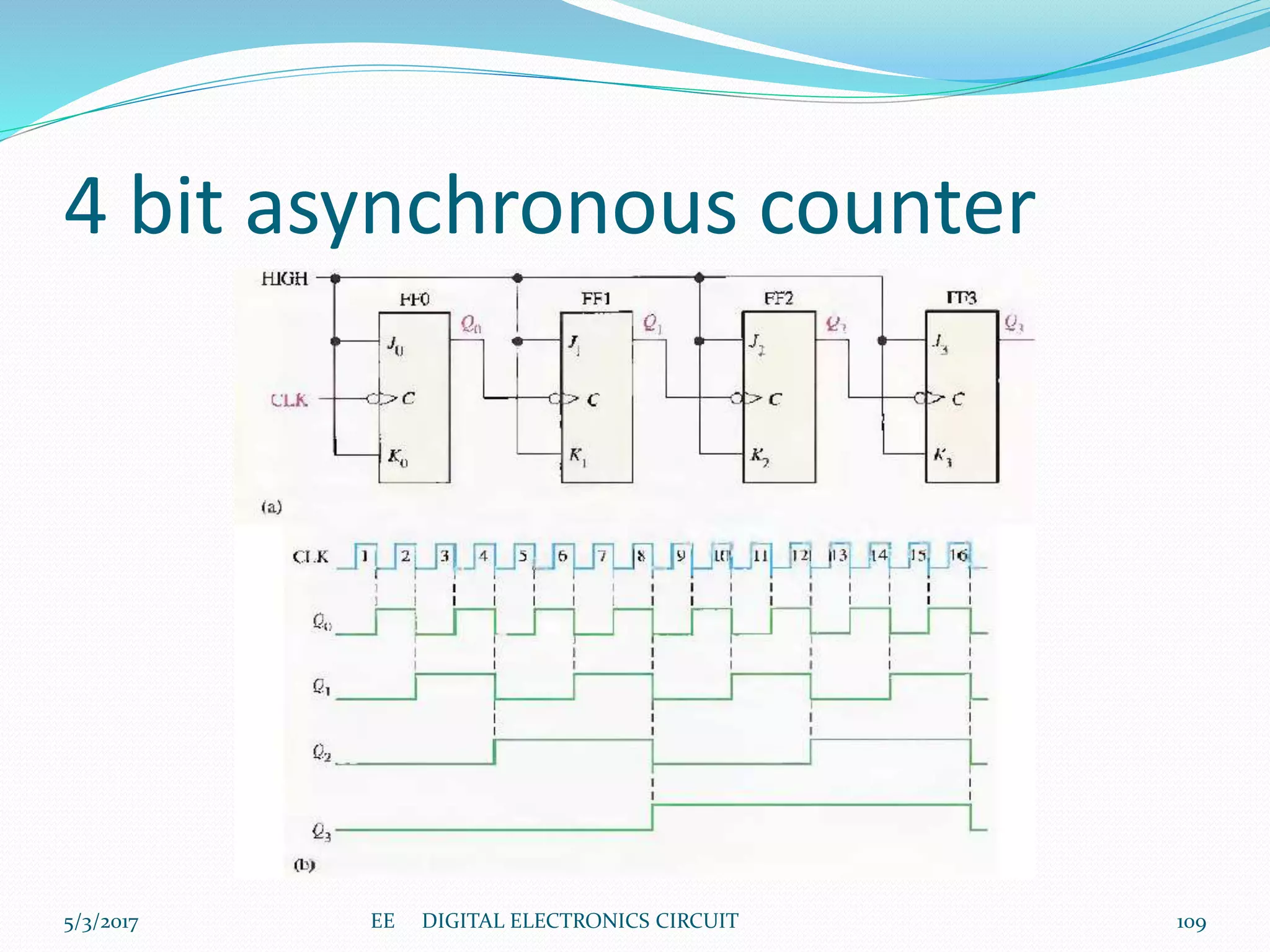

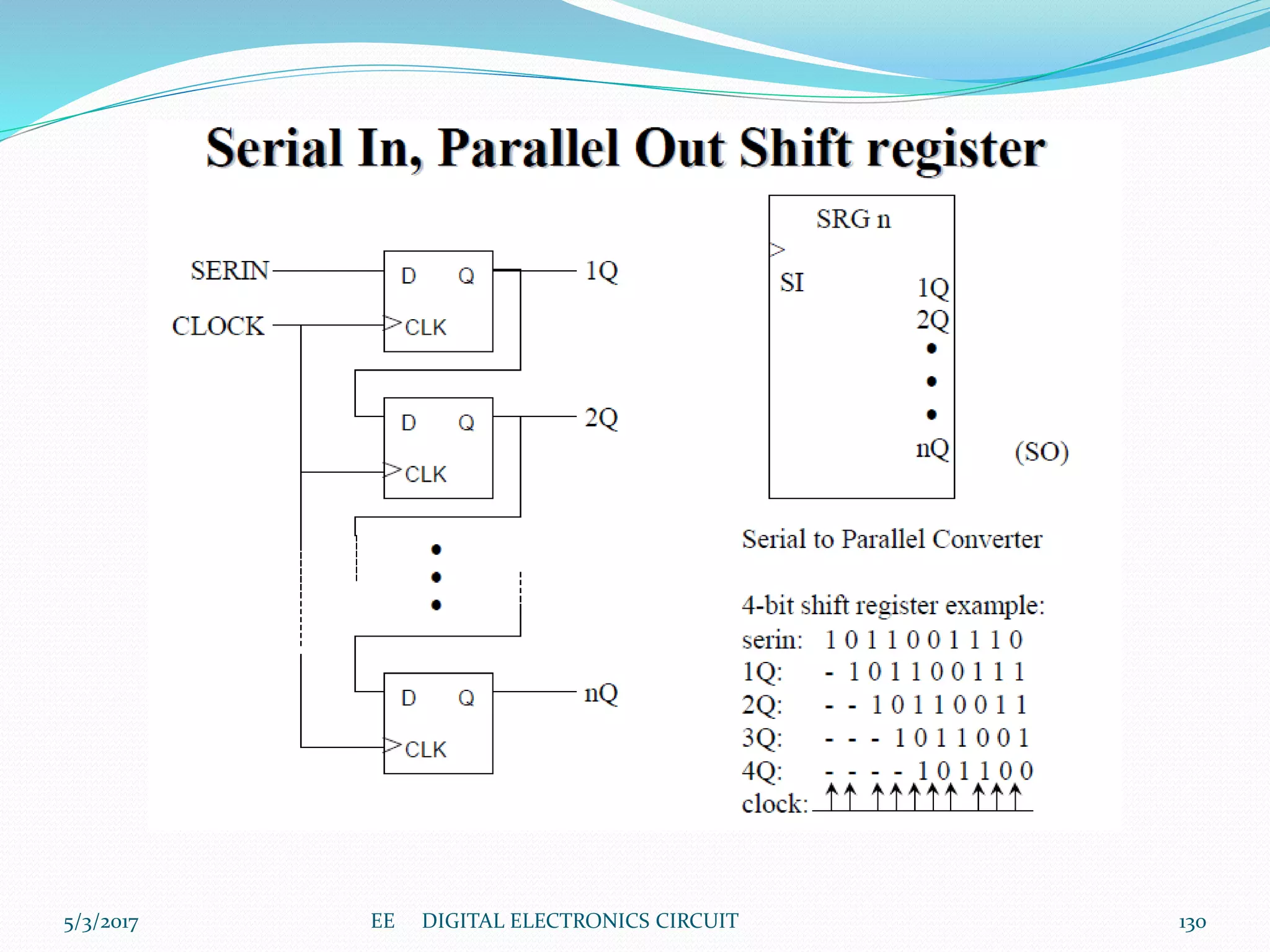

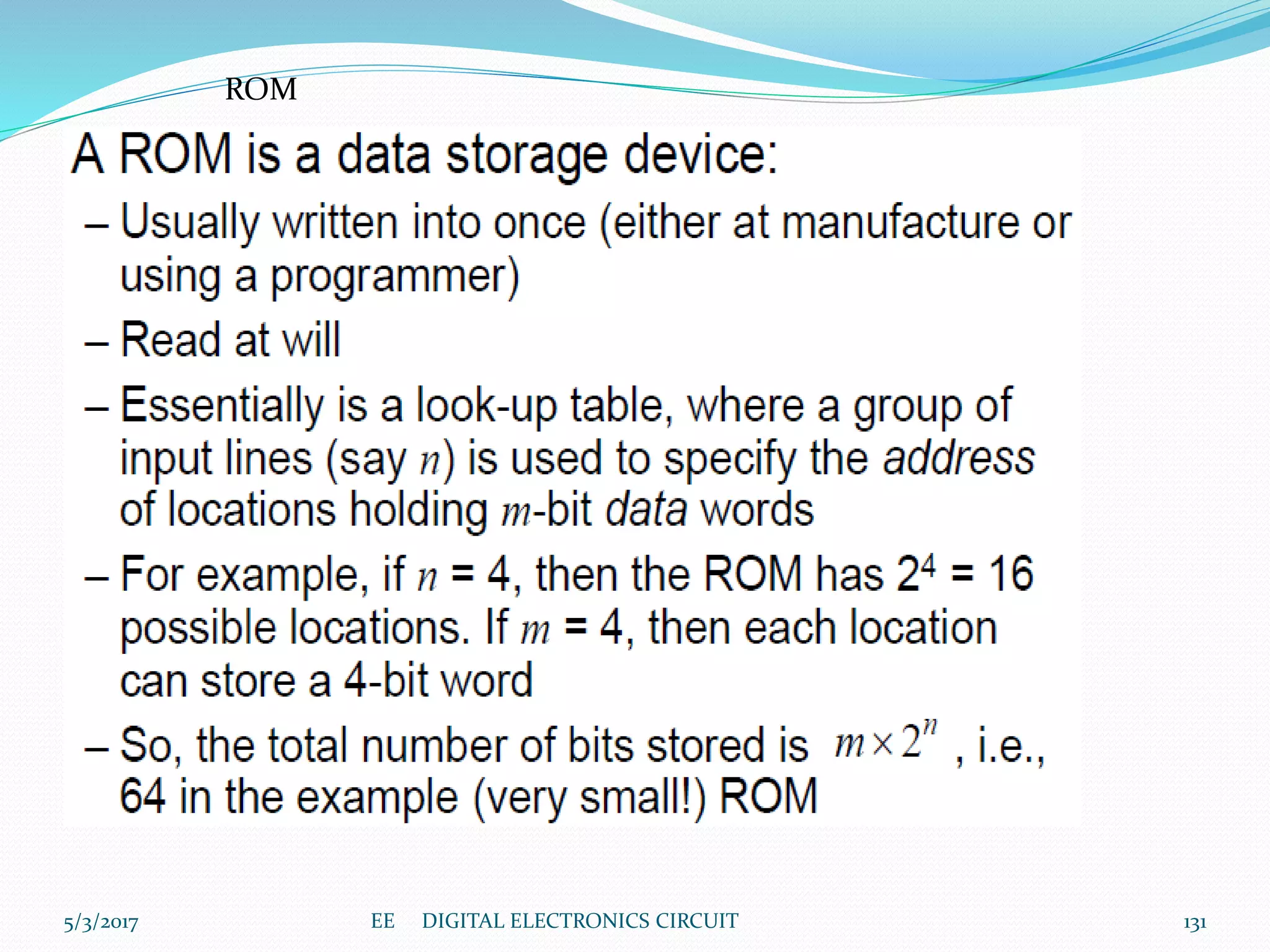

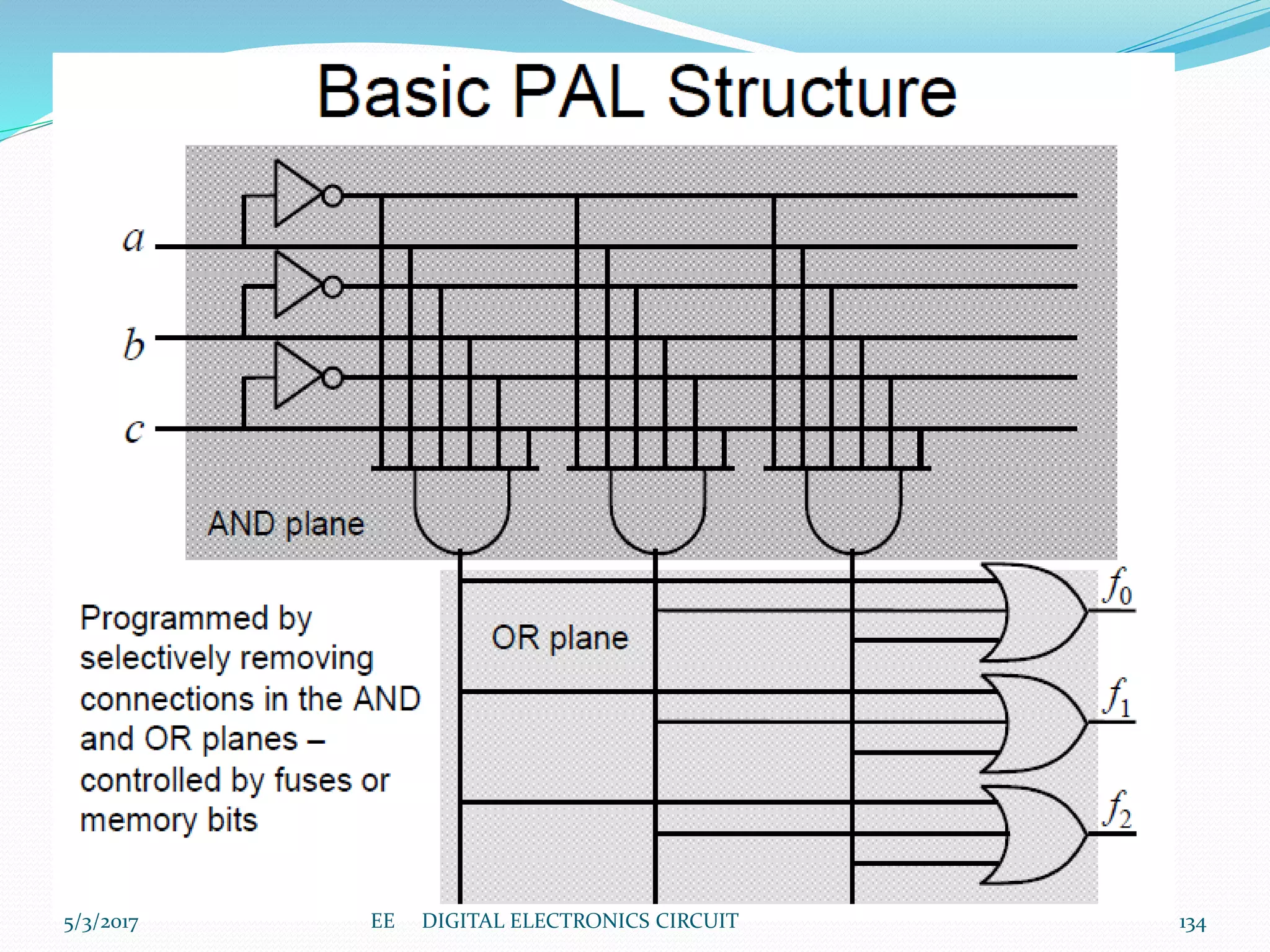

Module I covers number systems, binary codes, Boolean algebra, logic gates and truth tables. Module II focuses on combinational logic design including adders, encoders and multiplexers. Module III discusses sequential logic design, counters, shift registers, memory and programmable logic devices. The document lists common logic families and provides examples of number system conversions and Boolean logic simplifications. It is intended to outline the key topics that will be covered in the course.