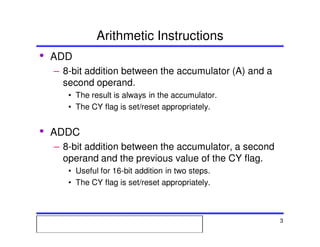

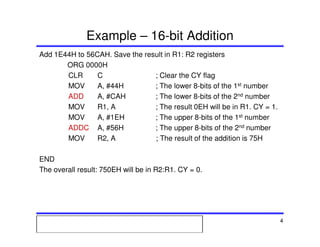

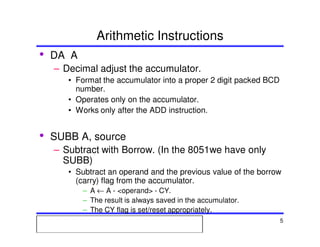

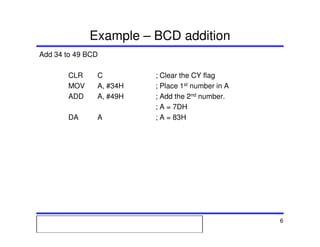

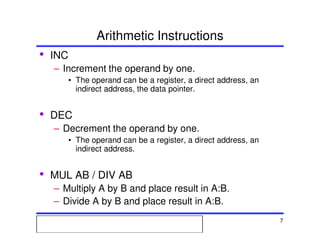

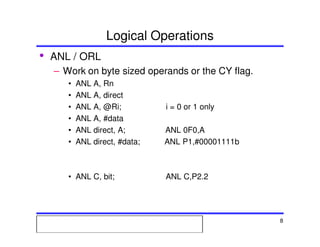

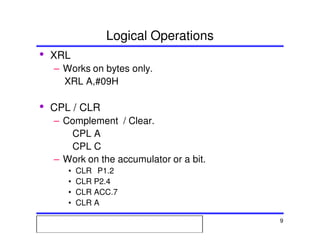

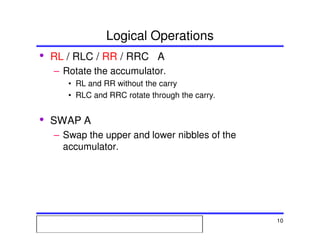

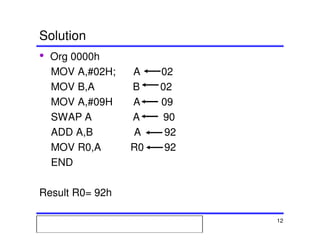

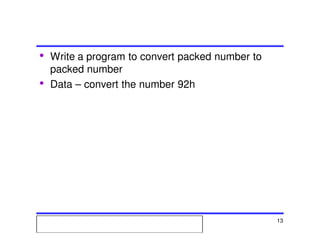

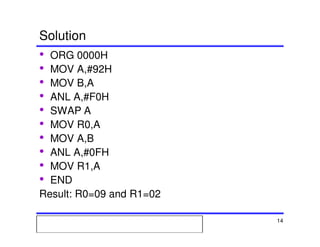

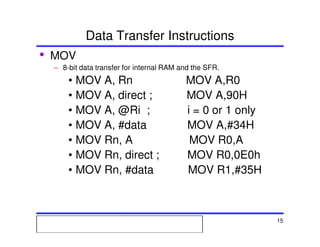

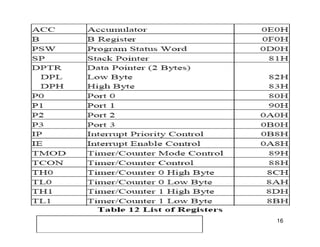

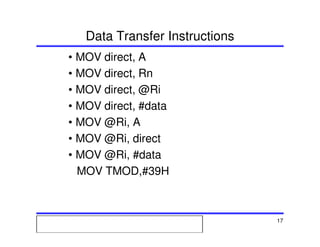

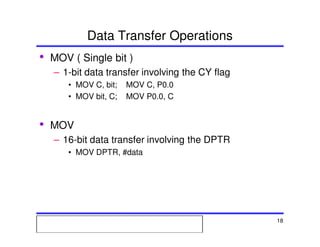

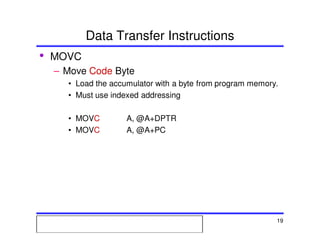

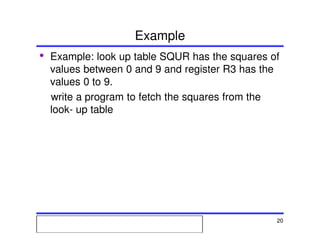

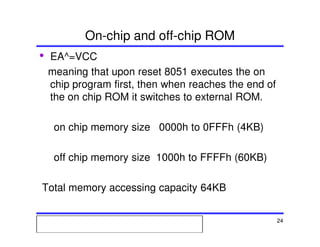

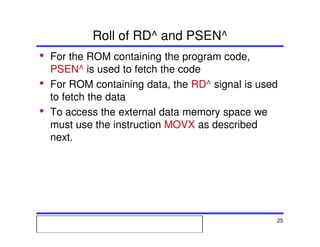

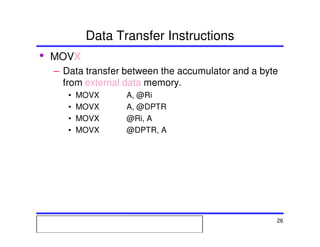

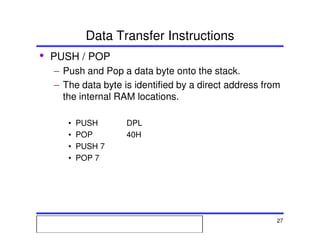

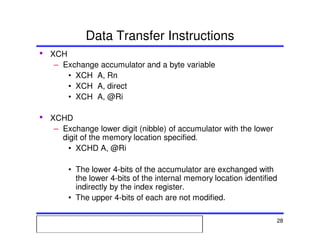

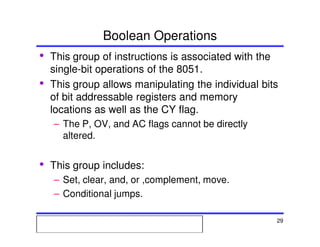

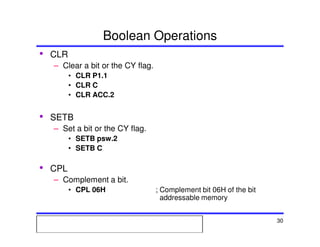

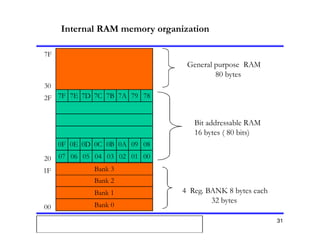

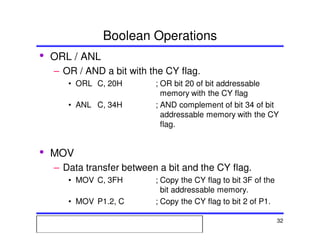

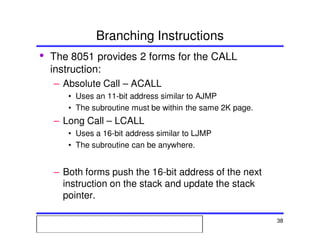

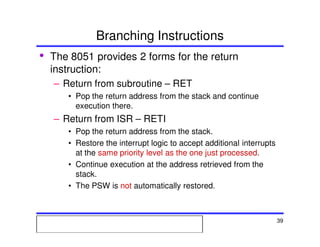

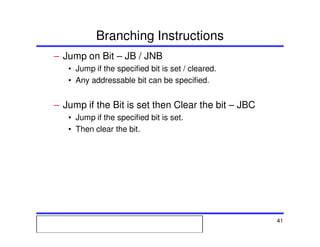

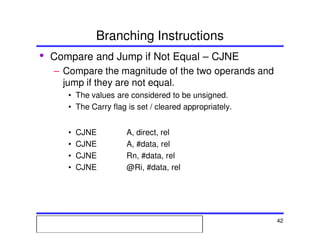

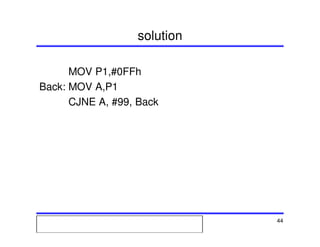

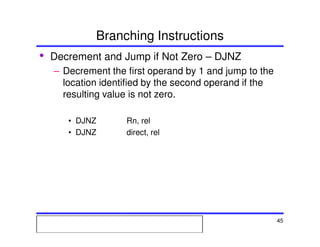

This document discusses the instruction groups of the 8051 microprocessor, including arithmetic, logic, data transfer, boolean, and branching instructions. It provides examples of instructions such as ADD, MOV, ANL, XCH, PUSH, POP, and MOVX. Specific instructions like ADD, SUB, AND, OR, XOR, INC, DEC, SWAP are explained along with examples of their usage. On-chip and off-chip memory access using RD and PSEN signals is also covered.