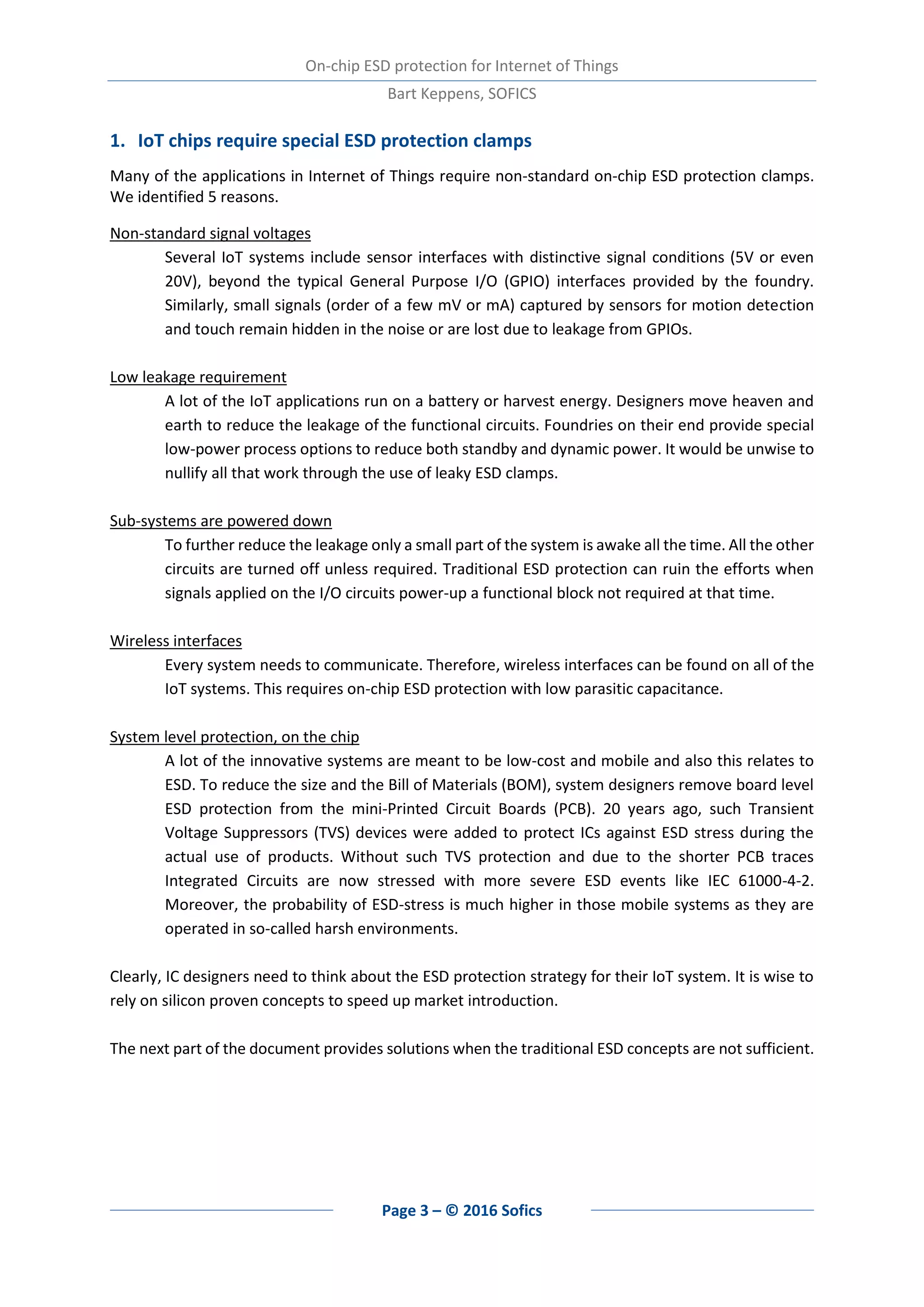

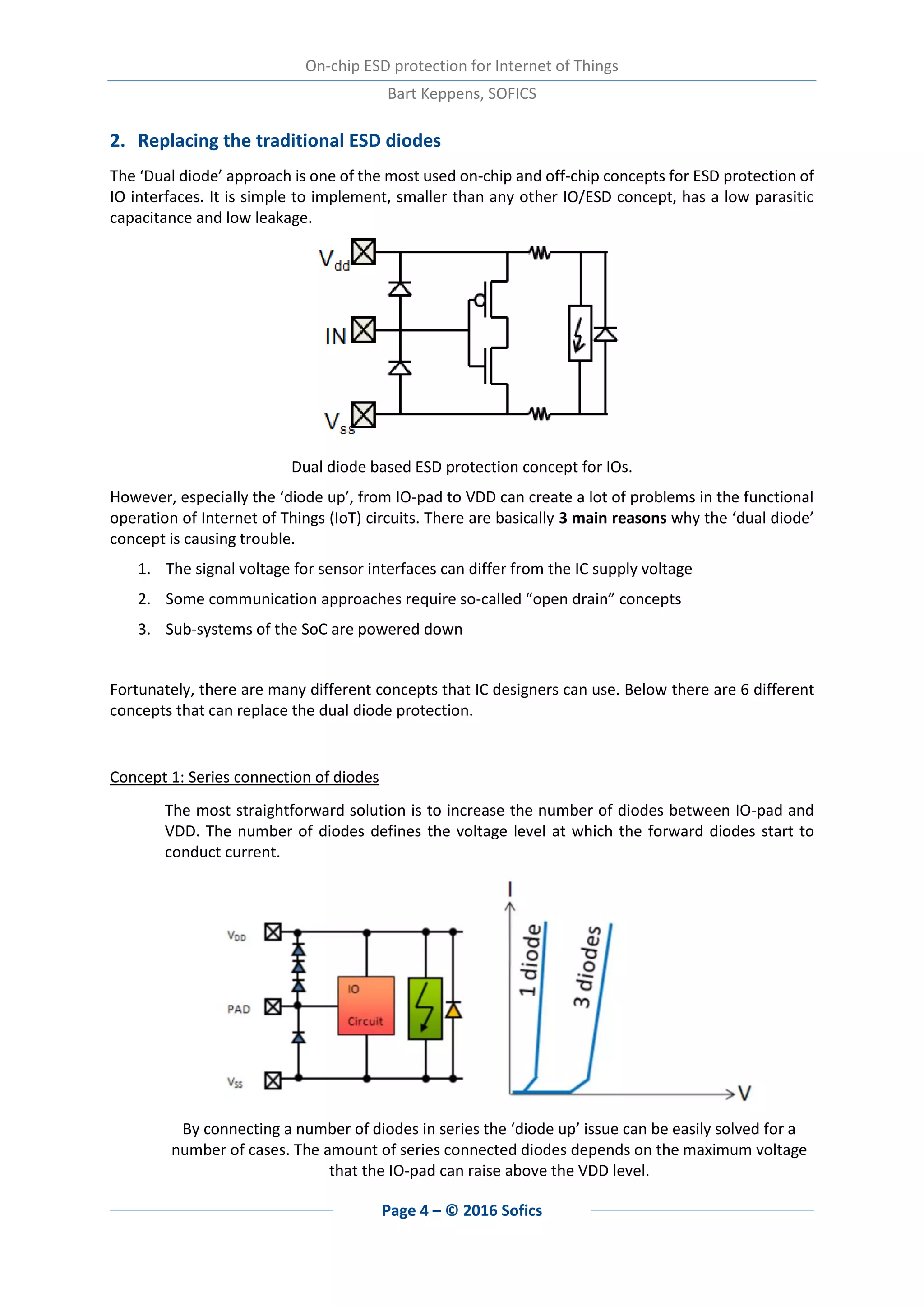

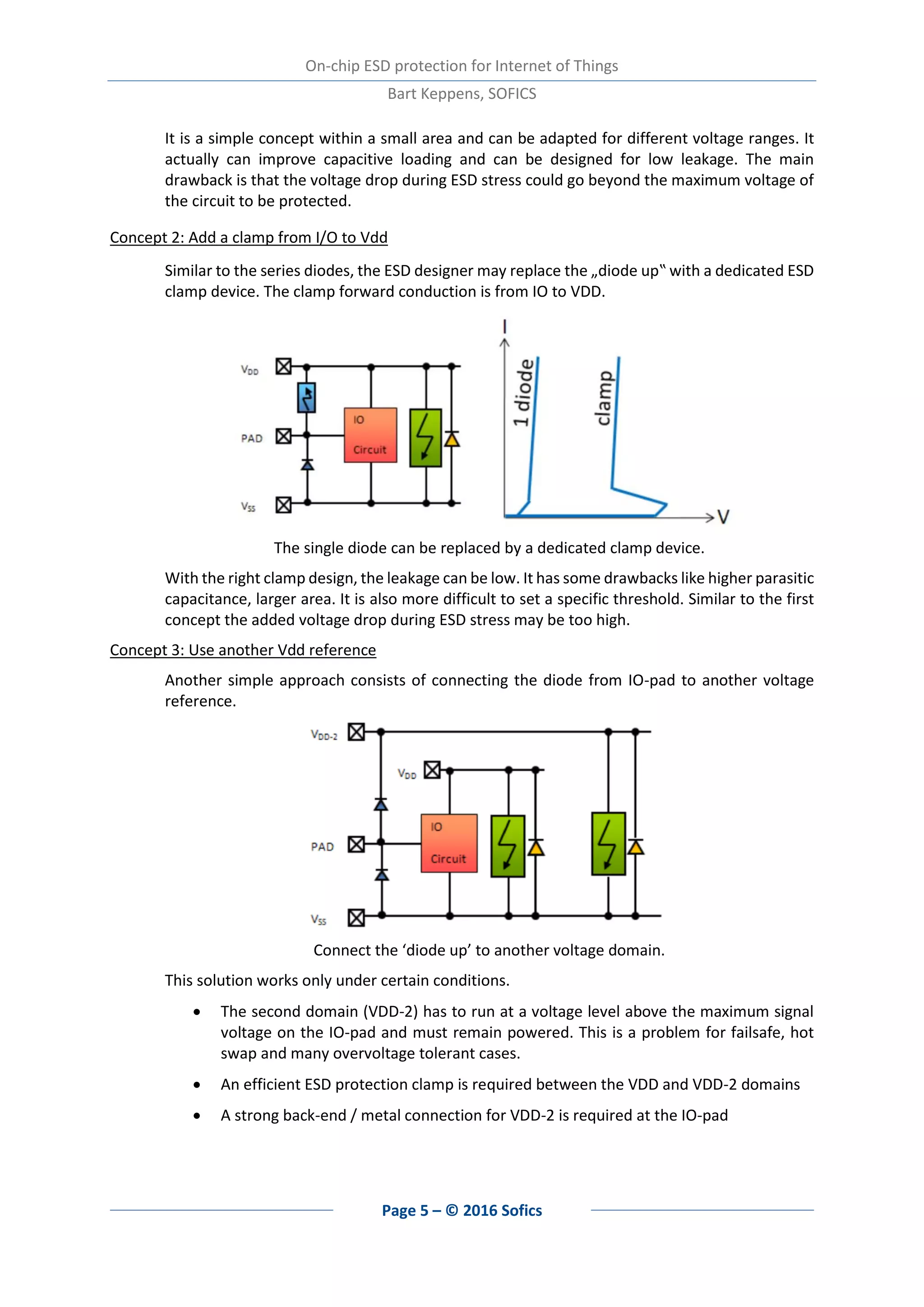

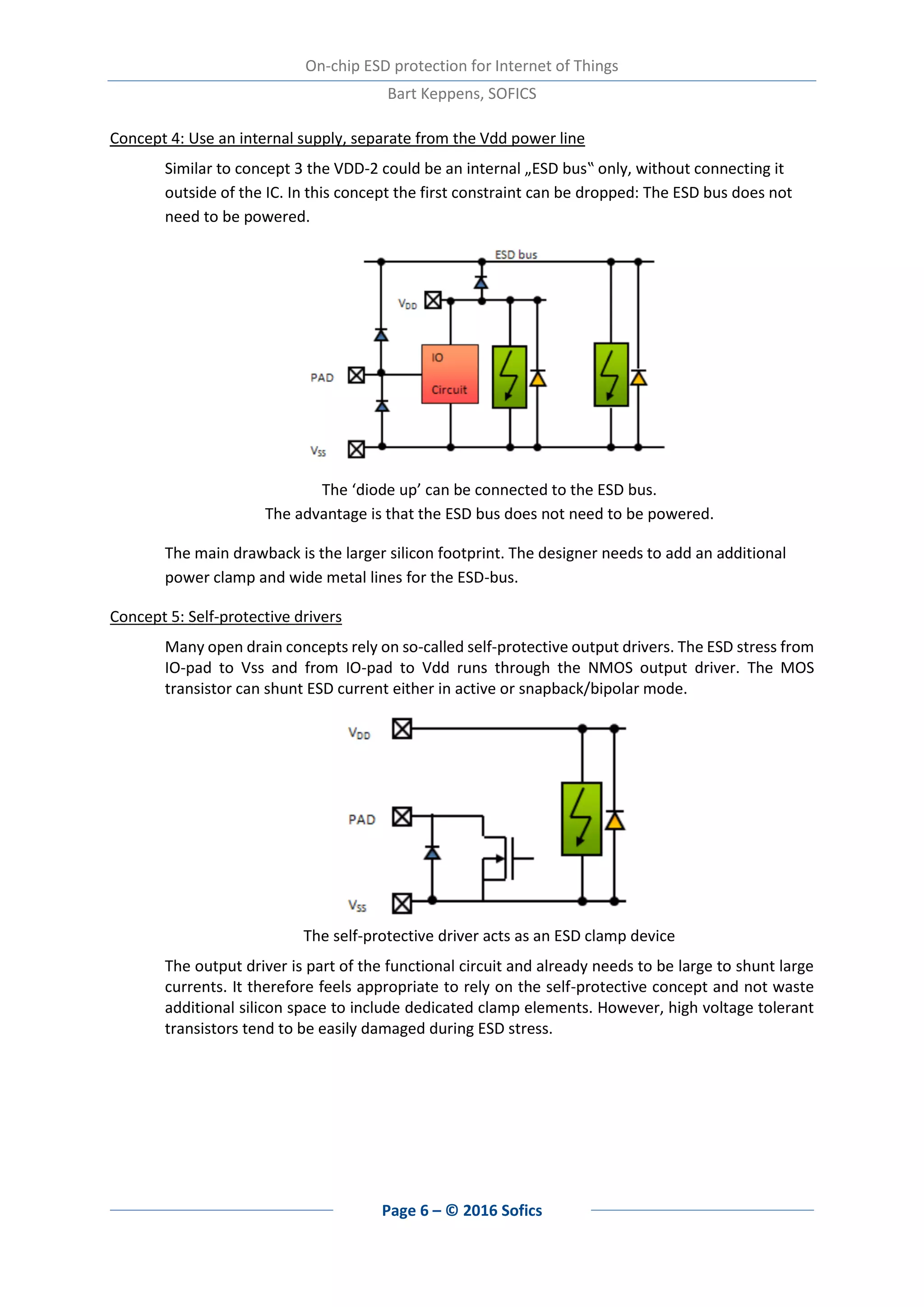

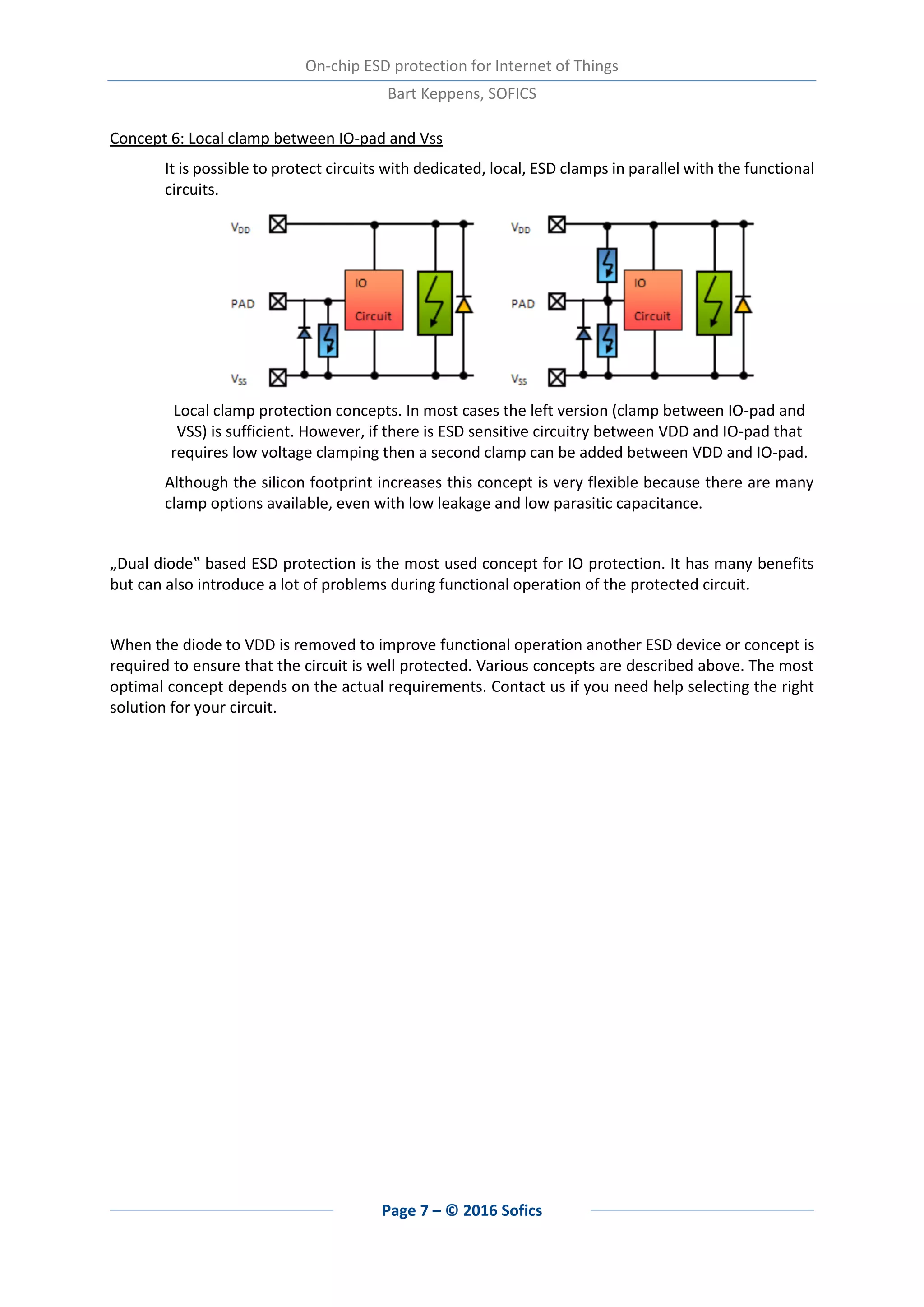

The document discusses on-chip electrostatic discharge (ESD) protection for Internet of Things (IoT) devices, emphasizing the need for non-standard ESD clamps due to unique requirements such as varying signal voltages and low leakage needs. It outlines various solutions to replace traditional dual diode ESD protection methods that may introduce operational issues, advocating for tailored approaches depending on specific circuit requirements. Lastly, it highlights the importance of considering environmental factors and reliable specifications for ESD/EOS during the design of IoT applications.