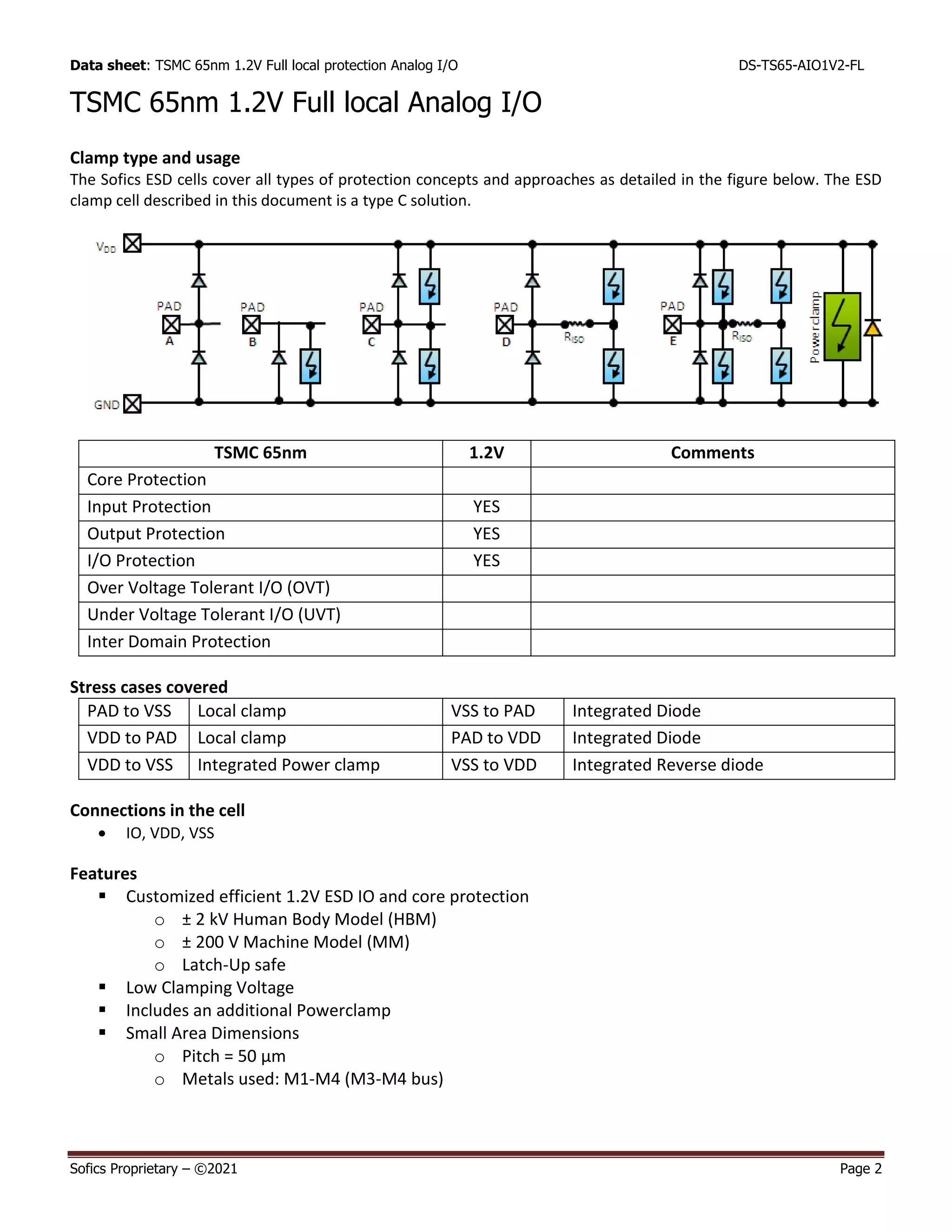

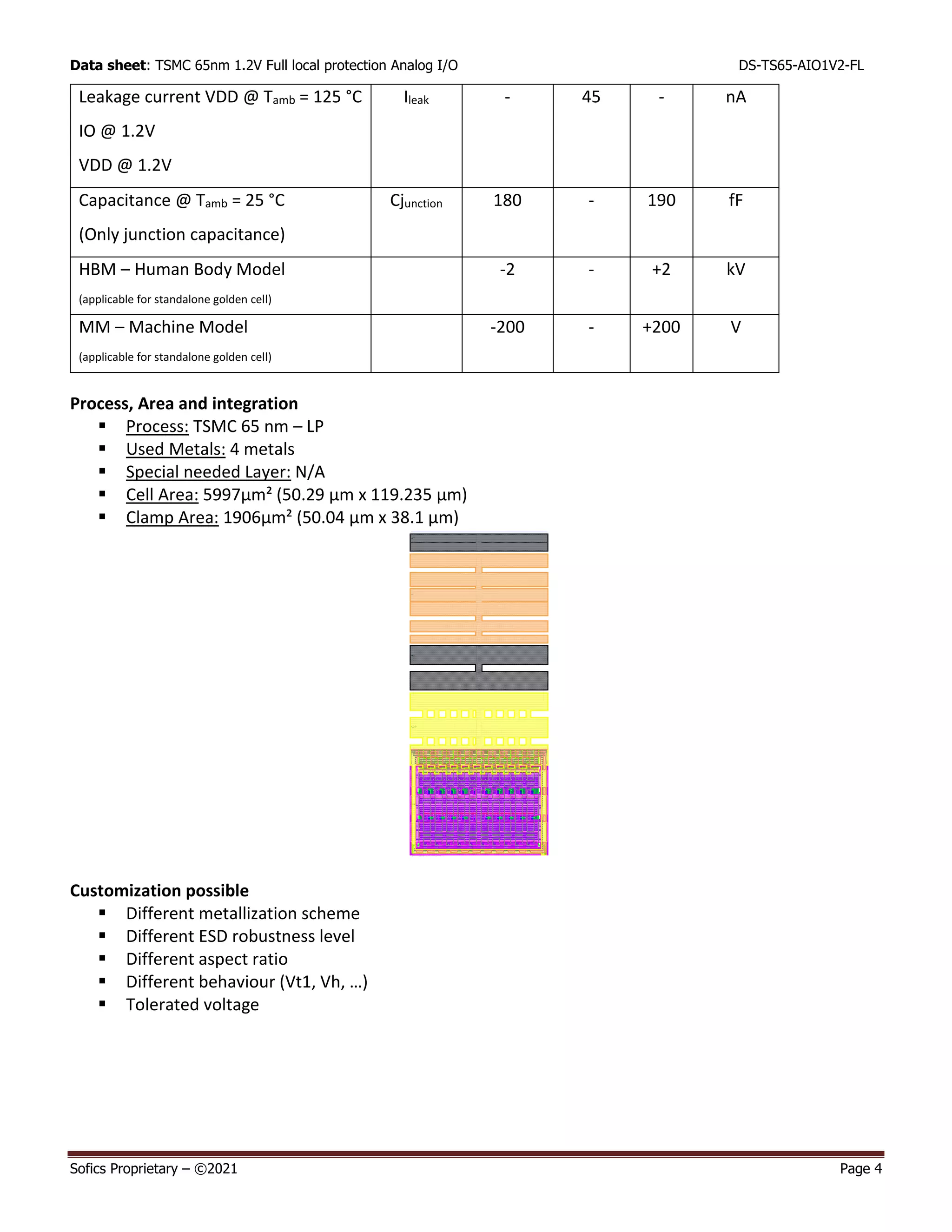

Sofics has developed and verified its Takecharge ESD protection clamps for various technology nodes down to 5nm, enhancing IC protection for multimedia and wireless interfaces. The document details a specific Type C ESD clamp for 1.2V analog I/O pads utilizing TSMC's 65nm process, highlighting its performance characteristics and maximum ratings. Additionally, it emphasizes Sofics' extensive experience in providing customized ESD solutions, having supported numerous companies globally.