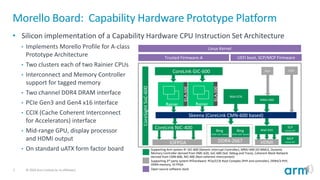

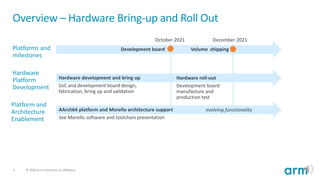

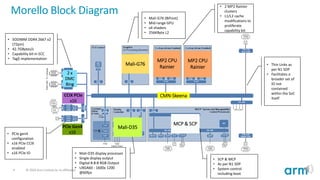

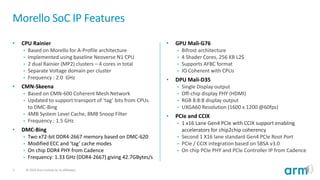

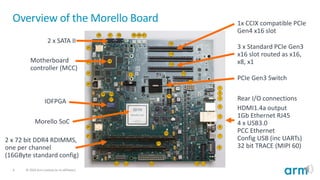

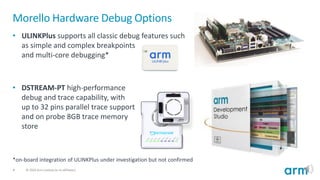

The document provides an overview of the Morello technology demonstrator hardware, detailing its CPU architecture, hardware capabilities, and development phases. It highlights the specific features of the Morello board, including multiple CPU clusters, memory interfaces, and GPU specifications. Additionally, it discusses the hardware roll-out and future software support for the Morello architecture.