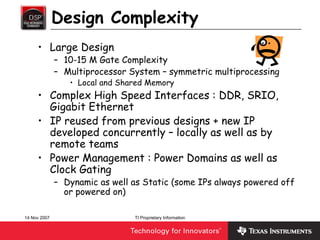

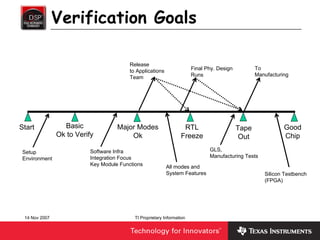

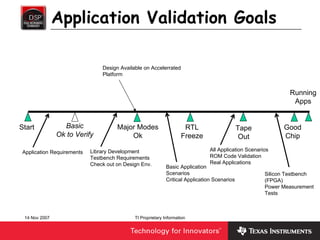

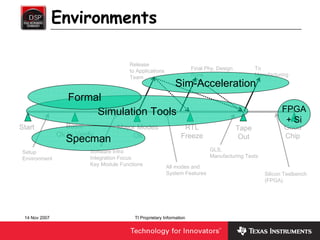

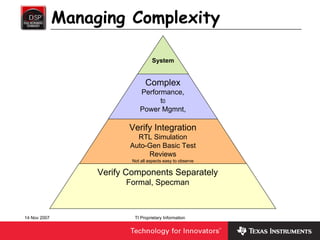

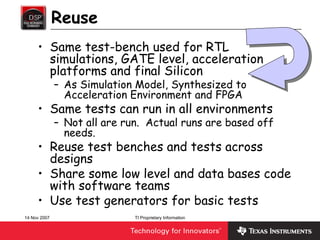

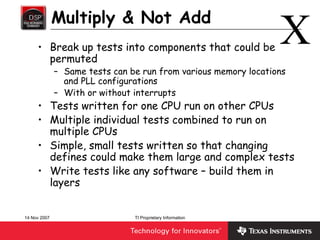

This document discusses design verification for a complex multiprocessor system-on-chip (SoC). It outlines the goals of validating the design for its intended applications and managing the complexity through: 1) breaking down verification into components; 2) staging verification over multiple environments; and 3) reusing tests, environments, and code across designs and teams.