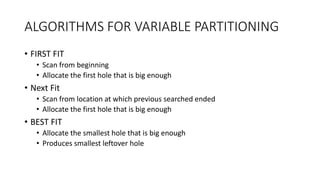

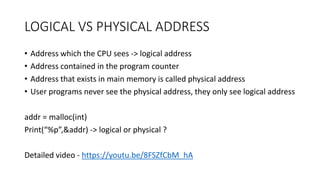

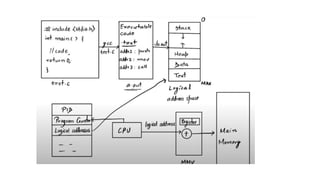

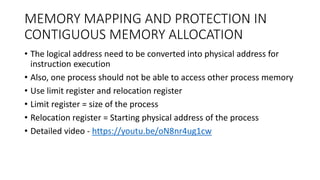

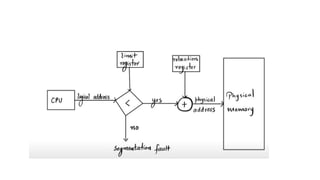

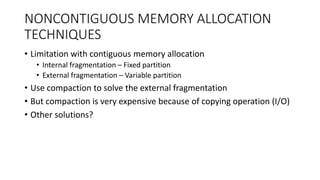

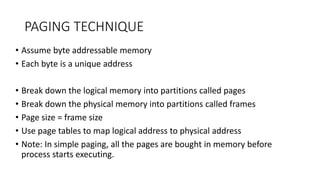

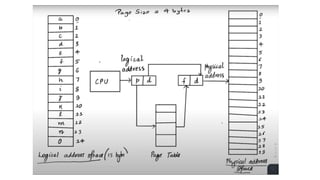

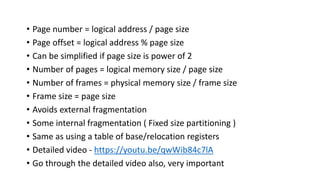

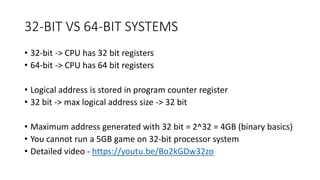

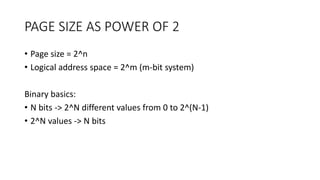

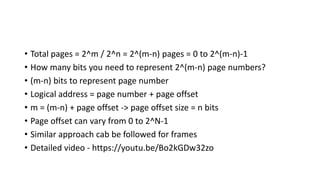

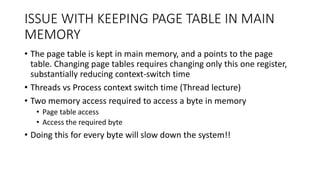

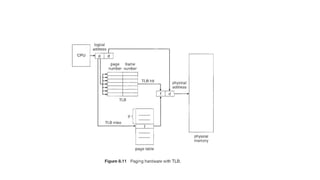

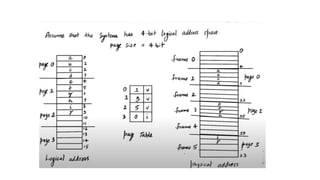

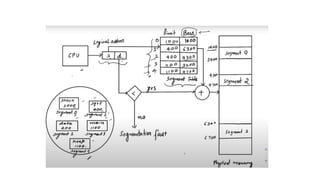

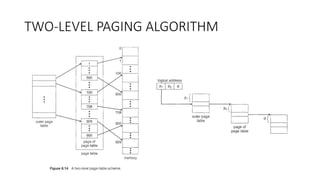

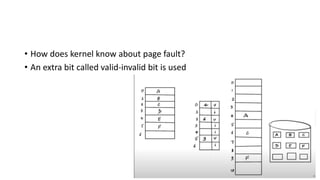

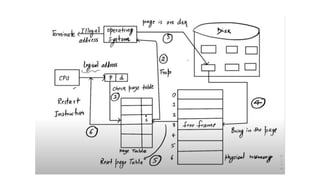

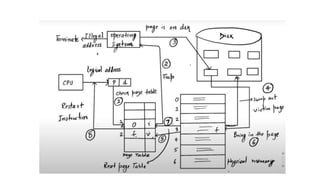

This document discusses memory management techniques in operating systems. It begins by covering contiguous memory allocation approaches like fixed and variable partitioning. It then discusses non-contiguous techniques like paging and segmentation. Key concepts covered include logical vs physical addresses, page tables, translation lookaside buffers, demand paging, and virtual memory. The document provides examples and links to detailed video explanations of these important OS memory management topics.