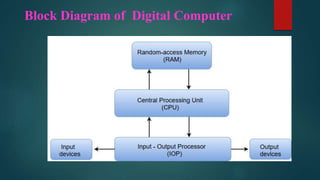

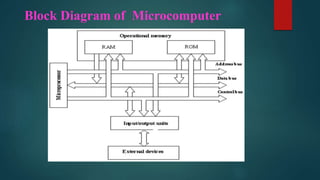

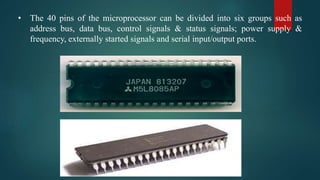

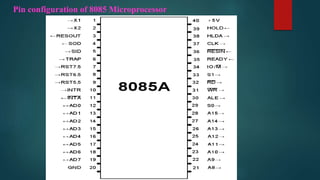

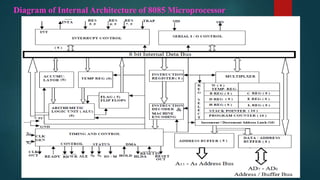

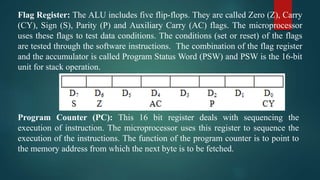

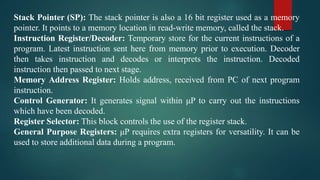

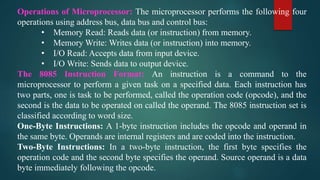

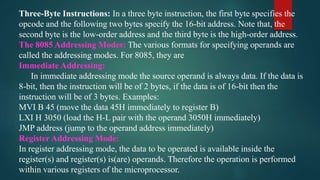

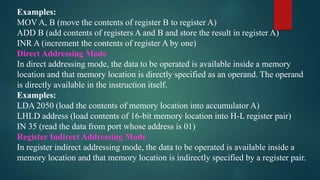

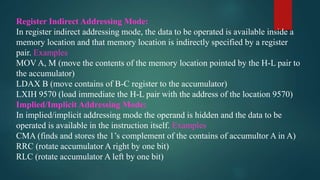

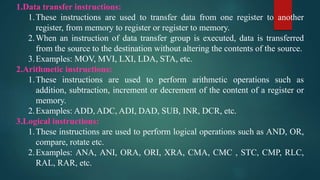

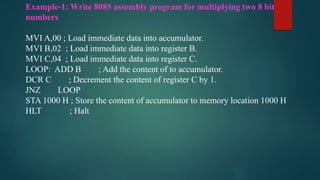

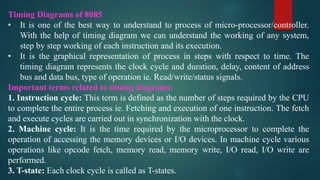

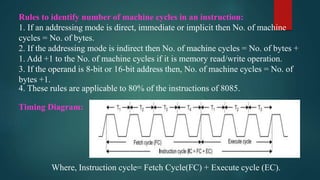

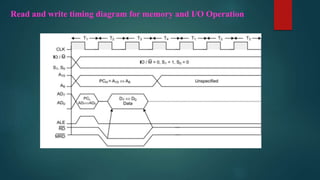

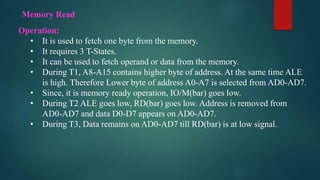

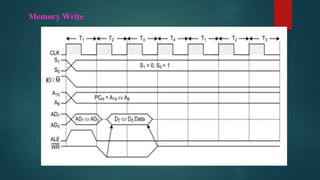

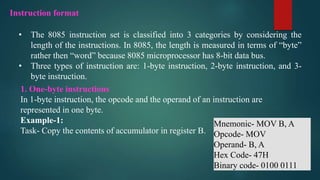

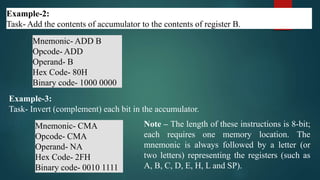

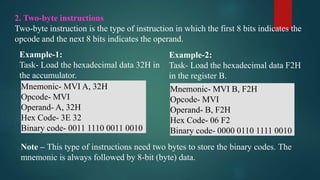

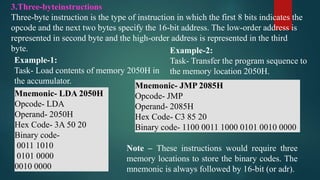

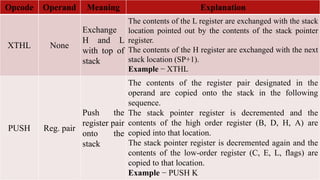

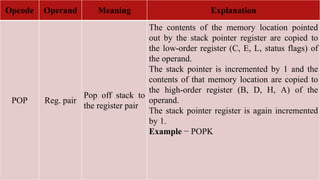

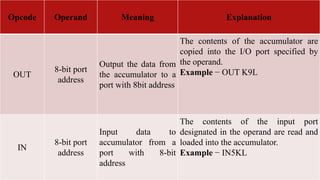

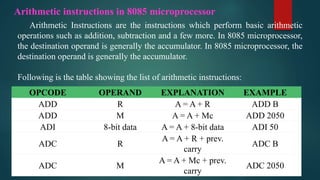

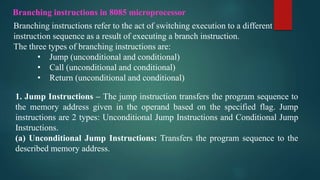

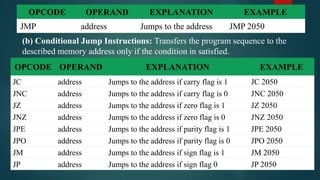

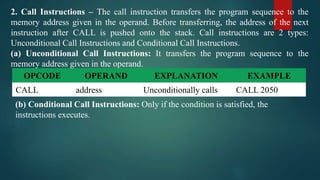

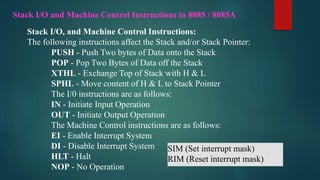

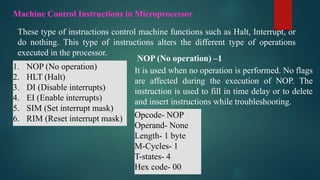

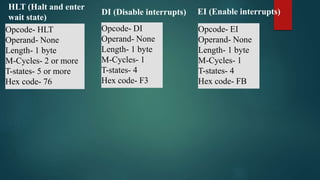

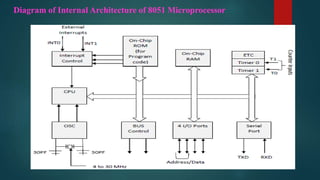

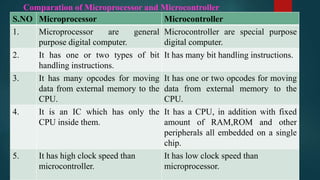

The document discusses the architecture and functioning of microprocessors, specifically focusing on the 8085 microprocessor and its components, including registers, buses, and control signals. It highlights the evolution of digital computers, explaining how microprocessors integrate various functionalities to form microcomputers that have shaped modern technology. Additionally, it details the operational principles and instruction formats associated with microprocessors, emphasizing their significance in electronic devices.