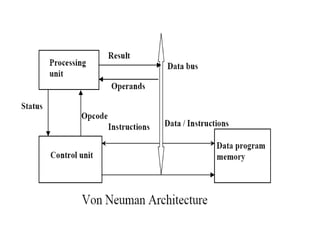

The document discusses microprocessors and microcontrollers. It defines a microprocessor as the central processing unit (CPU) of a microcomputer that is contained on a single silicon chip. A microcontroller is similarly integrated but also includes memory and input/output ports, making it self-contained to control a specific system. The document provides details on the components and architecture of microprocessors, including registers, buses, memory, and I/O devices. It also summarizes the characteristics of the Intel 8085 microprocessor.