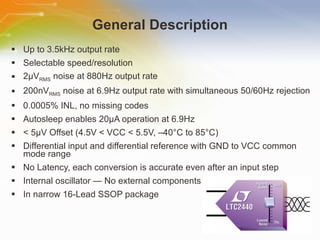

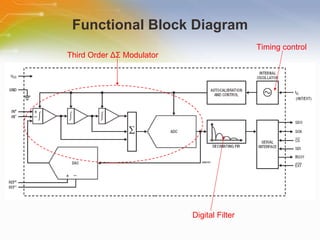

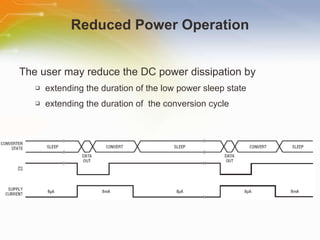

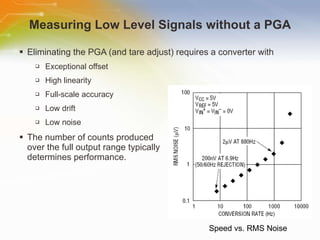

The LTC2440 is a high speed delta sigma analog to digital converter (ADC) from Linear Technology that offers programmable speed and resolution. It uses a third order delta sigma modulator and digital filter to provide conversion rates up to 3.5kHz with noise as low as 0.2uV. It has a differential input, integrated oscillator, low power sleep mode, and various serial interface options. The LTC2440 is suitable for applications such as high speed multiplexing, weight scales, data acquisition, and temperature measurement.