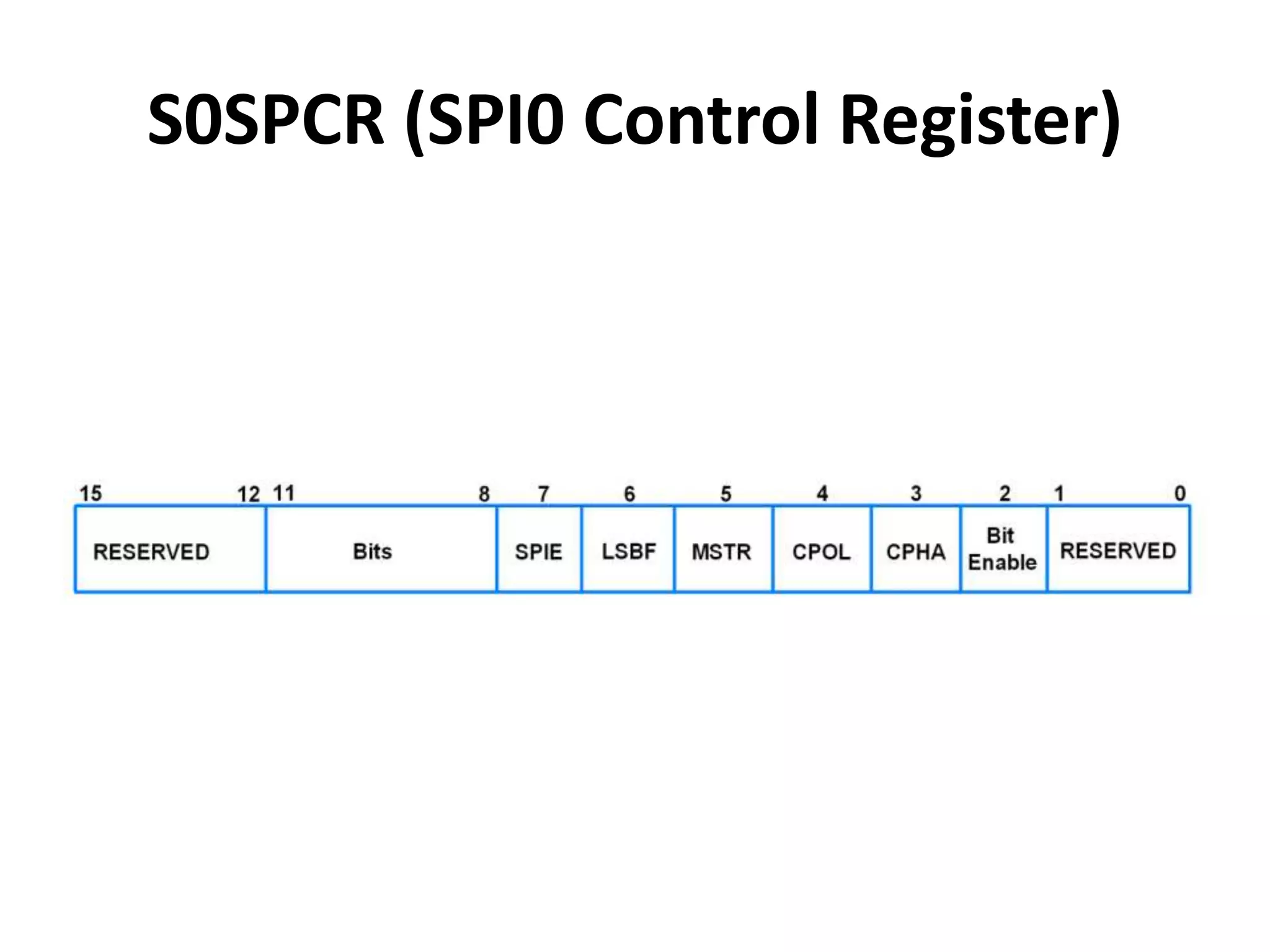

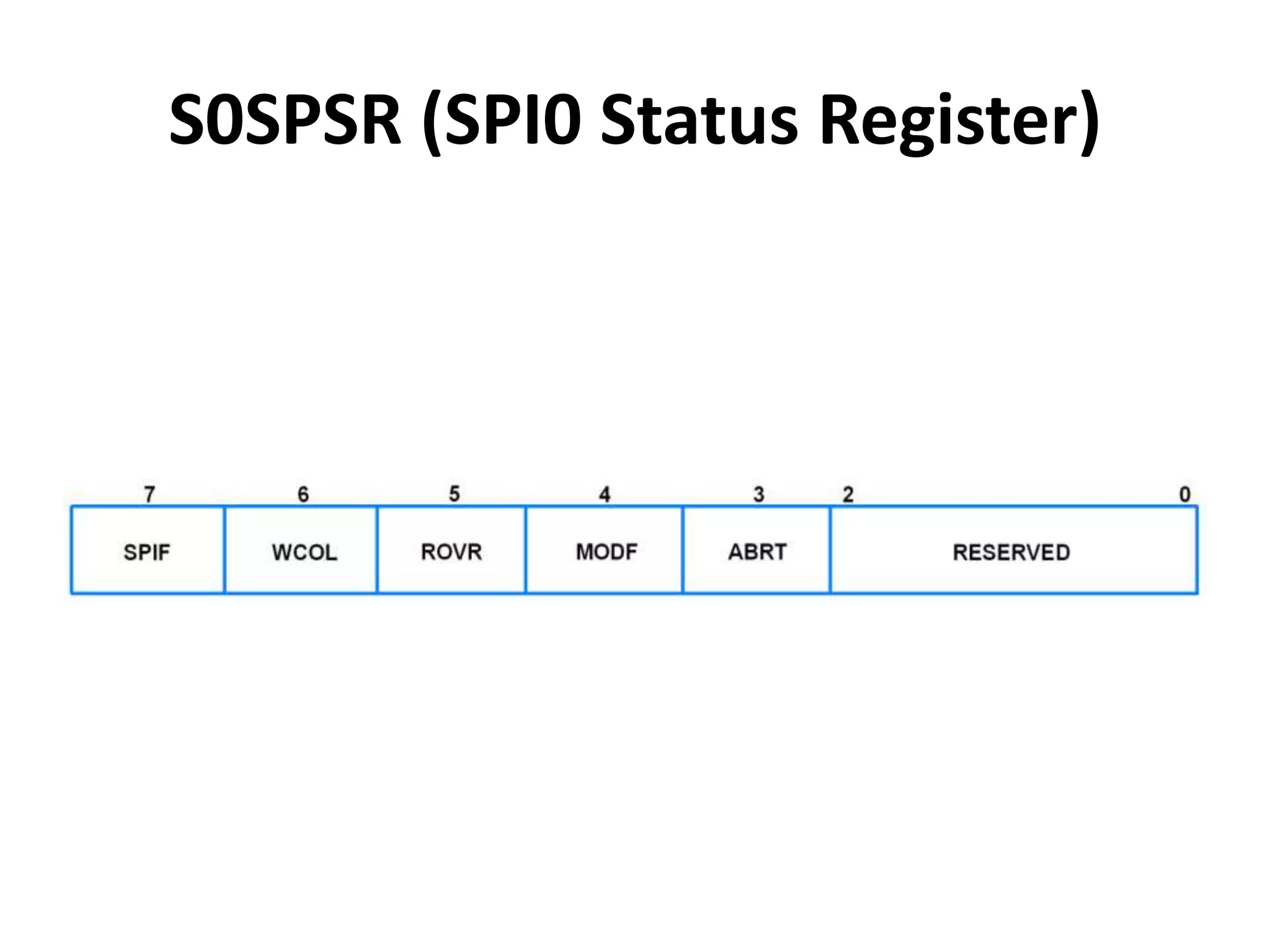

This document describes the SPI (Serial Peripheral Interface) protocol and its implementation on the LPC2148 microcontroller. It discusses the SPI control register (S0SPCR) which is used to configure the SPI block, the SPI status register (S0SPSR) which indicates status flags like aborts and overruns, and the SPI data register (S0SPDR) which is used to transmit and receive SPI data. The SPI enables full-duplex master-slave communication with a single master initiating communication and generating the clock.