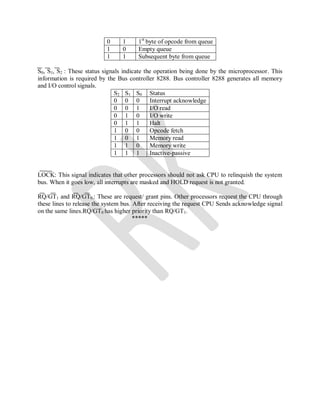

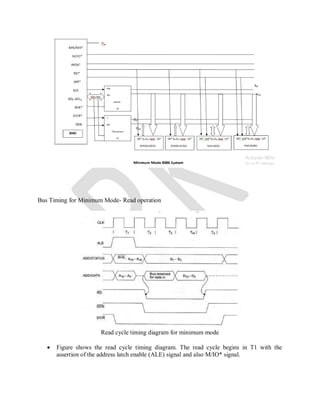

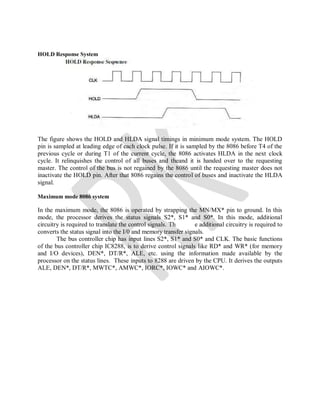

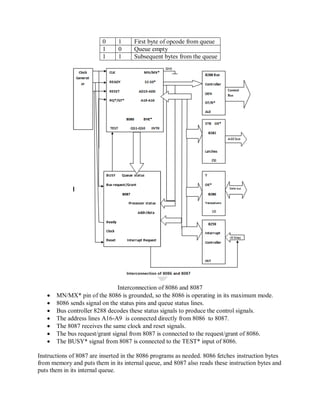

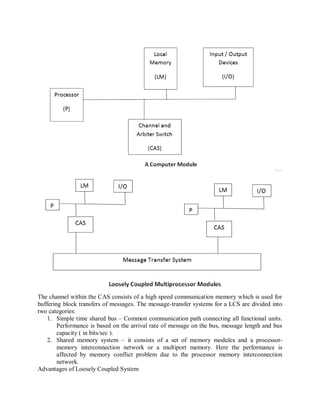

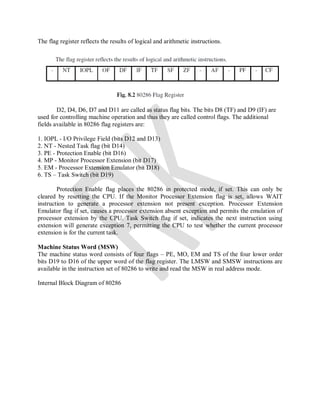

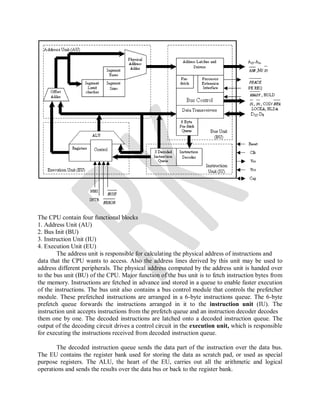

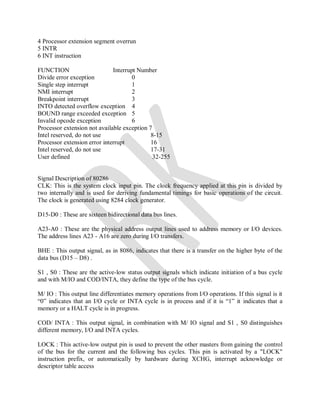

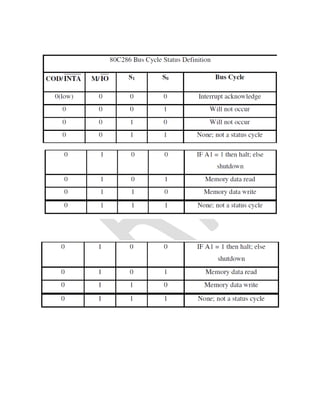

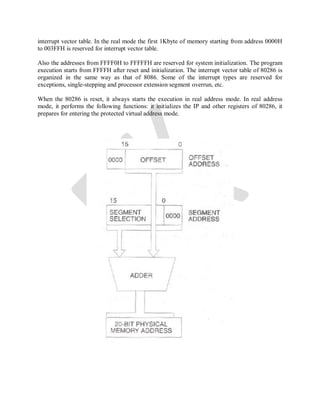

This document discusses the 8086 system bus structure. It begins by describing the basic configurations of minimum and maximum mode 8086 systems, including the system bus timing diagrams for read and write operations. It then discusses multiprocessor configurations using the 8086, including coprocessor configurations with the 8087 and closely/loosely coupled multiprocessor configurations. The document provides detailed information on the 8086 pin descriptions and signals in both minimum and maximum mode.