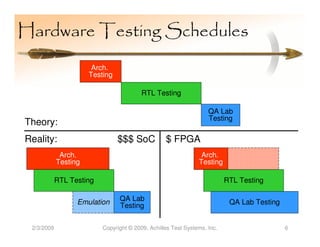

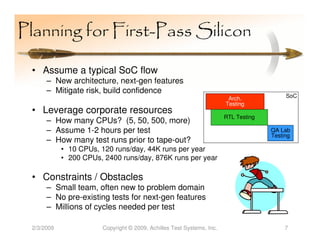

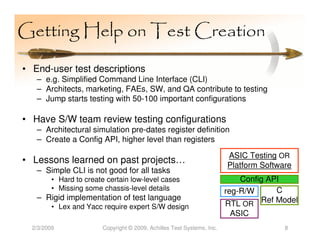

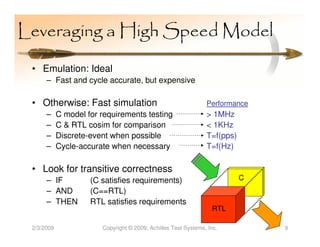

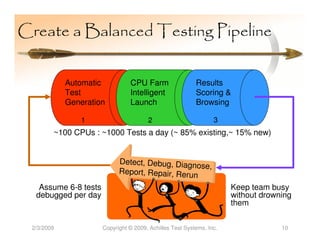

The document discusses lessons learned from 4 years of simulating an innovative network processor, emphasizing the need to leverage computing resources through automated testing, intelligent test generation, and storing large numbers of test executions and results in databases to methodically close issues. It provides recommendations for planning verification efforts and creating balanced testing pipelines to efficiently debug problems and keep verification teams productive.