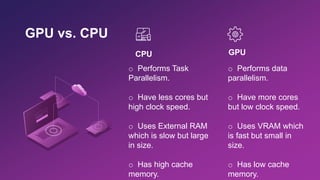

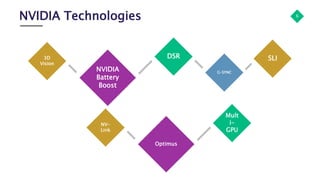

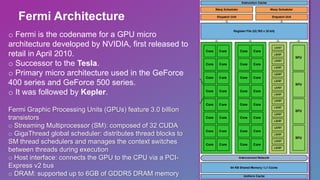

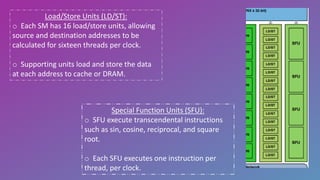

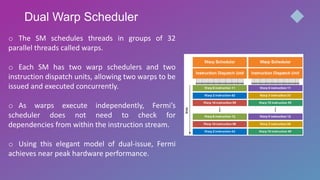

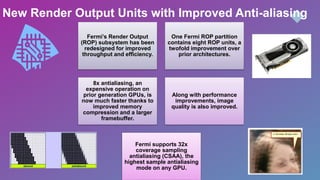

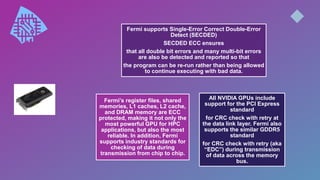

This document provides an overview of NVIDIA's GPU architecture, discussing the differences between GPUs and CPUs, as well as the detailed specifications of the Fermi microarchitecture. It highlights various components and innovations like the parallel thread execution, enhanced memory systems, and the usage of error-correcting code (ECC) for improved data integrity. Additionally, it emphasizes the performance capabilities and applications of GPUs in various fields such as gaming, scientific research, and medical imaging.